## (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**HO2M 5/293** (2006.01) **HO2M 1/00** (2007.01)

(52) CPC특허분류

**HO2M 5/2932** (2021.05) **HO2M 1/007** (2021.05)

(21) 출원번호 10-2021-0144639

(22) 출원일자 **2021년10월27일** 심사청구일자 **2021년10월27일**

(56) 선행기술조사문헌 US20150229227 A1 KR1020160027408 A (45) 공고일자 2022년10월17일

(11) 등록번호 10-2456093

(24) 등록일자 2022년10월13일

(73) 특허권자

#### 연세대학교 산학협력단

서울특별시 서대문구 연세로 50 (신촌동, 연세대 학교)

(72) 발명자

#### 박정욱

서울특별시 강남구 압구정로29길 71, 20동 701호 **칸 우스만 알리**

서울특별시 서대문구 연희로6길 21-11

#### 송민석

서울특별시 마포구 서강로16길 49, 302호

(74) 대리인

권성현, 유광철, 백두진, 강일신, 김정연

심사관: 윤시영

전체 청구항 수 : 총 13 항

(54) 발명의 명칭 캐스케이드 듀얼-벅 AC-AC 컨버터 제어 장치

#### (57) 요 약

본 발명의 컨버터 제어 장치는 캐스케이드 n개의 유닛이 연속적으로 연결된 캐스케이드 구조의 컨버터를 제어하는 캐스케이드 듀얼-벅 AC-AC 컨버터 제어 장치에 있어서, 상기 유닛에 포함된 복수의 스위치의 온/오프(on/of f)를 제어 신호에 기초하여 제어하는 제어부를 포함하고, 상기 캐스케이드 듀얼-벅 AC-AC 컨버터는 제1 유닛 내부와 제n 유닛의 내부에 각각 포함된 2개의 인덕터 및 상기 n개의 유닛 중 연속되는 2개의 유닛을 연결하는 n-1개의 인덕터를 포함할 수 있다.

#### 대 표 도 - 도2

# (52) CPC특허분류

Y02B 70/10 (2020.08)

이 발명을 지원한 국가연구개발사업

과제고유번호 1711130713 과제번호 2020R1A3B2079407 부처명 과학기술정보통신부

과제관리(전문)기관명 한국연구재단

연구사업명 개인기초연구(과기정통부)(R&D) 연구과제명 에너지 대전환 전력망 연구단

기 여 율 1/1

과제수행기관명 연세대학교

연구기간 2021.03.01 ~ 2022.02.28

공지예외적용 : 있음

#### 명세서

#### 청구범위

#### 청구항 1

n개(n은 2 이상의 자연수)의 유닛이 연속적으로 연결된 캐스케이드 구조의 컨버터를 제어하는 캐스케이드 듀얼-벅 AC-AC 컨버터 제어 장치에 있어서.

상기 유닛에 포함된 복수의 스위치의 온/오프(on/off)를 제어 신호에 기초하여 제어하는 제어부를 포함하고,

상기 캐스케이드 듀얼-벅 AC-AC 컨버터는 제1 유닛 내부와 제n 유닛의 내부에 각각 포함된 2개의 인덕터 및 상기 n개의 유닛 중 연속되는 2개의 유닛을 연결하는 n-1개의 인덕터를 포함하는

캐스케이드 듀얼-벅 AC-AC 컨버터 제어 장치.

#### 청구항 2

제1항에 있어서,

상기 제1 유닛은 제1 다이오드와 직렬로 연결된 제1 스위치, 제2 다이오드와 직렬로 연결된 제2 스위치, 제3 다이오드와 직렬로 연결된 제3 스위치 및 제4 다이오드와 직렬로 연결된 제4 스위치를 포함하는

캐스케이드 듀얼-벅 AC-AC 컨버터 제어 장치.

#### 청구항 3

제2항에 있어서,

상기 2개의 인덕터 중 상기 제1 유닛 내부에 포함된 인덕터는 상기 제1 스위치와 상기 제1 다이오드 사이의 제1 노드 및 상기 제2 스위치와 상기 제2 다이오드 사이의 제2 노드에 연결된

캐스케이드 듀얼-벅 AC-AC 컨버터 제어 장치.

#### 청구항 4

제3항에 있어서.

n이 2일 때, 상기 캐스케이드 듀얼-벅 AC-AC 컨버터는,

상기 제1 스위치와 대응되고 제5 다이오드와 직렬로 연결된 제5 스위치, 상기 제2 스위치와 대응되고 제6 다이오드와 직렬로 연결된 제6 스위치, 상기 제3 스위치와 대응되고 제7 다이오드와 직렬로 연결된 제7 스위치 및 상기 제4 스위치와 대응되고 제8 다이오드와 직렬로 연결된 제8 스위치를 포함하고, 상기 제1 유닛과 인덕터를 통해 연결되는 제2 유닛을 포함하고,

상기 2개의 인덕터 중 상기 제2 유닛 내부에 포함된 인덕터는 상기 제7 스위치와 상기 제7 다이오드 사이의 제3 노드 및 상기 제8 스위치와 상기 제8 다이오드 사이의 제4 노드에 연결된

캐스케이드 듀얼-벅 AC-AC 컨버터 제어 장치.

#### 청구항 5

제4항에 있어서,

상기 연속되는 2개의 유닛을 연결하는 인덕터는 상기 제3 스위치와 상기 제3 다이오드 사이의 제5 노드 및 상기

제6 스위치와 상기 제6 다이오드 사이의 제6 노드에 연결되거나, 상기 제4 스위치와 상기 제4 다이오드 사이의 제7 노드 및 상기 제5 스위치와 상기 제5 다이오드 사이의 제8 노드 사이에 연결된 캐스케이드 듀얼-벅 AC-AC 컨버터 제어 장치.

#### 청구항 6

제5항에 있어서,

상기 제4 노드에 연결된 필터링 커패시터 및 상기 제2 노드에 연결된 필터링 인덕터를 더 포함하는 캐스케이드 듀얼-벅 AC-AC 컨버터 제어 장치.

#### 청구항 7

제2항에 있어서.

상기 제1 다이오드, 상기 제2 스위치, 상기 제3 다이오드 및 상기 제4 스위치는 서로 하나의 노드에 연결된 캐스케이드 듀얼-벅 AC-AC 컨버터 제어 장치.

#### 청구항 8

제4항에 있어서,

상기 제5 다이오드, 상기 제6 스위치, 상기 제7 다이오드 및 상기 제8 스위치는 서로 하나의 노드에 연결된 캐스케이드 듀얼-벅 AC-AC 컨버터 제어 장치.

### 청구항 9

제1항에 있어서,

상기 제1 유닛 내부와 제n 유닛의 내부에 각각 포함된 2개의 인덕터의 임피던스 및 상기 n개의 유닛 중 연속되는 2개의 유닛을 연결하는 n-1개의 인덕터의 임피던스는 동일한

캐스케이드 듀얼-벅 AC-AC 컨버터 제어 장치.

#### 청구항 10

제4항에 있어서,

상기 제어부는,

상기 제1 스위치 및 상기 제3 스위치의 온/오프를 제1 제어 신호에 의해 제어하고,

상기 제2 스위치 및 상기 제4 스위치의 온/오프를 상기 제1 제어 신호를 반전한 제2 제어 신호에 의해 제어하고,

상기 제5 스위치 및 상기 제7 스위치의 온/오프를 제3 제어 신호에 의해 제어하고,

상기 제6 스위치 및 상기 제8 스위치의 온/오프를 상기 제3 제어 신호를 반전한 제4 제어 신호에 의해 제어하는 캐스케이드 듀얼-벅 AC-AC 컨버터 제어 장치.

#### 청구항 11

제10항에 있어서,

상기 제3 제어 신호는 상기 제1 제어 신호에서 180도 위상 천이된 신호인 캐스케이드 듀얼-벅 AC-AC 컨버터 제어 장치.

#### 청구항 12

제4항에 있어서,

상기 제어부는.

상기 제1 스위치, 상기 제3 스위치, 상기 제5 스위치 및 상기 제7 스위치가 온 상태이고, 상기 제2 스위치, 상기 제4 스위치, 상기 제6 스위치 및 상기 제8 스위치가 오프 상태인 경우를 제1 모드로 설정하고,

상기 제1 스위치, 상기 제3 스위치, 상기 제6 스위치 및 상기 제8 스위치가 온 상태이고, 상기 제2 스위치, 상기 제4 스위치, 상기 제5 스위치 및 상기 제7 스위치가 오프 상태인 경우를 제2 모드로 설정하고,

상기 제2 스위치, 상기 제4 스위치, 상기 제5 스위치 및 상기 제7 스위치가 온 상태이고, 상기 제1 스위치, 상기 제3 스위치, 상기 제6 스위치 및 상기 제8 스위치가 오프 상태인 경우를 제3 모드로 설정하고,

상기 제1 모드, 상기 제2 모드, 상기 제1 모드, 상기 제3 모드 및 다시 상기 제1 모드가 순차적으로 반복되도록 상기 제어 신호를 생성하는

캐스케이드 듀얼-벅 AC-AC 컨버터 제어 장치.

#### 청구항 13

제1항에 있어서,

상기 캐스케이드 듀얼-벅 AC-AC 컨버터에 포함된 인덕터의 개수는 필터링 인덕터를 제외하고 (n+1)개인 캐스케이드 듀얼-벅 AC-AC 컨버터 제어 장치.

#### 발명의 설명

#### 기술분야

[0001] 본 발명은 컨버터 제어 장치에 관한 것으로, 보다 상세하게는, 캐스케이드 컨버터에 포함된 인덕터의 개수를 줄일 수 있는 구성 및 제어에 관한 것이다.

#### 배경기술

- [0002] 다양한 분야에서 출력 전압을 승압 및 강압할 수 있는 듀얼-벅 AC-AC 컨버터에 대한 연구가 활발히 진행되고 있다. 그 중 단락 및 개방 회로 문제로 인한 정류 문제를 해결하기 위해 많은 토폴로지가 제안되었다.

- [0003] 그러나, 종래의 캐스케이드 컨버터는 연결되는 유닛이 많아질수록 인덕터의 개수도 많아지므로, 레이아웃 복잡성, 비용 및 자기 부피가 증가하는 문제가 초래된다. 따라서, 캐스케이드 연결을 하더라도, 위와 같은 문제를 최소화할 수 있는 캐스케이드 컨버터 구조가 필요하다.

#### 발명의 내용

#### 해결하려는 과제

- [0004] 본 발명의 일 과제는 인덕터의 개수를 줄일 수 있는 캐스케이드 컨버터에 관한 것이다.

- [0005] 본 발명의 일 과제는 위상 천이 제어를 통해 인덕터 전류 리플을 줄일 수 있는 컨버터 제어 장치에 관한

것이다.

#### 과제의 해결 수단

- [0006] 일 실시예에 따른 캐스케이드 듀얼-벅 AC-AC 컨버터 제어 장치는 n개의 유닛이 연속적으로 연결된 캐스케이드 구조의 컨버터를 제어하는 캐스케이드 듀얼-벅 AC-AC 컨버터 제어 장치에 있어서, 상기 유닛에 포함된 복수의 스위치의 온/오프(on/off)를 제어 신호에 기초하여 제어하는 제어부를 포함하고, 상기 캐스케이드 듀얼-벅 AC-AC 컨버터는 제1 유닛 내부와 제n 유닛의 내부에 각각 포함된 2개의 인덕터 및 상기 n개의 유닛 중 연속되는 2 개의 유닛을 연결하는 n-1개의 인덕터를 포함할 수 있다.

- [0007] 여기서, 상기 제1 유닛은 제1 다이오드와 직렬로 연결된 제1 스위치, 제2 다이오드와 직렬로 연결된 제2 스위치, 제3 다이오드와 직렬로 연결된 제3 스위치 및 제4 다이오드와 직렬로 연결된 제4 스위치를 포함할 수 있다.

- [0008] 여기서, 상기 2개의 인덕터 중 상기 제1 유닛 내부에 포함된 인덕터는 상기 제1 스위치와 상기 제1 다이오드 사이의 제1 노드 및 상기 제2 스위치와 상기 제2 다이오드 사이의 제2 노드에 연결될 수 있다.

- [0009] 여기서, n이 2일 때, 상기 캐스케이드 듀얼-벅 AC-AC 컨버터는, 상기 제1 스위치와 대응되고 제5 다이오드와 직렬로 연결된 제5 스위치, 상기 제2 스위치와 대응되고 제6 다이오드와 직렬로 연결된 제6 스위치, 상기 제3 스위치와 대응되고 제7 다이오드와 직렬로 연결된 제7 스위치 및 상기 제4 스위치와 대응되고 제8 다이오드와 직렬로 연결된 제8 스위치를 포함하고, 상기 제1 유닛과 인덕터를 통해 연결되는 제2 유닛을 포함하고, 상기 2개의 인덕터 중 상기 제2 유닛 내부에 포함된 인덕터는 상기 제7 스위치와 상기 제7 다이오드 사이의 제3 노드 및 상기 제8 스위치와 상기 제8 다이오드 사이의 제4 노드에 연결될 수 있다.

- [0010] 여기서, 상기 연속되는 2개의 유닛을 연결하는 인덕터는 상기 제3 스위치와 상기 제3 다이오드 사이의 제5 노드 및 상기 제6 스위치와 상기 제6 다이오드 사이의 제6 노드에 연결되거나, 상기 제4 스위치와 상기 제4 다이오드 사이의 제7 노드 및 상기 제5 스위치와 상기 제5 다이오드 사이의 제8 노드 사이에 연결될 수 있다.

- [0011] 여기서, 상기 제4 노드에 연결된 필터링 커패시터 및 상기 제2 노드에 연결된 필터링 인덕터를 더 포함할 수 있다.

- [0012] 여기서, 상기 제1 스위치, 상기 제2 다이오드, 상기 제3 스위치 및 상기 제4 다이오드는 서로 병렬로 연결되고, 상기 제1 다이오드, 상기 제2 스위치, 상기 제3 다이오드 및 상기 제4 스위치는 서로 병렬로 연결될 수 있다.

- [0013] 여기서, 상기 제5 스위치, 상기 제6 다이오드, 상기 제7 스위치 및 상기 제8 다이오드는 서로 병렬로 연결되고, 상기 제5 다이오드, 상기 제6 스위치, 상기 제7 다이오드 및 상기 제8 스위치는 서로 병렬로 연결될 수 있다.

- [0014] 여기서, 상기 제1 유닛 내부와 제n 유닛의 내부에 각각 포함된 2개의 인덕터의 임피던스 및 상기 n개의 유닛 중연속되는 2개의 유닛을 연결하는 n-1개의 인덕터의 임피던스는 동일할 수 있다.

- [0015] 여기서, 상기 제어부는, 상기 제1 스위치 및 상기 제3 스위치의 온/오프를 제1 제어 신호에 의해 제어하고, 상기 제2 스위치 및 상기 제4 스위치의 온/오프를 상기 제1 제어 신호를 반전한 제2 제어 신호에 의해 제어하고, 상기 제5 스위치 및 상기 제7 스위치의 온/오프를 제3 제어 신호에 의해 제어하고, 상기 제6 스위치 및 상기 제8 스위치의 온/오프를 상기 제3 제어 신호를 반전한 제4 제어 신호에 의해 제어할 수 있다.

- [0016] 여기서, 상기 제3 제어 신호는 상기 제1 제어 신호에서 180도 위상 천이된 신호일 수 있다.

- [0017] 여기서, 상기 제어부는, 상기 제1 스위치, 상기 제3 스위치, 상기 제5 스위치 및 상기 제7 스위치가 온 상태이고, 상기 제2 스위치, 상기 제4 스위치, 상기 제6 스위치 및 상기 제8 스위치가 오프 상태인 경우를 제1 모드로 설정하고, 상기 제1 스위치, 상기 제3 스위치, 상기 제6 스위치 및 상기 제8 스위치가 온 상태이고, 상기 제2 스위치, 상기 제4 스위치, 상기 제5 스위치 및 상기 제7 스위치가 오프 상태인 경우를 제2 모드로 설정하고, 상기 제2 스위치, 상기 제4 스위치, 상기 제5 스위치 및 상기 제7 스위치가 온 상태이고, 상기 제1 스위치, 상기 제3 스위치, 상기 제6 스위치 및 상기 제8 스위치가 오프 상태인 경우를 제3 모드로 설정하고, 상기 제3 모드, 상기 제2 모드, 상기 제1 모드, 상기 제3 모드 및 다시 상기 제1 모드가 순차적으로 반복되도록 상기 제어 신호를 생성할 수 있다.

- [0018] 여기서, 상기 캐스케이드 듀얼-벅 AC-AC 컨버터에 포함된 인덕터의 개수는 필터링 인덕터를 제외하고 (n+1)개일 수 있다.

#### 발명의 효과

- [0019] 본 발명의 일 실시예에 따르면 인덕터의 개수가 종래보다 줄어든 캐스케이드 컨버터가 제공될 수 있다.

- [0020] 본 발명의 일 실시예에 따르면 위상 천이 제어를 통해 인덕터 전류 리플을 감소하는 컨버터 제어 장치가 제공될 수 있다.

#### 도면의 간단한 설명

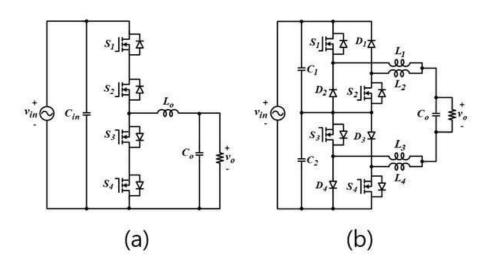

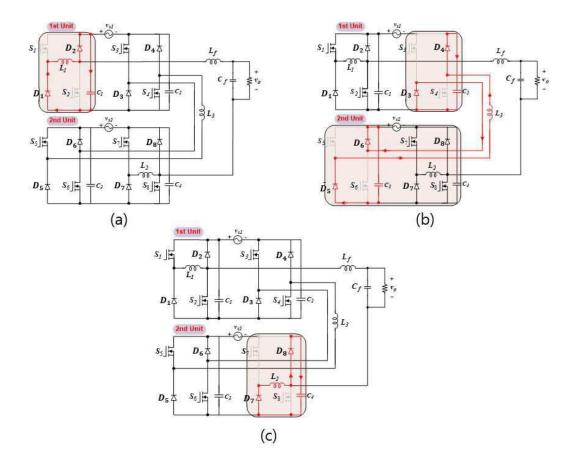

[0021] 도 1은 종래의 벅 타입 AC-AC 컨버터를 나타낸 회로도이다.

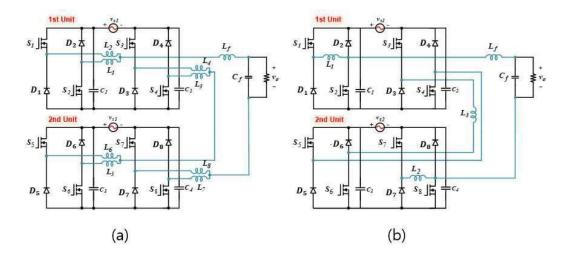

도 2는 종래의 캐스케이드 AC-AC 컨버터와 본원 발명의 일 실시예에 따른 캐스케이드 AC-AC 컨버터를 나타낸 회로도이다.

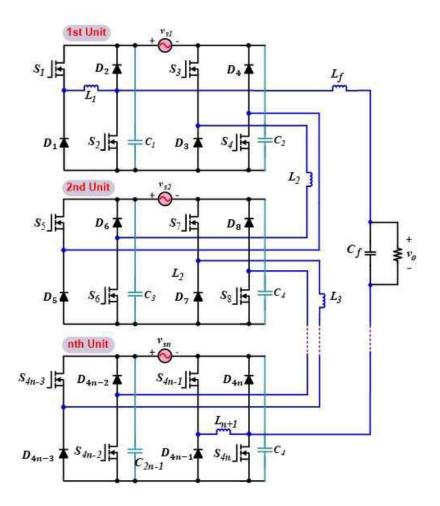

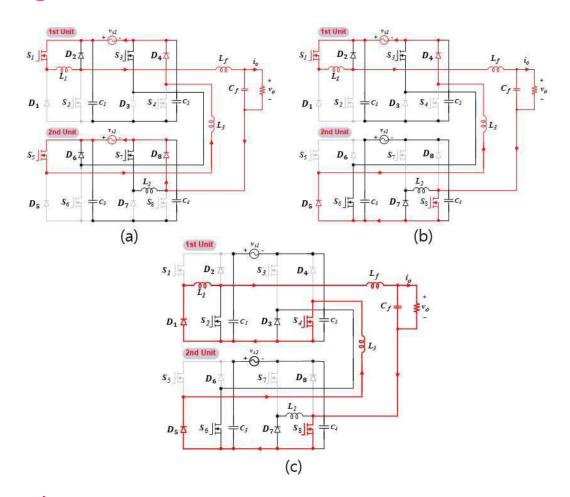

도 3은 본원 발명의 일 실시예에 따른 n개의 유닛이 연결된 캐스케이드 AC-AC 컨버터의 회로도이다.

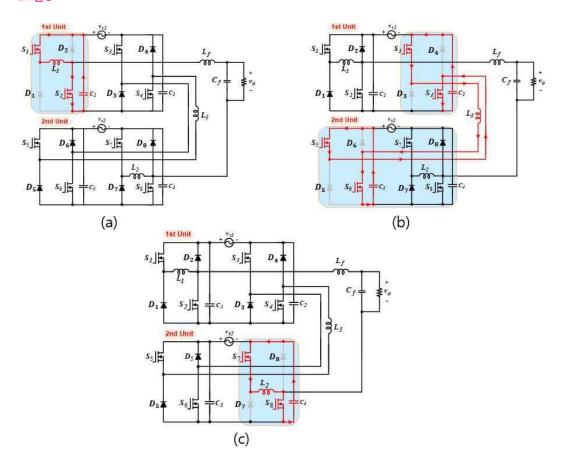

도 4는 일 실시예에 따른 캐스케이드 AC-AC 컨버터의 스위치 간의 중첩 시간 동안의 전류 흐름을 나타낸 회로도이다.

도 5는 일 실시예에 따른 캐스케이드 AC-AC 컨버터의 스위치 간의 데드 타임 동안의 전류 흐름을 나타낸 회로도이다.

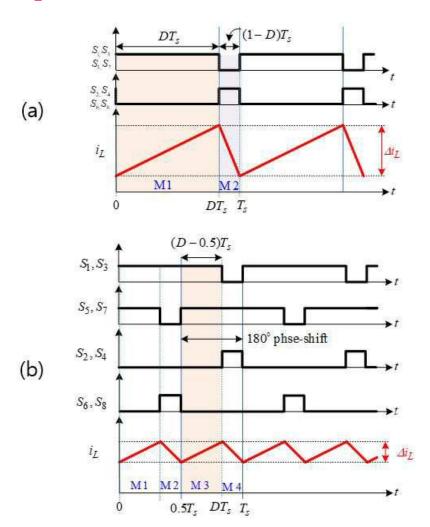

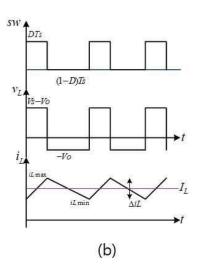

도 6은 위상 천이 제어가 없는 경우와 위상 천이 제어가 있는 경우의 게이트 신호와 인덕터 전류 리플을 비교한 도면이다.

도 7은 위상 천이 제어가 없는 경우, 컨버터의 모드에 따른 회로를 나타낸 도면이다.

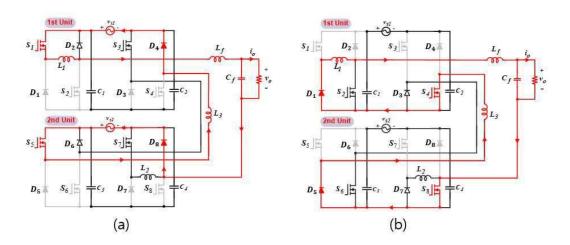

도 8은 위상 천이 제어가 있는 경우, 컨버터의 모드에 따른 회로를 나타낸 도면이다.

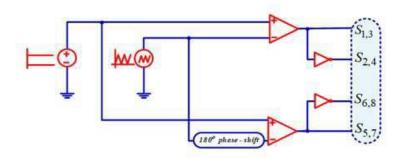

도 9는 일 실시예에 따른 제어 신호 입력을 위한 블록 다이어그램을 나타낸 도면이다.

도 10은 인덕터의 전압-시간 평형 조건을 나타낸 도면이다.

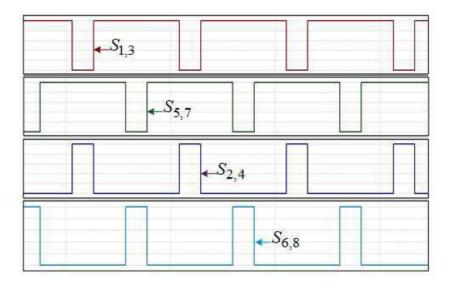

도 11은 위상 천이 제어가 있는 캐스케이드 컨버터의 스위칭 신호를 나타낸 도면이다.

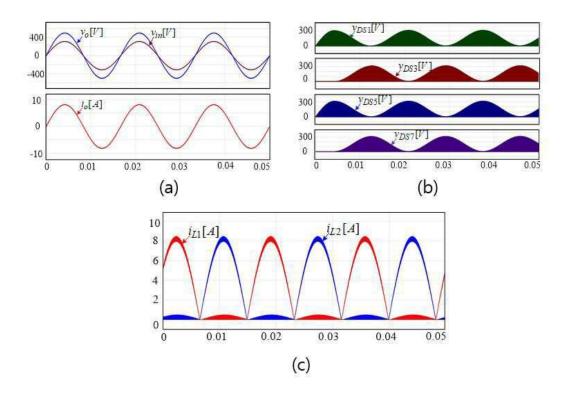

도 12는 위상 천이 제어가 없는 2-유닛 캐스케이드 컨버터의 시뮬레이션 파형을 나타낸 도면이다.

도 13은 본원 발명의 일 실시예에 따른 위상 천이 제어가 있는 2-유닛 캐스케이드 컨버터의 시뮬레이션 파형을 나타낸 도면이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0022] 본 명세서에 기재된 실시예는 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에게 본 발명의 사상을 명확히 설명하기 위한 것이므로, 본 발명이 본 명세서에 기재된 실시예에 한정되는 것은 아니며, 본 발명의 범위는 본 발명의 사상을 벗어나지 아니하는 수정예 또는 변형예를 포함하는 것으로 해석되어야 한다.

- [0023] 본 명세서에서 사용되는 용어는 본 발명에서의 기능을 고려하여 가능한 현재 널리 사용되고 있는 일반적인 용어를 선택하였으나 이는 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자의 의도, 판례 또는 새로운 기술의 출현 등에 따라 달라질 수 있다. 다만, 이와 달리 특정한 용어를 임의의 의미로 정의하여 사용하는 경우에는 그 용어의 의미에 관하여 별도로 기재할 것이다. 따라서 본 명세서에서 사용되는 용어는 단순한 용어의 명칭이 아닌 그 용어가 가진 실질적인 의미와 본 명세서의 전반에 걸친 내용을 토대로 해석되어야 한다.

- [0024] 본 명세서에 첨부된 도면은 본 발명을 용이하게 설명하기 위한 것으로 도면에 도시된 형상은 본 발명의 이해를 돕기 위하여 필요에 따라 과장되어 표시된 것일 수 있으므로 본 발명이 도면에 의해 한정되는 것은 아니다.

- [0025] 본 명세서에서 본 발명에 관련된 공지의 구성 또는 기능에 대한 구체적인 설명이 본 발명의 요지를 흐릴 수 있다고 판단되는 경우에 이에 관한 자세한 설명은 필요에 따라 생략하기로 한다.

- [0027] 도 1은 종래의 벅 타입 AC-AC 컨버터를 나타낸 회로도이다.

- [0028] 도 1(a)는 종래의 AC-AC 벅 컨버터의 회로도이고, 도 1(b)는 듀얼-벅 유형 AC-AC 컨버터의 회로도이다.

- [0029] 도 1(a)의 벅 타입 AC-AC 컨버터는 구조가 간단하고 강압 기능이 있다. 그러나, 입력 전압보다 큰 출력 전압을

생성하는 부스트 기능이 없다. 그리고, 해당 구조는 단락 및 개방 회로 문제로 인해 정류 문제가 있어서, 실용 화될 수 없다.

- [0030] 정류 문제를 해결하기 위해 새로운 유형의 직접적인 PWM AC-AC 컨버터가 연구되었고, 도 1(b)의 듀얼-벅 유형 AC-AC 컨버터가 그 중 하나이다. 해당 구조는 정류 문제가 없으며, 바디 다이오드의 역 회복 문제없이 모스펫을 사용할 수 있다. 또한, 손실 스너버 회로가 필요하지 않으며, 데드 타임 없이 동작할 수 있다.

- [0031] 직접적인 AC-AC 전력 변환을 위해 플라잉 커패시터와 캐스케이드 멀티 레벨 컨버터가 개발되었다. 그 중 하나가 도 2(a)의 캐스케이드 구조이고, 해당 구조는 도 1(b)의 컨버터를 기반으로 한 것이다.

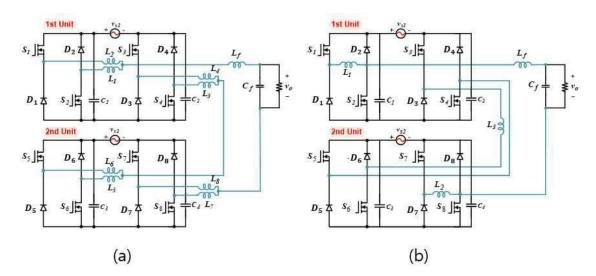

- [0033] 도 2는 종래의 캐스케이드 AC-AC 컨버터와 본원 발명의 일 실시예에 따른 캐스케이드 AC-AC 컨버터를 나타낸 회로도이다.

- [0034] 도 2(a)는 종래의 캐스케이드 AC-AC 컨버터의 회로도이고, 도 2(b)는 본원 발명의 일 실시예에 따른 캐스케이드 AC-AC 컨버터의 회로도이다.

- [0035] 도 2(a)의 컨버터는 도 1(b)를 기반으로 한 기존의 캐스케이드 듀얼-벅 AC-AC 컨버터로서, 도 1(b)의 장점을 모두 가지고 있다. 또한, 입력 전압보다 더 높은 출력 전압을 얻을 수 있다.

- [0036] 그러나, 도 1(b)를 기반으로 한 캐스케이드 듀얼-벅 AC-AC 컨버터는 각 캐스케이드 유닛에 대해 4개의 슛-스루 제한 인덕터가 필요하다. 따라서, n개의 캐스케이드 유닛이 연결되었다면 슛-스루 제한 인덕터는 4n개가 필요하다.

- [0037] 많은 수의 슛-스루 제한 인덕터가 필요하기 때문에, 이는 컨버터의 볼륨, 비용, 납땜 연결 및 회로 레이아웃의 복잡성을 증가시키고, 전력 밀도를 감소시키는 문제를 초래한다.

- [0038] 따라서, 본원 발명은 기존의 캐스케이드 듀얼-벅 AC-AC 컨버터보다 더 적은 수의 인덕터를 사용하는 개선된 캐스케이드 듀얼-벅 AC-AC를 제안한다. 본원 발명의 컨버터는 복잡한 제어 또는 하드웨어가 필요하지 않으므로, 기존 AC-AC 컨버터의 큰 볼륨 및 많은 수의 인덕터로 초래되는 문제들을 효과적으로 개선할 수 있다.

- [0039] 본원 발명의 컨버터는 더 높은 스위칭 주파수에서 동작할 수 있다. 또한, 종래보다 더 적은 수의 인덕터를 필요로 하므로, 전체 자기 볼륨, 비용 및 복잡한 회로 배열을 줄일 수 있다. 게다가, 본원 발명의 컨버터는 수동 소자의 부피를 줄이기 위해 위상 천이 제어로 동작할 수 있다. 위상 천이 제어에 대한 내용은 이하에서 도 5를 참조하여 자세히 설명한다.

- [0040] 본원 발명의 컨버터에 포함된 스위치의 전압 스트레스는 입력 전압 Vin일 수 있다. 본원 발명의 컨버터의 각 레그에서 단일 스위치와 외부 고속 회복 다이오드가 직렬로 연결될 수 있다. 따라서, 본원 발명의 컨버터는 슛-스루 문제를 제거할 수 있고, 모스펫 바디 다이오드의 역 회복 문제없이 전력 모스펫으로 구현할 수 있다.

- [0041] 본원 발명의 캐스케이드 컨버터는 n개의 캐스케이드 유닛을 포함할 수 있다. 도 2(b)는 2개의 캐스케이드 유닛을 포함하는 캐스케이드 컨버터를 도시한 도면이다. 이때 n은 자연수로서 본원 발명의 캐스케이드 컨버터는 n에 따라 다양해질 수 있으며, n이 2인 도 2(b)에 한정되지 않는다.

- [0042] 일 실시예에 따르면, 캐스케이드 컨버터는 제1 유닛 및 제2 유닛을 포함할 수 있다. 이때 제1 유닛 및 제2 유닛 은 동일한 회로 구성을 가진 회로단일 수 있다.

- [0043] 제1 유닛은 제1 다이오드(D1)와 직렬로 연결된 제1 스위치(S1), 제2 다이오드(D2)와 직렬로 연결된 제2 스위치(S2), 제3 다이오드(D3)와 직렬로 연결된 제3 스위치(S3) 및 제4 다이오드(D4)와 직렬로 연결된 제4 스위치(S4)를 포함할 수 있다.

- [0044] 제2 유닛은 제5 다이오드(D5)와 직렬로 연결된 제5 스위치(S5), 제6 다이오드(D6)와 직렬로 연결된 제6 스위치(S6), 제7 다이오드(D7)와 직렬로 연결된 제7 스위치(S7) 및 제8 다이오드(D8)와 직렬로 연결된 제8 스위치(S8)를 포함할 수 있다.

- [0045] 이때, 제1 유닛 및 제2 유닛은 동일한 회로 구성을 갖기 때문에, 제1 스위치(S1)는 제5 스위치(S2)와 대응되고, 제2 스위치(S2)는 제6 스위치(S6)와 대응되고, 제3 스위치(S3)는 제7 스위치(S7)와 대응되고, 제8 스위치(S8)는 제8 스위치(S8)와 대응될 수 있다.

- [0046] 또한, 제1 다이오드(D1)는 제5 다이오드(D5)와 대응되고, 제2 다이오드(D2)는 제6 다이오드(D6)와 대응되고, 제 3 다이오드(D3)는 제7 다이오드(D7)와 대응되고, 제4 다이오드(D4)는 제8 다이오드(D8)와 대응될 수 있다.

- [0047] 이때, 제1 내지 제8 다이오드(D1 내지 D8)는 외부 고속 회복 전류 프리휠링 다이오드일 수 있다. 또한, 컨버터에 포함된 커패시터(C1 내지 C4)는 데드 타임 동안 인덕터 전류에 대해 경로를 제공하는 스너버 역할을 할 수 있다.

- [0048] 본원 발명의 컨버터는 제1 스위치(S1) 및 제1 다이오드(D1) 사이의 마디(노드)와 제2 스위치(S2) 및 제2 다이오드(D2) 사이의 마디에 연결된 제1 인덕터(L1)를 포함할 수 있다.

- [0049] 또한, 본원 발명의 컨버터는 제7 스위치(S2) 및 제7 다이오드(D7) 사이의 마디와 제8 스위치(S8) 및 제8 다이오드(D8) 사이의 마디에 연결된 제2 인덕터(L2)를 포함할 수 있다.

- [0050] 또한, 본원 발명의 컨버터는 제3 스위치(S3) 및 제3 다이오드(D3) 사이의 마디 및 제6 스위치(S6) 및 제6 다이오드(D6) 사이의 마디에 연결된 제3 인덕터(L3)를 포함할 수 있다. 또는 이때, 제3 인덕터(L3)는 제4 스위치(S3) 및 제4 다이오드(D4) 사이의 마디 및 제5 스위치(S5) 및 제5 다이오드(D5) 사이의 마디에 연결될 수도 있다.

- [0051] 도 2(a)를 참조하면, 종래의 캐스케이드 컨버터는 필터링 인덕터(Lf)를 제외하고, L1 내지 L8의 8개의 인덕터를 포함하였다. 즉, 종래의 n개의 유닛이 연결된 캐스케이드 컨버터는 4n개의 인덕터를 포함하였다.

- [0052] 그러나, 도 2(b)를 참조하면, 본원 발명의 캐스케이드 컨버터는 필터링 인덕터(Lf)를 제외하고 L1 내지 L3의 3 개의 인덕터를 포함하고 있다. 즉, 본원 발명의 캐스케이드 컨버터가 n개의 캐스케이드 유닛을 포함할 경우, n+1개의 인덕터를 포함하게 된다. 따라서, 종래의 캐스케이드 컨버터보다 인덕터의 개수가 3n-1개가 더 줄어들게 될 수 있다.

- [0053] 예를 들어, n이 3인 경우, 종래의 컨버터는 12개의 인덕터를 포함하고, 본원 발명의 컨버터는 4개의 인덕터를 포함하게 된다. 따라서, 본원 발명의 컨버터는 종래의 컨버터보다 인덕터의 개수를 8개 줄일 수 있다.

- [0054] 또한, n이 4인 경우, 종래의 컨버터는 16개의 인덕터를 포함하고, 본원 발명의 컨버터는 5개의 인덕터를 포함하 게 된다. 따라서, 본원 발명의 컨버터는 종래의 컨버터보다 인덕터의 개수를 11개 줄일 수 있다.

- [0055] 또한, n이 5인 경우, 종래의 컨버터는 20개의 인덕터를 포함하고, 본원 발명의 컨버터는 6개의 인덕터를 포함하 게 된다. 따라서, 본원 발명의 컨버터는 종래의 컨버터보다 인덕터의 개수를 14개 줄일 수 있다.

- [0057] 도 3은 본원 발명의 일 실시예에 따른 n개의 유닛이 연결된 캐스케이드 AC-AC 컨버터의 회로도이다.

- [0058] 도 3을 참조하면, n개의 유닛이 연결된 캐스케이드 AC-AC 컨버터는 제1 유닛의 내부에 포함된 제1 인덕터(L1) 및 제n 유닛의 내부에 포함된 제(n+1) 인덕터(L\_(n+1))를 포함할 수 있다. 또한, 컨버터는 연속되는 2개의 유닛을 연결하는 n-1개의 인덕터를 포함할 수 있다.

- [0059] 즉, 본원 발명의 캐스케이드 AC-AC 컨버터는 첫번째 유닛과 마지막 유닛의 내부에 연결된 2개의 인덕터를 포함 하고, 연속되는 유닛 사이를 연결하는 n-1개의 인덕터를 포함할 수 있다. 따라서, 필터링 인덕터(Lf)를 제외하고 컨버터에 포함된 인덕터의 개수는 n+1개가 된다.

- [0061] 도 4는 일 실시예에 따른 캐스케이드 AC-AC 컨버터의 스위치 간의 중첩 시간 동안의 전류 흐름을 나타낸 회로도이다. 도 4를 참조하면, 스위치 간의 중첩 시간 동안 제1 인덕터(L1) 내지 제3 인덕터(L3)가 슛-스루 전류를 제한하는 것을 알 수 있다.

- [0062] 도 4(a)는 제1 스위치(S1) 및 제2 스위치(S2)가 온 상태인 경우의 전류 흐름을 나타낸 것이고, 도 4(b)는 제3 스위치(S3) 내지 제6 스위치(S6)가 온 상태인 경우의 전류 흐름을 나타낸 것이고, 도 4(c)는 제7 스위치(S7) 및 제8 스위치(S8)가 온 상태인 경우의 전류 흐름을 나타낸 것이다.

- [0063] 도 4(a)를 참조하면, 제1 스위치(S1) 및 제2 스위치(S2)가 온 상태인 경우 제1 인덕터(L1)가 슛-스루 전류를 제한할 수 있다. 또한, 도 4(b)를 참조하면, 제3 스위치(S3) 내지 제6 스위치(S6)가 온 상태인 경우 제3 인덕터(L3)가 슛-스루 전류를 제한할 수 있다. 또한, 도 4(c)를 참조하면, 제7 스위치(S7) 및 제8 스위치(S8)가 온 상태인 경우 제2 인덕터(L2)가 슛-스루 전류를 제한할 수 있다.

- [0065] 도 5는 일 실시예에 따른 캐스케이드 AC-AC 컨버터의 스위치 간의 데드 타임 동안의 전류 흐름을 나타낸 회로도이다. 도 4를 참조하면, 스위치가 동시에 오프 상태가 되는 데드 타임 동안의 전류 흐름을 알 수 있다.

- [0066] 도 5(a)는 제1 스위치(S1) 및 제2 스위치(S2)가 모두 오프 상태인 데드 타임의 전류 흐름을 나타낸 것이고, 도 5(b)는 제3 스위치(S3) 내지 제6 스위치(S6)가 모두 오프 상태인 데드 타임의 전류 흐름을 나타낸 것이고, 도

- 5(c)는 제7 스위치(S7) 및 제8 스위치(S8)가 모두 오프 상태인 데드 타임의 전류 흐름을 나타낸 것이다.

- [0067] 도 5(a)를 참조하면, 제1 스위치(S1) 및 제2 스위치(S2)가 모두 오프 상태인 데드 타임 동안, 제1 커패시터 (C1), 제1 다이오드(D1) 및 제2 다이오드(D2)가 인덕터 전류에 대한 안전한 경로를 제공할 수 있다.

- [0068] 또한, 도 5(b)를 참조하면, 제3 스위치(S3) 내지 제6 스위치(S6)가 모두 오프 상태인 데드 타임 동안, 제2 커패시터(C2), 제3 커패시터(C3), 및 제3 다이오드(D3) 내지 제6 다이오드(D6)가 인덕터 전류에 대한 안전한 경로를 제공할 수 있다.

- [0069] 또한, 도 5(c)를 참조하면, 제7 스위치(S7) 및 제8 스위치(S8)가 모두 오프 상태인 데드 타임 동안, 제4 커패시터(C4), 제7 다이오드(D7) 및 제8 다이오드(D8)가 인덕터 전류에 대한 안전한 경로를 제공할 수 있다.

- [0070] 따라서, 본원 발명의 컨버터는 스위치가 모두 온 상태인 중첩 시간과 스위치가 모두 오프 상태인 데드 타임 동 안에 발생하는 문제가 없기 때문에, 전류 문제를 해결할 수 있다.

- [0072] 도 6은 위상 천이 제어가 없는 경우와 위상 천이 제어가 있는 경우의 게이트 신호와 인덕터 전류 리플을 비교한 도면이다. 컨버터 제어 장치의 처리는 내부 제어부(프로세서)에 의해 수행될 수 있다. 이때, 제어부는 컨버터의 마이크로 컨트롤 유닛(MCU)일 수 있다. 구체적으로, 제어부는 컨버터에 제어 신호를 인가하는 로직 회로 등일수 있다.

- [0073] 도 6(a)는 AC-AC 컨버터의 위상 천이 제어가 없는 게이트 신호를 나타낸 도면이고, 도 6(b)는 위상 천이 제어에 의한 게이트 신호를 나타낸 도면이다.

- [0074] 도 6(a)를 참조하면, 컨버터 제어 장치는 제1 스위치(S1), 제3 스위치(S3), 제5 스위치(S5) 및 제7 스위치(S7) 의 온/오프를 제1 제어 신호에 따라 제어하였다. 또한, 제2 스위치(S2), 제4 스위치(S4), 제6 스위치(S6) 및 제8 스위치(S8)의 온/오프를 제2 제어 신호에 따라 제어하였다. 이때, 제2 제어 신호는 제1 제어 신호를 반전한 신호이다. 따라서, 위상 천이 제어가 없는 경우는 2개의 모드로 컨버터를 제어하였다.

- [0075] 위상 천이 제어를 하지 않은 경우, 도 6(a)와 같이 인덕터 전류 리플이 큰 것을 알 수 있다. 그러나, 본원 발명의 컨버터 제어 장치는 인덕터의 개수를 줄일 수 있는 캐스케이드 컨버터에 위상 천이 제어를 통해 반도체 장치의 실제 스위칭 주파수를 높이지 않고 인덕터 및 커패시터의 유효 스위칭 주파수를 증가시켜 부피를 줄일 수 있다.

- [0076] 본원 발명의 컨버터 제어 장치는 n개의 유닛을 포함하는 캐스케이드 컨버터에서 2개의 연속된 캐스케이드 유닛 의 게이트 신호를 (360/n)도만큼 위상 천이 제어를 할 수 있다.

- [0077] 도 6(b)를 참조하면, 일 실시예에 따른 컨버터 제어 장치는 2개의 유닛을 포함하는 캐스케이드 컨버터에서 180도 위상 천이 제어를 할 수 있다.

- [0078] 컨버터 제어 장치는 제1 스위치(S1) 및 제3 스위치(S3)의 온/오프를 제1 제어 신호에 의해 제어하고, 제2 스위치(S2) 및 제4 스위치(S4)의 온/오프를 제2 제어 신호에 의해 제어하고, 제5 스위치(S5) 및 제7 스위치(S7)의 온/오프를 제3 제어 신호에 의해 제어하고, 제6 스위치(S6) 및 제8 스위치(S8)의 온/오프를 제4 제어 신호에 의해 제어할 수 있다.

- [0079] 이때, 제2 제어 신호는 제1 제어 신호가 반전된 신호이고, 제4 제어 신호는 제3 제어 신호가 반전된 신호일 수 있다. 또한, 180도 위상 천이 제어로 인해, 제3 제어 신호는 제1 제어 신호에서 180도 위상 천이된 신호일 수 있다.

- [0080] 도 6(a)와 도 6(b)에 도시된 인덕터 전류(iL)를 비교하면, 위상 천이 제어가 없는 종래보다 위상 천이 제어가 있는 본원 발명에서의 인덕터 전류의 리플이 감소한 것을 확인할 수 있다.

- [0081] 도 6(b)에 도시된 바와 같이, 본원 발명의 컨버터 제어 장치는 복수의 스위치들을 4가지 모드(제1 모드 내지 제 4 모드)에 따라 제어할 수 있다.

- [0083] 도 7은 위상 천이 제어가 없는 경우, 컨버터의 모드에 따른 회로를 나타낸 도면이다.

- [0084] 도 7을 참조하면, 컨버터 제어 장치의 제어부는 제1 스위치(S1) 내지 제8 스위치(S8)의 온/오프 상태에 따라 모드를 구분할 수 있다.

- [0085] 예를 들어, 제어부는 제1 스위치(S1), 제3 스위치(S3), 제5 스위치(S5) 및 제7 스위치(S7)가 온 상태이고, 제2

- 스위치(S2), 제4 스위치(S4), 제6 스위치(S6) 및 제8 스위치(S8)가 오프인 상태를 제1 모드로 설정할 수 있다.

- [0086] 또한, 제어부는 제1 스위치(S1), 제3 스위치(S3), 제5 스위치(S5) 및 제7 스위치(S7)가 오프 상태이고, 제2 스위치(S2), 제4 스위치(S4), 제6 스위치(S6) 및 제8 스위치(S8)가 온인 상태를 제2 모드로 설정할 수 있다.

- [0087] 도 7(a)는 위상 천이 제어가 없는 경우 제1 모드에서의 전류 흐름을 나타낸 회로도이고, 도 7(b)는 위상 천이 제어가 없는 경우 제2 모드에서의 전류 흐름을 나타낸 회로도이다.

- [0088] 도 7(a)를 참조하면, 제1 모드에서 전류는 V\_S1에서 제1 스위치(S1), 제1 인덕터(L1)를 지난다. 이어서, 전류는 필터링 인덕터(Lf) 및 필터링 커패시터(Cf)를 지나 제8 다이오드(D8)를 지날 수 있다. 이어서, 전류는 V\_S2를 지나 제5 스위치(S5), 제3 인덕터(L3) 및 제4 다이오드(D4)를 지날 수 있다.

- [0089] 이때, 인덕터 전류(iL)는 도 6(a)와 같이 증가하게 된다. 또한, 인덕터 전류(iL)의 기울기는 (2Vs-V0)/L일 수 있다.

- [0090] 도 7(b)를 참조하면, 제2 모드에서 전류는 제1 다이오드(D1) 및 제1 인덕터(L1)를 지난다. 이어서, 전류는 필터링 인덕터(Lf) 및 필터링 커패시터(Cf)를 지나 제8 스위치(S8)를 지날 수 있다. 이어서, 전류는 제5 다이오드(D5), 제3 인덕터(L3) 및 제4 스위치(S4)를 지날 수 있다.

- [0091] 이때, 인덕터 전류(iL)는 도 6(a)와 같이 감소하게 된다. 또한, 인덕터 전류(iL)의 기울기는 -V0/L일 수 있다.

- [0093] 도 8은 위상 천이 제어가 있는 경우, 컨버터의 모드에 따른 회로를 나타낸 도면이다.

- [0094] 도 8을 참조하면, 컨버터 제어 장치의 제어부는 제1 스위치(S1) 내지 제8 스위치(S8)의 온/오프 상태에 따라 모드를 구분할 수 있다.

- [0095] 예를 들어, 제어부는 제1 스위치(S1), 제3 스위치(S3), 제5 스위치(S5) 및 제7 스위치(S7)가 온 상태이고, 제2 스위치(S2), 제4 스위치(S4), 제6 스위치(S6) 및 제8 스위치(S8)가 오프인 상태를 제1 모드로 설정할 수 있다.

- [0096] 구체적으로, 제어부는 일정 주기 내에서 제1 스위치(S1) 및 제3 스위치(S3)가 온 상태이면서 제5 스위치(S5) 및 제7 스위치(S7)가 온 상태에서 오프 상태로 전환되는 순간까지를 제1 모드로 설정할 수 있다. 또한 이때, 제어부는 일정 주기 내에서 제2 스위치(S2) 및 제4 스위치(S4)가 오프 상태이면서 제6 스위치(S6) 및 제8 스위치(S8)가 오프 상태였다가 온 상태로 전환되는 순간까지를 제1 모드로 설정할 수 있다.

- [0097] 또한, 제어부는 제1 스위치(S1), 제3 스위치(S3), 제6 스위치(S6) 및 제8 스위치(S8)가 온 상태이고, 제2 스위치(S2), 제4 스위치(S4), 제5 스위치(S5) 및 제7 스위치(S7)가 오프 상태인 경우를 제2 모드로 설정할 수 있다.

- [0098] 구체적으로, 제어부는 일정 주기 내에서 제1 스위치(S1) 및 제3 스위치(S3)가 온 상태이면서 제6 스위치(S6) 및 제8 스위치(S8)가 오프 상태였다가 온 상태로 전환되는 순간부터 다시 오프 상태로 전환되는 순간까지를 제2 모드로 설정할 수 있다. 또한 이때, 제어부는 일정 주기 내에서 제2 스위치(S2) 및 제4 스위치(S4)가 오프 상태이면서 제5 스위치(S5) 및 제7 스위치(S7)가 온 상태에서 오프 상태로 전환되는 순간부터 다시 온 상태로 전환되는 순간까지를 제2 모드로 설정할 수 있다.

- [0099] 또한, 제어부는 제1 스위치(S1), 제3 스위치(S3), 제5 스위치(S5) 및 제7 스위치(S7)가 온 상태이고, 제2 스위치(S2), 제4 스위치(S4), 제6 스위치(S6) 및 제8 스위치(S8)가 오프인 상태를 제3 모드로 설정할 수 있다. 이때, 제3 모드는 실질적으로 제1 모드와 동일한 모드일 수 있다.

- [0100] 구체적으로, 제어부는 일정 주기 내에서 제5 스위치(S5) 및 제7 스위치(S7)가 온 상태이면서 제1 스위치(S1) 및 제3 스위치(S3)가 온 상태였다가 오프 상태로 전환되는 순간까지를 제3 모드로 설정할 수 있다. 또한 이때, 제어부는 일정 주기 내에서 제6 스위치(S6) 및 제8 스위치(S8)가 오프 상태이면서 제2 스위치(S2) 및 제4 스위치(S4)가 오프 상태였다가 온 상태로 전환되는 순간까지를 제3 모드로 설정할 수 있다.

- [0101] 또한, 제어부는 제2 스위치(S2), 제4 스위치(S4), 제5 스위치(S5) 및 제7 스위치(S7)가 온 상태이고, 제1 스위치(S1), 제3 스위치(S3), 제6 스위치(S6) 및 제8 스위치(S8)가 오프인 상태를 제4 모드로 설정할 수 있다.

- [0102] 구체적으로, 제어부는 일정 주기 내에서 제5 스위치(S5) 및 제7 스위치(S7)가 온 상태이면서 제2 스위치(S2) 및 제4 스위치(S4)가 오프 상태였다가 온 상태로 전환된 순간부터 다시 오프 상태로 전환되는 순간까지를 제4 모드로 설정할 수 있다. 또한 이때, 제어부는 일정 주기 내에서 제6 스위치(S6) 및 제8 스위치(S8)가 오프인 상태이면서 제1 스위치(S1) 및 제3 스위치(S3)가 온 상태에서 오프 상태로 전환된 순간부터 다시 온 상태로 전환되는 순간까지를 제4 모드로 설정할 수 있다.

- [0103] 제어부는 제1 모드 제2 모드 제3 모드(제1 모드) 제4 모드의 패턴이 반복되도록 컨버터를 제어할 수 있다. 즉, 제어부는 제1 모드, 제2 모드, 제1 모드, 제4 모드 그리고 다시 제1 모드의 패턴이 반복되도록 제1 스위치(S1) 내지 제8 스위치(S2)에 대한 제어 신호를 생성할 수 있다.

- [0105] 도 8(a)는 위상 천이 제어가 있는 경우 제1 모드 및 제3 모드에서의 전류 흐름을 나타낸 회로도이고, 도 8(b)는 위상 천이 제어가 있는 경우 제2 모드에서의 전류 흐름을 나타낸 회로도이고, 도 8(c)는 위상 천이 제어가 있는 경우 제4 모드에서의 전류 흐름을 나타낸 회로도이다.

- [0106] 도 8(a)를 참조하면, 제1 모드 또는 제3 모드에서 전류는 V\_S1에서 제1 스위치(S1), 제1 인덕터(L1)를 지난다. 이어서, 전류는 필터링 인덕터(Lf) 및 필터링 커패시터(Cf)를 지나 제8 다이오드(D8)를 지날 수 있다. 이어서, 전류는 V\_S2를 지나 제5 스위치(S5), 제3 인덕터(L3) 및 제4 다이오드(D4)를 지날 수 있다.

- [0107] 이때, 인덕터 전류(iL)는 도 6(b)와 같이 증가하게 된다. 또한, 인덕터 전류(iL)의 기울기는 (2Vs-V0)/L일 수 있다.

- [0108] 도 8(b)를 참조하면, 제2 모드에서는 전류는 V\_S1에서 제1 스위치(S1), 제1 인덕터(L1)를 지난다. 이어서, 전류는 필터링 인덕터(Lf) 및 필터링 커패시터(Cf)를 지나 제8 스위치(S8)를 지날 수 있다. 이어서, 전류는 제5 다이오드(D5), 제3 인덕터(L3) 및 제4 다이오드(D4)를 지날 수 있다.

- [0109] 이때, 인덕터 전류(iL)는 도 6(b)와 같이 감소하게 된다. 또한, 인덕터 전류(iL)의 기울기는 (Vs-V0)/L일 수 있다.

- [0110] 도 8(c)를 참조하면, 제4 모드에서는 전류는 제1 다이오드(D2) 및 제1 인덕터(L1)를 지난다. 이어서, 전류는 필터링 인덕터(Lf) 및 필터링 커패시터(Cf)를 지나 제8 스위치(S8)를 지날 수 있다. 이어서, 전류는 제5 다이오드 (D5), 제3 인덕터(L3) 및 제4 스위치(S4)를 지날 수 있다.

- [0111] 이때, 인덕터 전류(iL)는 도 6(b)와 같이 감소하게 된다. 또한, 인덕터 전류(iL)의 기울기는 (Vs-V0)/L일 수 있다.

- [0113] 도 9는 일 실시예에 따른 제어 신호 입력을 위한 블록 다이어그램을 나타낸 도면이다.

- [0114] 도 9를 참조하면, 제어부의 제어 신호 생성 단계를 블록 다이어그램을 통해 파악할 수 있다. 제어부는 블록 다이어그램과 같이 제1 스위치(S1) 및 제3 스위치(S3)를 제어하는 제1 제어 신호, 제2 스위치(S2) 및 제4 스위치(S4)를 제어하는 제2 제어 신호, 제5 스위치(S5) 및 제7 스위치(S7)를 제어하는 제3 제어 신호 및 제6 스위치(S6) 및 제8 스위치(S8)를 제어하는 제4 제어 신호를 생성할 수 있다.

- [0115] 제어부는 제1 제어 신호를 생성하기 위해 DC 신호를 반송파 신호와 비교한다. 제어부는 제1 제어 신호를 반전시 켜 제2 제어 신호를 얻을 수 있다. 제어부는 제3 제어 신호를 생성하기 위해 DC 신호를 180도 위상 천이된 반송파 신호와 비교한다. 제어부는 제3 제어 신호를 반전시켜 제4 제어 신호를 얻을 수 있다.

- [0117] 도 10은 인덕터의 전압-시간 평형 조건을 나타낸 도면이다.

- [0118] 전압-시간 평형 조건은 한 번의 스위칭 주기에서 인덕터에 인가되는 전압과 시간의 곱이 0이 된다는 조건이다.

- [0119] 따라서, 도 10을 참조하면,

- [0120]  $(v_s v_o)DT_s + (-v_o)(1-D)T_s = 0$

- [0121] 의 관계를 알 수 있다.

- [0123] 도 11은 위상 천이 제어가 있는 2-유닛 캐스케이드 컨버터의 스위칭 신호를 나타낸 도면이다.

- [0124] 도 11의 스위칭 신호를 통해 도 6(b)처럼 스위치들이 동작할 수 있다.

- [0125] 도 5에서 살펴본 바와 같이, 제1 스위치(S1) 및 제3 스위치(S3)를 제어하는 제어 신호는 제2 스위치(S2) 및 제4 스위치(S4)를 제어하는 제어 신호와 반전 관계에 있음을 알 수 있다. 또한, 제1 스위치(S1) 및 제3 스위치(S3)를 제어하는 제어 신호는 제5 스위치(S5) 및 제7 스위치(S7)를 제어하는 제어 신호와 180도 위상 차이를 갖는 것을 알 수 있다.

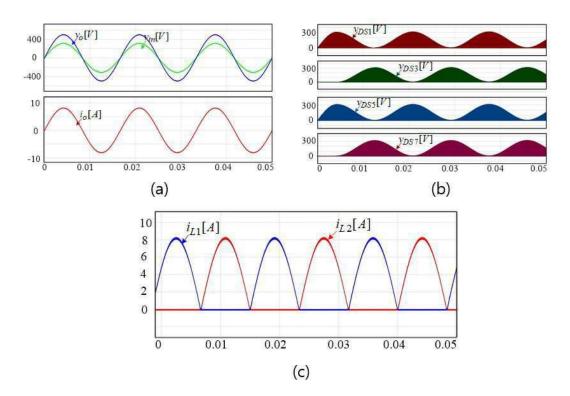

- [0127] 도 12는 위상 천이 제어가 없는 2-유닛 캐스케이드 컨버터의 시뮬레이션 파형을 나타낸 도면이다.

- [0128] 도 12(a)는 컨버터의 입력 전압, 출력 전압 및 출력 전류를 나타낸 그래프이고, 도 12(b)는 컨버터에 포함된 스

위치의 드레인-소스 전압을 나타낸 그래프이고, 도 12(c)는 인덕터 전류들을 나타낸 그래프이다.

- [0130] 도 13은 본원 발명의 일 실시예에 따른 위상 천이 제어가 있는 2-유닛 캐스케이드 컨버터의 시뮬레이션 파형을 나타낸 도면이다.

- [0131] 도 13(a)는 컨버터의 입력 전압, 출력 전압 및 출력 전류를 나타낸 그래프이고, 도 13(b)는 컨버터에 포함된 스위치의 드레인-소스 전압을 나타낸 그래프이고, 도 13(c)는 인덕터 전류들을 나타낸 그래프이다.

- [0132] 도 12(c)와 도 13(c)를 비교하면, 위상 천이 제어가 있을 때의 인덕터 전류 리플이 위상 천이 제어가 없을 때의 인덕터 전류 리플보다 작음을 알 수 있다. 따라서, 본원 발명은 종래의 캐스케이드 컨버터보다 인덕터의 개수를 줄일 수 있고, 더불어 위상 천이 제어를 통해 인덕터 전류의 리플을 줄일 수 있다.

- [0133] 인덕터의 개수를 줄이는 것은 복잡성을 줄일 수 있고, 왜곡이 적은 출력 전압을 얻을 수 있고, 인덕터 풋프린트 및 자기 부피를 줄일 수 있는 장점이 있다. 또한, 위상 천이 제어를 통해 반도체 장치의 실제 스위칭 주파수를 높이지 않고 인덕터와 커패시터의 유효 스위칭 주파수를 증가시켜 효율성을 저하시키지 않으면서 수동 소자의 부피를 줄일 수 있는 장점이 있다.

- [0135] 실시예에 따른 방법은 다양한 컴퓨터 수단을 통하여 수행될 수 있는 프로그램 명령 형태로 구현되어 컴퓨터 판독 가능 매체에 기록될 수 있다. 상기 컴퓨터 판독 가능 매체는 프로그램 명령, 데이터 파일, 데이터 구조 등을 단독으로 또는 조합하여 포함할 수 있다. 상기 매체에 기록되는 프로그램 명령은 실시예를 위하여 특별히 설계되고 구성된 것들이거나 컴퓨터 소프트웨어 당업자에게 공지되어 사용 가능한 것일 수도 있다. 컴퓨터 판독 가능 기록 매체의 예에는 하드 디스크, 플로피 디스크 및 자기 테이프와 같은 자기 매체(magnetic media), CD-ROM, DVD와 같은 광기록 매체(optical media), 플롭티컬 디스크(floptical disk)와 같은 자기-광 매체 (magneto-optical media), 및 롬(ROM), 램(RAM), 플래시 메모리 등과 같은 프로그램 명령을 저장하고 수행하도록 특별히 구성된 하드웨어 장치가 포함된다. 프로그램 명령의 예에는 컴파일러에 의해 만들어지는 것과 같은 기계어 코드뿐만 아니라 인터프리터 등을 사용해서 컴퓨터에 의해서 실행될 수 있는 고급 언어 코드를 포함한다. 상기된 하드웨어 장치는 실시예의 동작을 수행하기 위해 하나 이상의 소프트웨어 모듈로서 작동하도록 구성될 수 있으며, 그 역도 마찬가지이다

- [0136] 이상과 같이 실시예들이 비록 한정된 실시예와 도면에 의해 설명되었으나, 해당 기술분야에서 통상의 지식을 가진 자라면 상기의 기재로부터 다양한 수정 및 변형이 가능하다. 예를 들어, 설명된 기술들이 설명된 방법과 다른 순서로 수행되거나, 및/또는 설명된 시스템, 구조, 장치, 회로 등의 구성요소들이 설명된 방법과 다른 형태로 결합 또는 조합되거나, 다른 구성요소 또는 균등물에 의하여 대치되거나 치환되더라도 적절한 결과가 달성될수 있다.

- [0137] 그러므로, 다른 구현들, 다른 실시예들 및 특허청구범위와 균등한 것들도 후술하는 특허청구범위의 범위에 속한 다.

#### 도면