# (19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

*G11C* 11/413 (2006.01) *G11C* 11/412 (2006.01) *G11C* 7/12 (2006.01) *G11C* 8/08 (2006.01)

(52) CPC특허분류

*G11C* 11/413 (2013.01) *G11C* 11/412 (2013.01)

(21) 출원번호

10-2019-0008818

(22) 출원일자

2019년01월23일

심사청구일자 2019년01월23일

(11) 공개번호 10-2020-0091697

(43) 공개일자

2020년07월31일

(71) 출원인

연세대학교 산학협력단

서울특별시 서대문구 연세로 50 (신촌동, 연세대 학교)

(72) 발명자

정성욱

서울특별시 서대문구 연세로 50, 제3공학관 513호 (신촌동,연세대학교)

김기룡

서울특별시 서대문구 연세로 50, 제3공학관 206호 (신촌동,연세대학교)

(74) 대리인

김연권

전체 청구항 수 : 총 12 항

#### (54) 발명의 명칭 멀티스텝 워드라인 기반의 정적 메모리 장치 및 그 제어 방법

#### (57) 요 약

본 발명은 멀티스텝 워드라인 기반의 정적 메모리 장치 및 그 제어방법에 관한 것으로서, 일실시예에 따른 정적메모리 장치는 복수의 로우(Row)와 복수의 컬럼(Column)이 교차하는 셀 어레이에 구비된 복수의 메모리 셀과, 복수의 컬럼 중에서 비선택된 컬럼(Unselected column)에 구비되는 비트라인과 비트라인바 중에서 적어도 하나의라인을 프리차지하는 인터리브 프리차지 회로 및 비선택된 컬럼에 구비된 복수의 메모리 셀 각각에 연결되는 적어도 하나의 워드 라인을 플로팅(Floating) 상태로 제어하여, 플로팅된 워드 라인과 비선택된 컬럼에 구비되는프리차지된 라인 사이에 형성되는 기생 캐패시턴스(Parasitic capacitance) 성분을 통해 플로팅된 워드 라인을부스팅(Boosting)하는 워드라인 드라이버를 포함할 수 있다.

### 대 표 도 - 도1

#### (52) CPC특허분류

*G11C 7/12* (2013.01) *G11C 8/08* (2013.01)

### 이 발명을 지원한 국가연구개발사업

교제고유번호 2017R1A2B2006679 부처명 과학기술정보통신부 연구관리전문기관 한국연구재단

연구사업명 중견연구자지원사업

연구과제명 Domain Wall Motion 시냅스 기반의 On-Chip 지도-자율 통합학습 뉴로모픽 SoC 개발(2/3)

기 여 율 1/1

주관기관연세대학교 산학협력단연구기간2018.03.01 ~ 2019.02.28

#### 명세서

## 청구범위

#### 청구항 1

복수의 로우(Row)와 복수의 컬럼(Column)이 교차하는 셀 어레이에 구비된 복수의 메모리 셀;

상기 복수의 컬럼 중에서 비선택된 컬럼(Unselected column)에 구비되는 비트라인과 비트라인바 중에서 적어도 하나의 라인을 프리차지하는 인터리브 프리차지 회로 및

상기 비선택된 컬럼에 구비된 복수의 메모리 셀 각각에 연결되는 적어도 하나의 워드 라인을 플로팅(Floating) 상태로 제어하여, 상기 플로팅된 워드 라인과 상기 비선택된 컬럼에 구비되는 프리차지된 라인 사이에 형성되는 기생 캐패시턴스(Parasitic capacitance) 성분을 통해 상기 플로팅된 워드 라인을 부스팅(Boosting)하는 워드라 이 드라이버

를 포함하는 정적 메모리 장치.

#### 청구항 2

제1항에 있어서,

상기 인터리브 프리차지 회로는

상기 복수의 컬럼 중에서 선택된 컬럼(Selected column)에 구비되는 비트라인과 비트라인바 중에서 적어도 하나의 라인을 프리차지하는

정적 메모리 장치.

#### 청구항 3

제2항에 있어서,

상기 인터리브 프리차지 회로는

상기 선택된 컬럼에 구비되는 프리차지된 라인과 상기 비선택된 컬럼에 구비되는 프리차지된 라인 각각의 프리 차지 동작을 컬럼별로 독립적으로 제어하는

정적 메모리 장치.

#### 청구항 4

제1항에 있어서,

상기 복수의 메모리 셀 각각은

상기 비트라인과 연결된 제1 액세스 트랜지스터, 상기 비트라인바와 연결된 제2 액세스 트랜지스터, 셀 전원라인과 각각 연결된 제1 풀업 트랜지스터와 제2 풀업 트랜지스터 및 셀 소스라인과 각각 연결된 제1 풀다운 트랜지스터와 제2 풀다운 트랜지스터를 포함하는

정적 메모리 장치.

#### 청구항 5

제1항에 있어서,

상기 인터리브 프리차지 회로는

상기 복수의 컬럼 중에서 선택된 컬럼에 구비되는 비트라인과 비트라인바 중에서 적어도 하나의 라인과, 상기 비선택된 컬럼에 구비되는 비트라인과 비트라인바 중에서 적어도 하나의 라인을 동시에 프리차지하는 제1 프리 차지 동작을 수행하는 정적 메모리 장치.

#### 청구항 6

제1항에 있어서,

상기 워드라인 드라이버는

상기 적어도 하나의 워드라인에 어서트하고, 상기 어서트된 워드라인에 대해 언더 드라이브(Under Drive) 동작을 수행하는

정적 메모리 장치.

#### 청구항 7

제1항에 있어서,

상기 워드라인 드라이버는

상기 비선택된 컬럼에 구비된 복수의 메모리 셀 각각의 더미 리드(Dummy Read) 동작을 수행하여, 상기 비선택된 컬럼에 구비되는 프리차지된 라인을 방전(Discharge) 시키는

정적 메모리 장치.

#### 청구항 8

제7항에 있어서,

상기 인터리브 프리차지 회로는

상기 워드라인 드라이버에서 상기 비선택된 컬럼에 구비된 복수의 메모리 셀 각각에 연결되는 상기 적어도 하나의 워드 라인을 플로팅 상태로 제어하고, 상기 비선택된 컬럼에 구비되는 상기 방전된 라인을 다시 프리차지하는 제2 프리차지 동작을 수행하여 상기 플로팅된 워드라인과 상기 제2 프리차지 동작으로 프리차지된 라인 사이에 형성되는 상기 기생 캐패시턴스 성분을 통해 상기 플로팅된 워드 라인을 부스팅하는

정적 메모리 장치.

#### 청구항 9

인터리브 프리차지 회로에서 복수의 로우(Row)와 복수의 컬럼(Column)이 교차하는 셀 어레이에 구비된 상기 복수의 컬럼 중에서 비선택된 컬럼(Unselected column)에 구비되는 비트라인과 비트라인바 중에서 적어도 하나의라인을 프리차지 하는 단계 및

워드라인 드라이버에서 상기 셀 어레이에 구비된 복수의 메모리 셀 중에서 상기 비선택된 컬럼에 구비된 복수의 메모리 셀 각각에 연결되는 적어도 하나의 워드 라인을 플로팅(Floating) 상태로 제어하여, 상기 플로팅된 워드라인과 상기 비선택된 컬럼에 구비되는 프리차지된 라인 사이에 형성되는 기생 캐패시턴스(Parasitic capacitance) 성분을 통해 상기 플로팅된 워드 라인을 부스팅(Boosting)하는 단계

를 포함하는 정적 메모리 장치의 제어방법.

#### 청구항 10

제9항에 있어서,

상기 적어도 하나의 라인을 프리차지 하는 단계는

상기 인터리브 프리차지 회로에서 상기 복수의 컬럼 중에서 선택된 컬럼에 구비되는 비트라인과 비트라인바 중에서 적어도 하나의 라인과, 상기 비선택된 컬럼에 구비되는 비트라인과 비트라인바 중에서 적어도 하나의 라인을 동시에 프리차지하는 제1 프리차지 동작을 수행하는

정적 메모리 장치의 제어방법.

#### 청구항 11

제9항에 있어서,

상기 플로팅된 워드 라인을 부스팅하는 단계는

상기 적어도 하나의 워드라인에 어서트하고, 상기 어서트된 워드라인에 대해 언더 드라이브(Under Drive) 동작을 수행하는 단계

를 더 포함하는 정적 메모리 장치의 제어방법.

#### 청구항 12

제9항에 있어서,

상기 플로팅된 워드 라인을 부스팅하는 단계는

상기 워드라인 드라이버에서 상기 비선택된 컬럼에 구비된 복수의 메모리 셀 각각의 더미 리드(Dummy Read) 동작을 수행하여, 상기 비선택된 컬럼에 구비되는 프리차지된 라인을 방전(Discharge) 시키는 단계 및

상기 워드라인 드라이버에서 상기 비선택된 컬럼에 구비된 복수의 메모리 셀 각각에 연결되는 상기 적어도 하나의 워드 라인을 플로팅 상태로 제어하고, 상기 인터리브 프리차지 회로에서 상기 비선택된 컬럼에 구비되는 상기 방전된 라인을 다시 프리차지하는 제2 프리차지 동작을 수행하여 상기 플로팅된 워드라인과 상기 제2 프리차지 동작으로 프리차지된 라인 사이에 형성되는 상기 기생 캐패시턴스 성분을 통해 상기 플로팅된 워드 라인을 부스팅하는 단계

를 더 포함하는 정적 메모리 장치의 제어방법.

#### 발명의 설명

## 기술분야

[0001] 본 발명은 정적 메모리 장치 및 그 제어 방법에 관한 것으로서, 보다 상세하게는 멀티스텝으로 워드라인의 전압을 부스팅하는 기술적 사상에 관한 것이다.

#### 배경기술

- [0002] 트랜지스터(Transistor)는 제작 공정 중 발생하는 RDF(Random Dopant Fluctuation), LER(Line Edge Roughness) 및 WFV(Work Function Variation)으로 인해 설계자가 의도한 문턱전압(Threshold Voltage; V<sub>th</sub>)을 구현하는데 어려움이 있다.

- [0003] 즉, 트랜지스터는 문턱전압의 변화(V<sub>th</sub> variation)가 존재하며, 문턱전압은 확률 변수(Random Variable)가 되고, 문턱전압의 분포는 정규 분포(Gaussian Distribution)를 따르게 된다.

- [0004] 한편, 문턱전압의 표준편차(Standard deviation)는 하기의 수학식을 통해 도출될 수 있다. 즉, 하기의 수학식을 참조하면 트랜지스터는 길이(Length)와 폭(Width)이 작아질수록 V<sub>th</sub> variation이 심해지는 것을 알 수 있다.

- [0005] [수학식]

$$\sigma_{vth} = \frac{A_{vt}}{\sqrt{Length \times Width}}$$

[0006]

- [0007] 여기서,  $A_{Vt}$ 는 소자 및 공정 특성에 따라 결정되는 상수, Length는 트랜지스터의 길이, Width는 트랜지스터의 폭을 나타낸다.

- [0008] 한편, 복수의 트랜지스터로 메모리 셀을 형성하는 SRAM(Static Random Access Memory) 소자는 고집적화(High density integration)를 위해 매우 작은 사이즈로 제작 되므로 V<sub>th</sub> variation에 크게 영향을 받을 수 있다.

- [0009] 구체적으로, SRAM 소자에서는 메모리 셀(Memory cell)의 라이트(Write) 동작 시, V<sub>th</sub> variation에 의해 풀업 트

랜지스터의 강도(Strength)가 액세스 트랜지스터의 강도보다 커져서 데이터가 플립(Flip)되지 않는 라이트 실패 (Write failure)가 발생될 수 있다.

- [0010] 따라서, SRAM 소자에서의 라이트 실패를 방지하기 위해서는 트랜지스터 간 강도의 균형이 필요한데  $V_{th}$  variation이 크면 강도의 균형이 깨지기 쉬우므로,  $V_{th}$  variation을 개선할 수 있는 기술이 요구된다.

- [0011] 보다 구체적으로, 종래 기술은 워드라인(Word-line)의 부스팅(Boosting)을 통해 액세스 트랜지스터의 게이트 (Gate) 전압을 높여 액세스 트랜지스터의 강도를 증가시킴으로써, 라이트 특성(Write ability)을 개선하고 있다.

- [0012] 그러나, 종래의 워드라인 부스팅 기술은 워드라인의 부스팅을 위해 추가적인 캐패시터(Additional capacitor)를 사용하여 소자의 면적 증대가 불가피하다는 문제가 있다.

- [0013] 또한, 8T-SRAM 소자에서 전술한 추가적인 캐패시터 없이 라이트 워드라인(Write word-line)을 부스팅하는 종래의 기술은 리드(Read) 및 라이트 포트가 동일한 6T-SRAM 소자에서는 비선택된 컬럼(Unselected column)에서의리드 안정성(Read stability) 문제로 적용되기가 어렵다는 문제가 있다.

- [0014] 따라서, 비트-인터리브(Bit-interleaved) 구조의 6T SRAM 소자에서 면적의 증대 없이 용이하게 워드라인을 부스팅하여 라이트 수율(Yield)을 개선할 수 있는 기술의 구현이 요구된다.

#### 선행기술문헌

#### 특허문헌

[0015] (특허문헌 0001) 한국공개특허 제10-1872823호 "정적 램의 수율 예측 방법"

(특허문헌 0002) 한국공개특허 제10-2007-0080206호 "스태틱형 메모리 셀을 포함한 반도체 기억 장치"

(특허문헌 0003) 한국등록특허 제10-1579194호 "메모리 액세스 방법 및 메모리 장치"

#### 발명의 내용

## 해결하려는 과제

- [0016] 본 발명은 추가적인 캐패시터없이 워드라인과 프리차지된 비트라인 사이에 형성되는 기생 캐패시턴스 성분을 통해 워드라인을 부스팅함으로써, 장치의 크기 감소와 함께 라이트 특성(Write ability) 또한 향상시킬 수 있는 정적 메모리 장치 및 그 방법을 제공하고자 한다.

- [0017] 또한, 본 발명은 리드 및 라이트 포트가 동일한 비트-인터리브 구조의 6T-SRAM 소자에서 비선택된 컬럼에 구비된 비트라인 전압의 상승을 통해, 워드라인을 용이하게 부스팅할 수 있는 정적 메모리 장치 및 그 방법을 제공하고자 한다.

- [0018] 또한, 본 발명은 비선택된 컬럼에 구비된 비트라인 전압의 상승을 통해 워드라인을 부스팅함으로써, 라이트 특성뿐만 아니라 리드 안정성을 향상시킬 수 있는 정적 메모리 장치 및 그 방법을 제공하고자 한다.

#### 과제의 해결 수단

- [0019] 일실시예에 따른 정적 메모리 장치는 복수의 로우(Row)와 복수의 컬럼(Column)이 교차하는 셀 어레이에 구비된 복수의 메모리 셀과, 복수의 컬럼 중에서 비선택된 컬럼(Unselected column)에 구비되는 비트라인과 비트라인바 중에서 적어도 하나의 라인을 프리차지하는 인터리브 프리차지 회로 및 비선택된 컬럼에 구비된 복수의 메모리 셀 각각에 연결되는 적어도 하나의 워드 라인을 플로팅(Floating) 상태로 제어하여, 플로팅된 워드 라인과 비선택된 컬럼에 구비되는 프리차지된 라인 사이에 형성되는 기생 캐패시턴스(Parasitic capacitance) 성분을 통해 플로팅된 워드 라인을 부스팅(Boosting)하는 워드라인 드라이버를 포함할 수 있다.

- [0020] 일측에 따르면, 인터리브 프리차지 회로는 복수의 컬럼 중에서 선택된 컬럼(Selected column)에 구비되는 비트라인과 비트라인바 중에서 적어도 하나의 라인을 프리차지할 수 있다.

- [0021] 일측에 따르면, 인터리브 프리차지 회로는 선택된 컬럼에 구비되는 프리차지된 라인과 비선택된 컬럼에 구비되

는 프리차지된 라인 각각의 프리차지 동작을 컬럼별로 독립적으로 제어할 수 있다.

- [0022] 일측에 따르면, 복수의 메모리 셀 각각은 비트라인과 연결된 제1 액세스 트랜지스터, 비트라인바와 연결된 제2 액세스 트랜지스터, 셀 전원라인과 각각 연결된 제1 풀업 트랜지스터와 제2 풀업 트랜지스터 및 셀 소스라인과 각각 연결된 제1 풀다운 트랜지스터와 제2 풀다운 트랜지스터를 포함할 수 있다.

- [0023] 일측에 따르면, 인터리브 프리차지 회로는 복수의 컬럼 중에서 선택된 컬럼에 구비되는 비트라인과 비트라인바 중에서 적어도 하나의 라인과, 비선택된 컬럼에 구비되는 비트라인과 비트라인바 중에서 적어도 하나의 라인을 동시에 프리차지하는 제1 프리차지 동작을 수행할 수 있다.

- [0024] 일측에 따르면, 워드라인 드라이버는 적어도 하나의 워드라인에 어서트하고, 어서트된 워드라인에 대해 언더 드라이브(Under Drive) 동작을 수행할 수 있다.

- [0025] 일측에 따르면, 워드라인 드라이버는 비선택된 컬럼에 구비된 복수의 메모리 셀 각각의 더미 리드(Dummy Read) 동작을 수행하여, 비선택된 컬럼에 구비되는 프리차지된 라인을 방전(Discharge) 시킬 수 있다.

- [0026] 일측에 따르면, 인터리브 프리차지 회로는 워드라인 드라이버에서 비선택된 컬럼에 구비된 복수의 메모리 셀 각 각에 연결되는 적어도 하나의 워드 라인을 플로팅 상태로 제어하고, 비선택된 컬럼에 구비되는 방전된 라인을 다시 프리차지하는 제2 프리차지 동작을 수행하여 플로팅된 워드라인과 제2 프리차지 동작으로 프리차지된 라인사이에 형성되는 기생 캐패시턴스 성분을 통해 플로팅된 워드 라인을 부스팅할 수 있다.

- [0027] 일실시예에 따른 정적 메모리 장치의 제어 방법은 인터리브 프리차지 회로에서 복수의 로우(Row)와 복수의 컬럼 (Column)이 교차하는 셀 어레이에 구비된 복수의 컬럼 중에서 비선택된 컬럼(Unselected column)에 구비되는 비트라인과 비트라인바 중에서 적어도 하나의 라인을 프리차지 하는 단계 및 워드라인 드라이버에서 셀 어레이에 구비된 복수의 메모리 셀 중에서 비선택된 컬럼에 구비된 복수의 메모리 셀 각각에 연결되는 적어도 하나의 워드 라인을 플로팅(Floating) 상태로 제어하여, 플로팅된 워드 라인과 비선택된 컬럼에 구비되는 프리차지된 라인 사이에 형성되는 기생 캐패시턴스(Parasitic capacitance) 성분을 통해 플로팅된 워드 라인을 부스팅 (Boosting)하는 단계를 포함할 수 있다.

- [0028] 일측에 따르면, 적어도 하나의 라인을 프리차지 하는 단계는 인터리브 프리차지 회로에서 복수의 컬럼 중에서 선택된 컬럼에 구비되는 비트라인과 비트라인바 중에서 적어도 하나의 라인과, 비선택된 컬럼에 구비되는 비트라인과 비트라인바 중에서 적어도 하나의 라인을 동시에 프리차지하는 제1 프리차지 동작을 수행할 수 있다.

- [0029] 일측에 따르면, 플로팅된 워드 라인을 부스팅하는 단계는 적어도 하나의 워드라인에 어서트하고, 어서트된 워드라인에 대해 언더 드라이브(Under Drive) 동작을 수행하는 단계를 더 포함할 수 있다.

- [0030] 일측에 따르면, 플로팅된 워드 라인을 부스팅하는 단계는 워드라인 드라이버에서 비선택된 컬럼에 구비된 복수의 메모리 셀 각각의 더미 리드(Dummy Read) 동작을 수행하여, 비선택된 컬럼에 구비되는 프리차지된 라인을 방전(Discharge) 시키는 단계 및 워드라인 드라이버에서 비선택된 컬럼에 구비된 복수의 메모리 셀 각각에 연결되는 적어도 하나의 워드 라인을 플로팅 상태로 제어하고, 인터리브 프리차지 회로에서 비선택된 컬럼에 구비되는 방전된 라인을 다시 프리차지하는 제2 프리차지 동작을 수행하여 플로팅된 워드라인과 제2 프리차지 동작으로 프리차지된 라인 사이에 형성되는 기생 캐패시턴스 성분을 통해 플로팅된 워드 라인을 부스팅하는 단계를 더 포함할 수 있다.

#### 발명의 효과

- [0031] 일실시예에 따르면, 추가적인 캐패시터 없이 워드라인과 프리차지된 비트라인 사이에 형성되는 기생 캐패시턴스 성분을 통해 워드라인을 부스팅함으로써, 장치의 크기 감소와 함께 라이트 특성(Write ability) 또한 향상시킬수 있다.

- [0032] 일실시예에 따르면, 리드 및 라이트 포트가 동일한 비트-인터리브 구조의 6T-SRAM 소자에서 비선택된 컬럼에 구비된 비트라인 전압의 상승을 통해, 워드라인을 용이하게 부스팅할 수 있다.

- [0033] 일실시예에 따르면, 비선택된 컬럼에 구비된 비트라인 전압의 상승을 통해 워드라인을 부스팅함으로써, 라이트 특성뿐만 아니라 리드 안정성을 향상시킬 수 있다.

### 도면의 간단한 설명

- [0034] 도 1은 일실시예에 따른 정적 메모리 장치를 설명하기 위한 도면이다.

- 도 2는 일실시예에 따른 정적 메모리 장치에 구비된 메모리 셀의 예시를 설명하기 위한 도면이다.

- 도 3a는 일실시예에 따른 정적 메모리 장치의 상세한 구조를 설명하기 위한 도면이다.

- 도 3b는 일실시예에 따른 정적 메모리 장치의 상세한 동작을 설명하기 위한 도면이다.

- 도 4는 일실시예에 따른 정적 메모리 장치의 제어방법을 설명하기 위한 도면이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0035] 본 명세서에 개시되어 있는 본 발명의 개념에 따른 실시예들에 대해서 특정한 구조적 또는 기능적 설명들은 단지 본 발명의 개념에 따른 실시예들을 설명하기 위한 목적으로 예시된 것으로서, 본 발명의 개념에 따른 실시예들은 다양한 형태로 실시될 수 있으며 본 명세서에 설명된 실시예들에 한정되지 않는다.

- [0036] 본 발명의 개념에 따른 실시예들은 다양한 변경들을 가할 수 있고 여러 가지 형태들을 가질 수 있으므로 실시예들을 도면에 예시하고 본 명세서에 상세하게 설명하고자 한다. 그러나, 이는 본 발명의 개념에 따른 실시예들을 특정한 개시형태들에 대해 한정하려는 것이 아니며, 본 발명의 사상 및 기술 범위에 포함되는 변경, 균등물, 또는 대체물을 포함한다.

- [0037] 제1 또는 제2 등의 용어를 다양한 구성요소들을 설명하는데 사용될 수 있지만, 상기 구성요소들은 상기 용어들에 의해 한정되어서는 안 된다. 상기 용어들은 하나의 구성요소를 다른 구성요소로부터 구별하는 목적으로만, 예를 들어 본 발명의 개념에 따른 권리 범위로부터 이탈되지 않은 채, 제1 구성요소는 제2 구성요소로 명명될 수 있고, 유사하게 제2 구성요소는 제1 구성요소로도 명명될 수 있다.

- [0038] 어떤 구성요소가 다른 구성요소에 "연결되어" 있다거나 "접속되어" 있다고 언급된 때에는, 그 다른 구성요소에 직접적으로 연결되어 있거나 또는 접속되어 있을 수도 있지만, 중간에 다른 구성요소가 존재할 수도 있다고 이해되어야 할 것이다. 반면에, 어떤 구성요소가 다른 구성요소에 "직접 연결되어" 있다거나 "직접 접속되어" 있다고 언급된 때에는, 중간에 다른 구성요소가 존재하지 않는 것으로 이해되어야 할 것이다. 구성요소들 간의 관계를 설명하는 표현들, 예를 들어 "~사이에"와 "바로~사이에" 또는 "~에 직접 이웃하는" 등도 마찬가지로 해석되어야 한다.

- [0039] 본 명세서에서 사용한 용어는 단지 특정한 실시예들을 설명하기 위해 사용된 것으로, 본 발명을 한정하려는 의도가 아니다. 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다. 본 명세서에서, "포함하다" 또는 "가지다" 등의 용어는 설시된 특징, 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것이 존재함으로 지정하려는 것이지, 하나 또는 그 이상의 다른 특징들이나 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것들의 존재 또는 부가 가능성을 미리 배제하지 않는 것으로 이해되어야 한다.

- [0040] 다르게 정의되지 않는 한, 기술적이거나 과학적인 용어를 포함해서 여기서 사용되는 모든 용어들은 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에 의해 일반적으로 이해되는 것과 동일한 의미를 가진다. 일반적으로 사용되는 사전에 정의되어 있는 것과 같은 용어들은 관련 기술의 문맥상 가지는 의미와 일치하는 의미를 갖는 것으로 해석되어야 하며, 본 명세서에서 명백하게 정의하지 않는 한, 이상적이거나 과도하게 형식적인 의미로 해석되지 않는다.

- [0042] 이하, 실시예들을 첨부된 도면을 참조하여 상세하게 설명한다. 그러나, 특허출원의 범위가 이러한 실시예들에 의해 제한되거나 한정되는 것은 아니다. 각 도면에 제시된 동일한 참조 부호는 동일한 부재를 나타낸다.

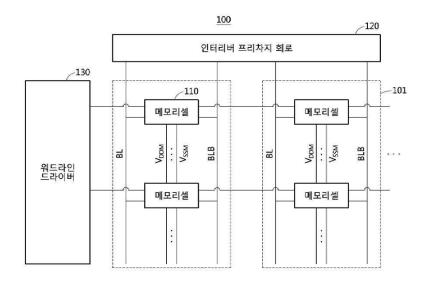

- [0044] 도 1은 일실시예에 따른 정적 메모리 장치를 설명하기 위한 도면이다.

- [0045] 도 1을 참조하면, 일실시예에 따른 정적 메모리 장치(100)는 추가적인 캐패시터 없이, 워드라인과 프리차지된 비트라인 사이에 형성되는 기생 캐패시턴스(Parasitic capacitance) 성분을 통해 워드라인을 부스팅(Boosting) 함으로써, 장치의 크기 감소와 함께 라이트 특성(Write ability) 또한 향상시킬 수 있다.

- [0046] 또한, 정적 메모리 장치(100)는 비선택된 컬럼(Unselected column)에 구비된 비트라인 전압의 상승을 통해, 리드 및 라이트 포트가 동일한 비트-인터리브(Bit-interleaved) 구조의 6T-SRAM 소자에서 워드라인을 용이하게 부

스팅할 수 있다.

- [0047] 또한, 정적 메모리 장치(100)는 비선택된 컬럼에 구비된 비트라인 전압의 상승을 통해 워드라인을 부스팅함으로 써, 라이트 특성뿐만 아니라 리드 안정성(Read stability)을 향상시킬 수 있다.

- [0048] 이를 위해, 일실시예에 따른 정적 메모리 장치(100)는 복수의 메모리 셀(110), 인터리브 프리차지 회로(120) 및 워드라인 드라이버(130)를 포함할 수 있다.

- [0049] 예를 들면, 일실시예에 따른 정적 메모리 장치(100)는 비트-인터리브 구조로 구현되는 6T-SRAM 소자일 수 있다.

- [0050] 다시 말해, 일실시예에 따른 정적 메모리 장치(100)는 같은 데이터 단위, 즉, 같은 워드(Word)에 속하는 메모리 셀(110)들을 인접하여 배치시키지 않고, 서로 다른 워드에 속하는 메모리 셀(110)들을 인접하여 배치시키는 비트 인터리브 구조로 형성된 6T-SRAM 소자일 수 있다.

- [0051] 구체적으로, 일실시예에 따른 복수의 메모리 셀(110)은 복수의 로우(Row)와 복수의 컬럼(Column; 101)이 교차하는 셀 어레이에 구비될 수 있다.

- [0052] 일실시예에 따른 메모리 셀(110)의 상세한 구조는 이후 실시예 도 2를 통해 보다 구체적으로 설명하기로 한다.

- [0053] 다음으로, 일실시예에 따른 인터리브 프리차지 회로(120)는 복수의 컬럼(101) 중에서 비선택된 컬럼(Unselected column)에 구비되는 비트라인(BL)과 비트라인바(BLB) 중에서 적어도 하나의 라인을 프리차지할 수 있다.

- [0054] 예를 들면, 비선택된 컬럼(Unselected column)은 셀 어레이에 구비된 복수의 컬럼(101) 중에서 선택된 컬럼 (Selected column)을 제외한 나머지 컬럼들일 수 있다.

- [0055] 또한, 선택된 컬럼은 복수의 메모리 셀(110) 중에서 홀드(Hold) 동작, 라이트(Write) 동작 및 리드(Read) 동작 중 어느 하나의 동작을 수행하기 위해 선택되는 타겟 메모리 셀이 포함된 컬럼일 수 있다.

- [0056] 일측에 따르면, 인터리브 프리차지 회로(120)는 복수의 컬럼 중에서 선택된 컬럼(Selected column)에 구비되는 비트라인(BL)과 비트라인바(BLB) 중에서 적어도 하나의 라인을 프리차지할 수 있다.

- [0057] 일측에 따르면, 인터리브 프리차지 회로(120)는 선택된 컬럼과 비선택된 컬럼에 구비되는 프리차지된 라인 각각 의 프리차지 동작을 컬럼별로 독립적으로 제어할 수 있다.

- [0058] 다시 말해, 인터리브 프리차지 회로(120)는 비트 인터리브 구조에 따라 각 컬럼별로 서로 다른 프리차지 제어신호를 인가하여 프리차지 동작을 독립적으로 제어하도록 구현될 수 있다.

- [0059] 일측에 따르면, 인터리브 프리차지 회로(120)는 복수의 컬럼(101) 중에서 선택된 컬럼에 구비되는 비트라인(BL)과 비트라인바(BLB) 중에서 적어도 하나의 라인과, 복수의 컬럼(101) 중에서 비선택된 컬럼에 구비되는 비트라인(BL)과 비트라인바(BLB) 중에서 적어도 하나의 라인을 동시에 프리차지하는 제1 프리차지 동작을 수행할 수있다.

- [0060] 다시 말해, 인터리브 프리차지 회로(120)는 선택된 컬럼과 나머지 비선택된 컬럼에서의 프리차지 동작을 동일한 타이밍에 수행하는 제1 프리차지 동작을 수행할 수 있다.

- [0061] 다음으로, 일실시예에 따른 워드라인 드라이버(130)는 비선택된 컬럼에 구비된 복수의 메모리 셀(110) 각각에 연결되는 적어도 하나의 워드 라인을 플로팅(Floating) 상태로 제어함으로써, 플로팅된 워드 라인과 비선택된 컬럼에 구비되는 프리차지된 라인 사이에 형성되는 기생 캐패시턴스(Parasitic capacitance) 성분을 통해 플로팅된 워드 라인을 부스팅(Boosting)할 수 있다.

- [0062] 보다 구체적으로, 워드라인 드라이버(130)는 적어도 하나의 워드라인에 어서트(Assert)하고, 어서트된 워드라인 에 대해 언더 드라이브(Under Drive) 동작을 수행할 수 있다.

- [0063] 다시 말해, 워드라인 드라이버(130)는 정상 동작시 워드라인에 인가되는 전원전압(VDD) 레벨의 워드라인 전압 보다 낮은 레벨의 워드라인 전압을 워드라인에 인가하는 언더 드라이브 동작을 수행할 수 있다.

- [0064] 다음으로, 워드라인 드라이버(130)는 복수의 컬럼(101) 중 비선택된 컬럼에 구비된 복수의 메모리 셀(110) 각각 의 더미 리드(Dummy Read) 동작을 수행하여, 비선택된 컬럼에 구비되는 프리차지된 라인을 방전(Discharge) 시킬 수 있다.

- [0065] 다시 말해, 워드라인 드라이버(130)는 비선택된 컬럼에 구비된 비트라인(BL) 및 비트라인바(BLB) 중에서 제1 프리카지 동작을 통해 비선택된 컬럼에 구비되는 프리차지된 라인을 방전시키는 더미 리드 동작을 수행할 수

있다.

- [0066] 다음으로, 워드라인 드라이버(130)는 비선택된 컬럼에 구비된 복수의 메모리 셀(110) 각각에 연결되는 적어도 하나의 워드 라인을 플로팅 상태로 제어할 수 있다.

- [0067] 이때, 인터리브 프리차지 회로(120)는 워드라인 드라이버(130)에서 적어도 하나의 워드 라인을 플로팅 상태로 제어하면, 방전된 비트라인(BL)과 비트라인바(BLB) 중 어느 하나의 라인을 다시 프리차지하는 제2 프리차지 동작을 수행하여, 플로팅된 워드라인과 제2 프리차지 동작으로 프리차지된 라인 사이에 형성되는 기생 캐패시턴스 성분을 통해 플로팅된 워드 라인을 부스팅할 수 있다.

- [0068] 일실시예에 따른 정적 메모리 장치의 상세한 동작은 이후 실시예 도 3a 내지 도 3b를 통해 보다 구체적으로 설명하기로 한다.

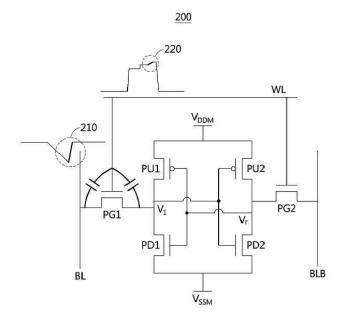

- [0070] 도 2는 일실시예에 따른 정적 메모리 장치에 구비된 메모리 셀의 예시를 설명하기 위한 도면이다.

- [0071] 다시 말해, 도 2의 메모리 셀(200)은 도 1에서 설명한 일실시예에 따른 메모리 셀(110)일 수 있다.

- [0072] 도 2를 참조하면, 일실시예에 따른 메모리 셀(200)은 6개의 트랜지스터를 구비하는 6T 구조로 형성될 수 있다.

- [0073] 또한, 이하에서 도 2를 통해 설명하는 메모리 셀(200)은 도 1을 통해 설명한 비선택된 컬럼에 구비된 메모리 셀일 수 있다.

- [0074] 일측에 따르면, 메모리 셀(200)은 비트라인(BL)과 연결된 제1 액세스 트랜지스터(PG1), 비트라인바와 연결된 제 2 액세스 트랜지스터(PG2)를 포함할 수 있다.

- [0075] 또한, 메모리 셀(200)은 셀 전원전압(V<sub>DDM</sub>)이 인가되는 셀 전원라인과 각각 연결된 제1 풀업 트랜지스터(PU1)와 제2 풀업 트랜지스터(PU2) 및 셀 소스전압(V<sub>SSM</sub>)이 인가되는 셀 소스라인과 각각 연결된 제1 풀다운 트랜지스터 (PD1)와 제2 풀다운 트랜지스터(PD2)를 포함할 수 있다.

- [0076] 일측에 따르면, 제1 액세스 트랜지스터(PG1)와 제2 액세스 트랜지스터(PG2)는 NMOS 트랜지스터로 구성될 수 있으며, 제1 액세스 트랜지스터(PG1)와 제2 액세스 트랜지스터(PG2) 각각의 게이트 단자는 워드라인(WL)과 연결될 수 있다.

- [0077] 일측에 따르면, 제1 풀업 트랜지스터(PU1)와 제2 풀업 트랜지스터(PU2)는 PMOS 트랜지스터로 구성될 수 있고, 제1 풀다운 트랜지스터(PD1)와 제2 풀다운 트랜지스터(PD2)는 NMOS 트랜지스터로 구성될 수 있다.

- [0078] 또한, 제1 풀업 트랜지스터(PU1)와 제1 풀다운 트랜지스터(PD1)의 게이트 단자는 V<sub>r</sub> 노드와 연결되고 드레인 단자는 V<sub>l</sub> 노드에 서로 연결되어 하나의 인버터를 구성하고, 제2 풀업 트랜지스터(PU2)와 제2 풀다운 트랜지스터 (PD2)의 게이트 단자는 V<sub>l</sub> 노드에 연결되고 드레인 단자는 V<sub>r</sub> 노드에 서로 연결되어 다른 하나의 인버터를 구성할 수 있다.

- [0079] 또한, 제1 풀업 트랜지스터(PU1)와 제1 풀다운 트랜지스터(PD1)로 형성된 인버터와, 제2 풀업 트랜지스터(PU2)와 제2 풀다운 트랜지스터(PD2)로 형성된 인버터는 상호결합(Cross-Coupled)된 구조로 구성될 수 있다.

- [0080] 한편, 일실시예에 따른 메모리 셀(200)에서 제1 액세스 트랜지스터(PG1)와 제2 액세스 트랜지스터(PG2)의 게이 트 단자에 연결된 워드라인(WL)은 도 1의 워드라인 드라이버(130)를 통해 플로팅(Floating) 상태로 제어될 수 있다.

- [0081] 한편, 비트라인(BL)과 비트라인바(BLB) 중 적어도 하나의 라인은 도 1의 인터리브 프리차지 회로(120)를 통한 프리차지 동작으로 인하여 참조부호 210에 도시된 것과 같이 전압이 상승할 수 있다.

- [0082] 한편, 플로팅된 워드라인(WL)의 전압은 참조부호 220에 도시된 것과 같이 적어도 하나의 라인의 전압 상승 및 기생 캐패시턴스 성분을 통해 부스팅 될 수 있다.

- [0083] 도 2에서는 기생 캐패시턴스가 워드라인(Ⅶ)과 비트라인(BL) 사이에만 도시되어 있으나, 워드라인(Ⅶ)과 비트라인(BLB) 사이에도 형성될 수 있다.

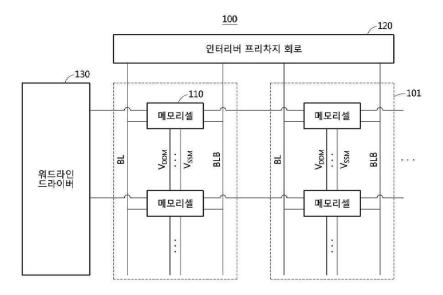

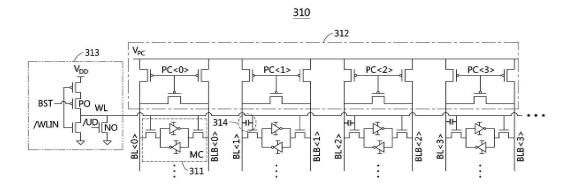

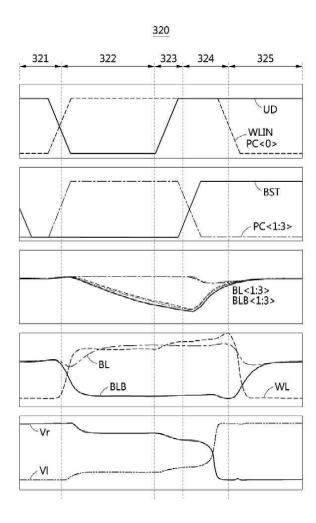

- [0085] 도 3a는 일실시예에 따른 정적 메모리 장치의 상세한 구조를 설명하기 위한 도면이고, 도 3b는 일실시예에 따른 정적 메모리 장치의 상세한 동작을 설명하기 위한 도면이다.

- [0086] 다시 말해, 도 3a 내지 도 3b는 도 1 내지 도 2를 통해 설명한 일실시예에 따른 정적 메모리 장치의 구조 및 동작에 대한 예시를 설명하는 도면으로, 이후 실시예 도 3a 내지 도 3b를 통해 설명하는 내용 중 일실시예에 따른 정적 메모리 장치를 통해 설명한 내용과 중복되는 설명은 생략하기로 한다.

- [0087] 도 3a 내지 3b를 참조하면, 참조부호 310은 일실시예에 따른 정적 메모리 장치의 상세한 구조를 나타내며, 일실 시예에 따른 정적 메모리 장치(310)는 복수의 컬럼 각각에 구비된 복수의 메모리 셀(311), 인터리브 프리차지회로(312) 및 워드라인 드라이버(313)를 포함할 수 있다.

- [0088] 또한, 참조부호 320은 정적 메모리 장치(310)의 동작 타이밍을 나타낸다.

- [0089] 예를 들면, 참조부호 320에 도시된 정적 메모리 장치(310)의 동작은 선택된 컬럼(Selected column)에 대한 라이트(Write) 동작 또는 리드(Read) 동작 시에 수행될 수 있으나, 바람직하게는 라이트 동작 시에 수행될 수 있다.

- [0091] 이하에서는 참조부호 310을 참조하여 일실시예에 따른 정적 메모리 장치의 상세한 구성에 대하여 설명하기로 한다.

- [0092] 구체적으로, 복수의 메모리 셀(311)은 복수의 로우(Row)와 복수의 컬럼(Column)이 교차하는 셀 어레이에 구비될 수 있다.

- [0093] 참조부호 310에서는 복수의 컬럼 중에서 비트라인 'BL<0>'과 비트라인바 'BLB<0>'를 구비하는 컬럼을 선택된 컬럼(Selected column)으로 가정하고, 나머지 비트라인 'BL<1>', 'BL<2>' 및 'BL<3>'과 비트라인바 'BLB<1>', 'BLB<2>' 및 'BLB<3>'를 구비하는 각각의 컬럼들을 비선택된 컬럼(Unselected column)으로 가정하여 설명하기로 한다.

- [0094] 일측에 따르면, 인터리브 프리차지 회로(312)는 선택된 컬럼과 비선택된 컬럼에 구비되는 비트라인 'BL<0>', 'BL<1>', 'BL<2>' 및 'BL<3>'과 비트라인바 'BLB<0>', 'BLB<1>', 'BLB<2>' 및 'BLB<3>' 중에서 적어도 하나의 라인을 프리차지하는 동작을 각 컬럼별로 독립적으로 제어할 수 있다.

- [0095] 보다 구체적으로, 인터리브 프리차지 회로(312)는 프리차지 전압 'V<sub>PC</sub>'이 인가되는 라인과 각각의 컬럼의 비트라인 'BL<0>', 'BL<1>', 'BL<2>', 'BL<3>' 및 비트라인바 'BLB<0>', 'BLB<1>', 'BLB<2>', 'BLB<3>' 사이에 각각의 컬럼별로 구비되는 3개의 PMOS 트랜지스터를 포함할 수 있다.

- [0096] 또한, 각각의 컬럼별로 구비된 3개의 PMOS 트랜지스터들의 게이트 단자는 서로 연결되고, 각각의 컬럼별로 구비된 3개의 PMOS 트랜지스터들의 게이트 단자를 통해 컬럼별로 서로 다른 프리차지 제어신호 'PC<0>', 'PC<1>', 'PC<2>' 및 'PC<3>'를 수신할 수 있다.

- [0097] 예를 들면, 인터리브 프리차지 회로(312)는 정적 메모리 장치(310) 내에 구비된 별도의 제어 회로를 통해 프리 차지 제어신호 'PC<0>', 'PC<1>', 'PC<2>' 및 'PC<3>'를 수신할 수 있다.

- [0098] 보다 구체적인 예를 들면, 인터리브 프리차지 회로(312)는 'Low' 레벨의 프리차지 제어신호 'PC<0>'를 수신하면, 선택된 컬럼에 구비된 비트라인 'BL<0>'과 비트라인바 'BLB<0>' 중 적어도 하나의 라인을 프리차지할 수 있다.

- [0099] 또한, 인터리브 프리차지 회로(312)는 'Low' 레벨의 프리차지 제어신호 'PC<1>'를 수신하면, 비선택된 컬럼에 구비된 비트라인 'BL<1>'과 비트라인바 'BLB<1>' 중 적어도 하나의 라인을 프리차지할 수 있다.

- [0100] 또한, 인터리브 프리차지 회로(312)는 'Low' 레벨의 프리차지 제어신호 'PC<2>'를 수신하면, 비선택된 컬럼에 구비된 비트라인 'BL<2>'과 비트라인바 'BLB<2>' 중 적어도 하나의 라인을 프리차지할 수 있다.

- [0101] 또한, 인터리브 프리차지 회로(312)는 'Low' 레벨의 프리차지 제어신호 'PC<3>'를 수신하면, 비선택된 컬럼에 구비된 비트라인 'BL<3>'과 비트라인바 'BLB<3>' 중 적어도 하나의 라인을 프리차지할 수 있다.

- [0102] 예를 들면, 전술한 프리차지 제어신호 'PC<0>', 'PC<1>', 'PC<2>' 및 'PC<3>'는 동일한 타이밍에 인가될 수 있고, 각 컬럼별로 서로 다른 타이밍에 인가될 수도 있다.

- [0103] 한편, 워드라인 드라이버(313)는 게이트 단자가 서로 연결된 PMOS 트랜지스터 및 NMOS 트랜지스터와, 게이트 단

자가 서로 연결된 PMOS 트랜지스터 및 NMOS 트랜지스터 사이에 구비된 플로팅 제어 트랜지스터 'PO'와, 워드라 인(WL)과 접지라인(GND; Ground line) 사이에 연결되는 언더 드라이브 트랜지스터 'NO'를 포함할 수 있다.

- [0104] 예를 들면, 플로팅 제어 트랜지스터 'PO'는 PMOS 트랜지스터이고, 언더 드라이브 트랜지스터 'NO'는 NMOS 트랜지스터일 수 있다.

- [0105] 보다 구체적으로, 플로팅 제어 트랜지스터 'PO'는 플로팅 제어신호(BST)를 게이트 단자로 수신하여 스위칭 동작을 수행할 수 있다.

- [0106] 또한, 게이트 단자가 서로 연결된 PMOS 트랜지스터 및 NMOS 트랜지스터는 반전된 워드라인 제어신호 '/WLIN'를 게이트 단자로 수신하여 스위칭 동작을 수행하고, 언더 드라이브 트랜지스터 'NO'는 반전된 언더 드라이브 제어 신호 '/UD'를 수신하여 스위칭 동작을 수행할 수 있다.

- [0107] 예를 들면, 반전된 워드라인 제어신호 '/WLIN'는 워드라인 제어신호 'WLIN'가 High 레벨일 때 Low 레벨이 되고, 워드라인 제어신호 'WLIN'가 Low 레벨일 때 High 레벨이 되는 신호일 수 있다.

- [0108] 또한, 반전된 언더 드라이브 제어신호 '/UD'는 언더 드라이브 제어신호 'UD'가 High 레벨일 때 Low 레벨이되고, 언더 드라이브 제어신호 'UD'가 Low 레벨일 때 High 레벨이 되는 신호일 수 있다.

- [0110] 이하에서는 참조부호 310 및 320을 참조하여, 참조부호 320에 도시된 일실시예에 따른 정적 메모리 장치의 동작타이밍에 대해 보다 구체적으로 설명 하기로 한다.

- [0111] 참조부호 320에 도시된 동작 타이밍에서 'UD'는 언더 드라이브 제어신호를 나타내고, 'WLIN'은 워드라인 제어신호를 나타내며, 'BST'는 플로팅 제어신호를 나타낸다.

- [0112] 또한, 'PC<0>'는 선택된 컬럼의 프리차지 동작을 제어하기 위한 프리차지 제어신호를 나타내고, 'PC<1:3>'는 각 각의 비선택된 컬럼 각각의 프리차지 동작을 제어하기 위한 프리차지 제어신호 'PC<1>', 'PC<2>' 및 'PC<3>'를 나타낸다.

- [0113] 또한, 참조부호 320에 도시된 동작 타이밍에서 'BL<1:3>'은 비선택된 컬럼 각각에 구비된 비트라인 'BL<1>', 'BL<2>' 및 'BL<3>'에 인가되는 신호를 나타내고, 'BLB<1:3>'은 비선택된 컬럼 각각에 구비된 비트라인바 'BLB<1>', 'BLB<2>' 및 'BLB<3>'에 인가되는 신호를 나타낸다.

- [0114] 또한, 참조부호 320에 도시된 동작 타이밍에서 'BL' 및 'BLB'는 선택된 컬럼의 비트라인 'BL<0>' 및 비트라인바 'BLB<0>' 각각에 인가되는 신호를 나타내고, 'V<sub>r</sub>' 및 'V<sub>l</sub>'은 선택된 컬럼에 구비되는 메모리 셀 내에 구비된 V<sub>r</sub> 노드 및 V<sub>l</sub> 노드를 나타낸다.

- [0115] 구체적으로, 참조부호 320의 321 구간에서 일실시예에 따른 정적 메모리 장치(310)는 비선택된 컬럼에 구비된 비트라인 'BL<1>', 'BL<2>' 및 'BL<3>'과, 비트라인바 'BLB<1>', 'BLB<2>' 및 'BLB<3>'를 프리차지할 수 있다.

- [0116] 보다 구체적으로, 321 구간에서 인터리브 프리차지 회로(312)는 Low 레벨의 프리차지 제어 신호 'PC<1:3>'를 수신하여, 비선택된 컬럼 각각에 구비되는 비트라인 'BL<1>', 'BL<2>' 및 'BL<3>'과, 비트라인바 'BLB<1>', 'BLB<2>' 및 'BLB<3>'에 대한 프리차지 동작을 수행할 수 있다.

- [0117] 일측에 따르면, 321 구간에서 일실시예에 따른 정적 메모리 장치(310)는 선택된 컬럼에 구비된 비트라인 'BL<0>'과, 비트라인바 'BLB<0>'를 프리차지할 수도 있다.

- [0118] 다음으로, 322 구간에서 일실시예에 따른 정적 메모리 장치(310)는 워드라인(WL)에 어서트하고, 어서트된 워드라인(WL)에 대해 언더 드라이브(Under Drive) 동작을 수행하여 리드 안정성(Read stability)을 향상시킬 수 있다.

- [0119] 보다 구체적으로, 322 구간에서 워드라인 드라이버(313)는 Low 레벨의 반전된 워드라인 제어신호 '/WLIN'와 Low 레벨의 플로팅 제어신호 'BST'와 High 레벨의 반전된 언더 드라이브 제어신호 '/UD'를 수신할 수 있다.

- [0120] 즉, 322 구간에서 워드라인 드라이버(313)는 전술한 신호들을 수신하여 게이트 단자가 서로 연결된 PMOS 트랜지스터와, 플로팅 제어 트랜지스터 'PO' 및 언더 드라이브 트랜지스터 'NO'를 턴온(Turn-on) 상태로 제어함으로써, 언더 드라이브 동작을 수행할 수 있다.

- [0121] 다음으로, 323 구간에서 일실시예에 따른 정적 메모리 장치(310)는 비선택된 컬럼에 구비되는 비트라인

'BL<1>', 'BL<2>' 및 'BL<3>'과, 비트라인바 'BLB<1>', 'BLB<2>' 및 'BLB<3>'의 전압을 방전(Discharge) 시키고, 워드라인(WL)에 인가되는 전압을 전원전압(VDD) 레벨로 증가시키는 동작을 통해 라이트 성능(Write ability)을 향상시킬 수 있다.

- [0122] 보다 구체적으로, 322 내지 323 구간에서 워드라인 드라이버(313)는 워드라인(WL)에 전압을 인가하여 비선택된 컬럼에 구비된 복수의 메모리 셀 각각의 더미 리드(Dummy Read) 동작을 제어함으로써, 프리차지된 비트라인 'BL<1>', 'BL<2>' 및 'BL<3>'과, 프리차지된 비트라인바 'BLB<1>', 'BLB<2>' 및 'BLB<3>'의 전압을 방전 시킬수 있다.

- [0123] 또한, 323 구간에서 워드라인 드라이버(313)는 프리차지된 비트라인 'BL<1>', 'BL<2>' 및 'BL<3>'과, 프리차지된 비트라인 'BL=1>', 'BL=2>' 및 'BL=3>'의 전압이 방전되면, Low 레벨의 반전된 언더 드라이브 제어신호 '/UD'를 수신하여 언더 드라이브 트랜지스터 'NO'를 턴오프(Turn-off) 상태로 제어할 수 있다.

- [0124] 즉, 323 구간에서 워드라인 드라이버(313)는 언더 드라이브 트랜지스터 'NO'를 턴오프(Turn-off) 상태로 제어하여 언더 드라이브 동작이 정지 되도록 함으로써, 워드라인(WL)에 전원전압(VDD) 레벨의 전압을 인가할 수 있다.

- [0125] 다음으로, 324 구간에서 일실시예에 따른 정적 메모리 장치(310)는 워드라인(WL)을 플로팅(Floating) 상태로 제어하고, 방전된 비트라인 'BL<1>', 'BL<2>' 및 'BL<3>'과, 방전된 비트라인바 'BLB<1>', 'BLB<2>' 및 'BLS<3>'과, 방전된 비트라인바 'BLB<1>', 'BLB<2>' 및 'BLB <3>'를 다시 프리차지하여, 기생 캐패시턴스 성분(314)을 통해 플로팅된 워드라인(WL)을 부스팅(Boosting)함으로써, 워드라인(WL) 전압의 추가적인 상승을 통해 라이트 성능(Write ability)을 추가적으로 향상 시킬 수있다.

- [0126] 참조부호 310에서 기생 캐패시턴스 성분(314)은 비선택된 컬럼에 구비되는 비트라인 BL<1>, BL<2> 및 BL<3>과 워드라인(WL) 사이에만 도시되어 있으나, 기생 캐패시턴스 성분(314)은 비선택된 컬럼에 구비되는 비트라인 BLB<1>, BLB<2> 및 BLB<3>와 워드라인(WL) 사이에도 형성될 수 있다.

- [0127] 보다 구체적으로, 324 구간에서 워드라인 드라이버(313)는 High 레벨의 플로팅 제어신호 'BST'를 수신하여 플로팅 제어 트랜지스터 'PO'를 턴오프 상태로 제어함으로써, 워드라인(WL)을 플로팅 시킬 수 있다.

- [0128] 또한, 324 구간에서 인터리브 프리차지 회로(312)는 Low 레벨의 비선택된 컬럼의 프리차지 제어 신호 'PC<1: 3>'를 수신하여, 비트라인 'BL<1>', 'BL<2>' 및 'BL<3>'과, 비트라인바 'BLB<1>', 'BLB<2>' 및 'BLB<3>'에 대한 프리차지 동작을 재 수행할 수 있다.

- [0129] 일측에 따르면, 일실시예에 따른 정적 메모리 장치(310)는 프리차지 전압 'V<sub>PC</sub>' 레벨과 324 구간의 타이밍 조절을 통해, 비선택된 컬럼의 비트라인에 인가되는 신호 'BL<1:3>' 및 비선택된 컬럼의 비트라인바에 인가되는 신호 'BLB<1:3>'의 상승으로 인한 리드 안정성(Read stability)의 영향력을 제어할 수 있다.

- [0130] 다음으로, 325 구간에서 일실시예에 따른 정적 메모리 장치(310)는 워드라인(WL)에 인가되는 전압을 감소시킬 수 있다.

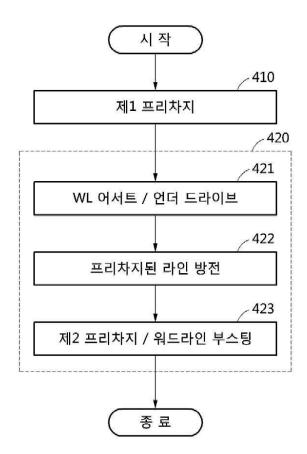

- [0132] 도 4는 일실시예에 따른 정적 메모리 장치의 제어방법을 설명하기 위한 도면이다.

- [0133] 다시 말해, 도 4는 도 1 내지 도 3b를 통해 설명한 일실시예에 따른 정적 메모리 장치의 제어방법에 관한 것으로서, 이후 도 4를 통해 설명하는 내용 중 일실시예에 따른 정적 메모리 장치에서 설명한 내용과 중복되는 설명은 생략하기로 한다.

- [0134] 도 4를 참조하면, 410단계에서 일실시예에 따른 정적 메모리 장치의 제어방법은 인터리브 프리차지 회로에서 복수의 로우(Row)와 복수의 컬럼(Column)이 교차하는 셀 어레이에 구비된 복수의 컬럼 중에서 비선택된 컬럼 (Unselected column)에 구비되는 비트라인과 비트라인바 중에서 적어도 하나의 라인을 프리차지할 수 있다.

- [0135] 일측에 따르면, 410단계에서 일실시예에 따른 정적 메모리 장치의 제어방법은 인터리브 프리차지 회로에서 복수의 컬럼 중 선택된 컬럼에 구비되는 비트라인과 비트라인바 중에서 적어도 하나의 라인과, 비선택된 컬럼에 구비되는 비트라인과 비트라인과 비트라인과 하나의 라인을 동시에 프리차지하는 제1 프리차지 동작을 수행할수 있다.

- [0136] 다음으로, 420단계에서 일실시예에 따른 정적 메모리 장치의 제어방법은 워드라인 드라이버에서 셀 어레이에 구비된 복수의 메모리 셀 중에서 비선택된 컬럼에 구비된 복수의 메모리 셀 각각에 연결되는 적어도 하나의 워드

라인을 플로팅(Floating) 상태로 제어하여, 플로팅된 워드 라인과 비선택된 컬럼에 구비되는 프리차지된 라인 사이에 형성되는 기생 캐패시턴스(Parasitic capacitance) 성분을 통해 플로팅된 워드 라인을 부스팅(Boostin g)할 수 있다.

- [0137] 보다 구체적으로, 421단계에서 일실시예에 따른 정적 메모리 장치의 제어방법은 적어도 하나의 워드라인에 어서 트하고, 어서트된 워드라인에 대해 언더 드라이브(Under Drive) 동작을 수행할 수 있다.

- [0138] 다음으로, 422단계에서 일실시예에 따른 정적 메모리 장치의 제어방법은 워드라인 드라이버에서 비선택된 컬럼 에 구비된 복수의 메모리 셀 각각의 더미 리드(Dummy Read) 동작을 수행하여, 프리차지된 라인을 방전 (Discharge) 시킬 수 있다.

- [0139] 다음으로, 423단계에서 일실시예에 따른 정적 메모리 장치의 제어방법은 워드라인 드라이버에서 비선택된 컬럼에 구비된 복수의 메모리 셀 각각에 연결되는 적어도 하나의 워드 라인을 플로팅 상태로 제어하고, 인터리브 프리차지 회로에서 비선택된 컬럼에 구비되는 방전된 라인을 다시 프리차지하는 제2 프리차지 동작을 수행하여 플로팅된 워드라인과 제2 프리차지 동작으로 프리차지된 라인 사이에 형성되는 기생 캐패시턴스 성분을 통해 플로팅된 워드 라인을 부스팅할 수 있다.

- [0141] 결국, 본 발명을 이용하면, 추가적인 캐패시터 없이 워드라인과 프리차지된 비트라인 사이에 형성되는 기생 캐패시턴스 성분을 통해 워드라인을 부스팅함으로써, 장치의 크기 감소와 함께 라이트 특성(Write ability) 또한 향상시킬 수 있다.

- [0142] 또한, 본 발명은 리드 및 라이트 포트가 동일한 비트-인터리브 구조의 6T-SRAM 소자에서 비선택된 컬럼에 구비된 비트라인 전압의 상승을 통해, 워드라인을 용이하게 부스팅할 수 있다.

- [0143] 또한, 본 발명은 비선택된 컬럼에 구비된 비트라인 전압의 상승을 통해 워드라인을 부스팅함으로써, 라이트 특성뿐만 아니라 리드 안정성을 향상시킬 수 있다.

- [0145] 이상에서 설명된 장치는 하드웨어 구성요소, 소프트웨어 구성요소, 및/또는 하드웨어 구성요소 및 소프트웨어 구성요소의 조합으로 구현될 수 있다. 예를 들어, 실시예들에서 설명된 장치 및 구성요소는, 예를 들어, 프로세서, 콘트롤러, ALU(arithmetic logic unit), 디지털 신호 프로세서(digital signal processor), 마이크로컴퓨터, FPGA(field programmable gate array), PLU(programmable logic unit), 마이크로프로세서, 또는 명령 (instruction)을 실행하고 응답할 수 있는 다른 어떠한 장치와 같이, 하나 이상의 범용 컴퓨터 또는 특수 목적컴퓨터를 이용하여 구현될 수 있다. 처리 장치는 운영 체제(OS) 및 상기 운영 체제 상에서 수행되는 하나 이상의 소프트웨어 애플리케이션을 수행할 수 있다. 또한, 처리 장치는 소프트웨어의 실행에 응답하여, 데이터를접근, 저장, 조작, 처리 및 생성할 수도 있다. 이해의 편의를 위하여, 처리 장치는 하나가 사용되는 것으로 설명된 경우도 있지만, 해당 기술분야에서 통상의 지식을 가진 자는, 처리 장치가 복수 개의 처리 요소 (processing element) 및/또는 복수 유형의 처리 요소를 포함할 수 있음을 알 수 있다. 예를 들어, 처리 장치는 복수 개의 프로세서 또는 하나의 프로세서 및 하나의 콘트롤러를 포함할 수 있다. 또한, 병렬 프로세서 (parallel processor)와 같은, 다른 처리 구성(processing configuration)도 가능하다.

- [0146] 이상과 같이 실시예들이 비록 한정된 도면에 의해 설명되었으나, 해당 기술분야에서 통상의 지식을 가진 자라면 상기의 기재로부터 다양한 수정 및 변형이 가능하다. 예를 들어, 설명된 기술들이 설명된 방법과 다른 순서로 수행되거나, 및/또는 설명된 시스템, 구조, 장치, 회로 등의 구성요소들이 설명된 방법과 다른 형태로 결합 또는 조합되거나, 다른 구성요소 또는 균등물에 의하여 대치되거나 치환되더라도 적절한 결과가 달성될 수 있다.

- [0147] 그러므로, 다른 구현들, 다른 실시예들 및 특허청구범위와 균등한 것들도 후술하는 특허청구범위의 범위에 속한다.

#### 부호의 설명

[0148] 100: 정적 메모리 장치 110: 메모리 셀

120: 인터리브 프리차지 회로 130: 워드라인 드라이버

## 도면

## 도면1

## 도면2

## 도면3a

## 도면3b

## 도면4