2020년12월02일

## (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

**HO3K 19/18** (2006.01) **HO1L 43/02** (2006.01) **HO3K 19/23** (2006.01)

(52) CPC특허분류

**H03K 19/18** (2013.01) **H01L 43/02** (2013.01)

(21) 출원번호 **10-2020-0021311**

(22) 출원일자 **2020년02월20일** 심사청구일자 **2020년02월20일**

(30) 우선권주장

1020190061279 2019년05월24일 대한민국(KR)

(11) 공개번호 10-2020-0135149

(71) 출원인

(43) 공개일자

한양대학교 에리카산학협력단

경기도 안산시 상록구 한양대학로 55

연세대학교 산학협력단

서울특별시 서대문구 연세로 50 (신촌동, 연세대 학교)

(72) 발명자

오새룬터

경기도 안산시 상록구 한양대학로 55, 제3공학관 408호

홍종일

서울특별시 서대문구 연세로 50 연세대학교, 제2 공학관 311호

(74) 대리인

정병훈

전체 청구항 수 : 총 12 항

(54) 발명의 명칭 **스핀 로직 소자 및 이의 동작 방법**

#### (57) 요 약

본 발명은 스핀 로직 소자 및 이의 동작 방법에 관한 것으로, 특히, 일반적인 유전체 커패시터와 추가 트랜지스터를 이용해 동작할 수 있는 스핀 로직 소자 및 이의 동작 방법에 관한 것이다. 본 발명의 실시 예에 따른 스핀로직 소자는 자성체층, 상기 자성체층의 일면 상에 형성된 전류전달층, 상기 자성체층의 상기 일면 상에 상기 전류전달층과 이격되어 형성된 스핀 주입층 및 상기 스핀 주입층 상에 형성된 스핀-전하 변환층을 포함한다.

#### 대 표 도 - 도1

#### (52) CPC특허분류

**HO3K 19/23** (2013.01)

이 발명을 지원한 국가연구개발사업

과제고유번호 2018R1D1A1B07043334

부처명 교육부 과제관리(전문)기관명 한국연구재단

연구사업명 이공학 개인기초연구지원사업

연구과제명 IoT 센서용 시각신경회로모사 포토시냅스 소자를 적용한 적응형 학습 플랫폼 개발

기 여 율 40/100

과제수행기관명 한양대학교 에리카산학협력단 연구기간 2018.06.01 ~ 2021.05.31

이 발명을 지원한 국가연구개발사업

과제고유번호 10067739 부처명 산업통상자원부

과제관리(전문)기관명 한국산업기술평가관리원

연구사업명 산업기술혁신사업 / 산업핵심기술개발사업 / 전자정보디바이스산업원천기술개발사업

연구과제명 5nm 급 이하 차세대 Logic 소자 원천요소기술개발

기 여 율 30/100

과제수행기관명 한양대학교 에리카산학협력단 연구기간 2016.10.01 ~ 2021.09.30

이 발명을 지원한 국가연구개발사업

과제고유번호 2019R1A2C2002960 부처명 과학기술정보통신부

과제관리(전문)기관명 한국연구재단 연구사업명 중견연구자지원사업

연구과제명 수소화그래핀 진성반도체를 이용한 탄소 전자/스핀 소자

기 여 율 30/100

과제수행기관명 연세대학교 산학협력단 연구기간 2019.03.01 ~ 2023.02.28

### 명 세 서

#### 청구범위

#### 청구항 1

자성체층;

상기 자성체층의 일면 상에 형성된 전류전달층;

상기 자성체층의 상기 일면 상에 상기 전류전달층과 이격되어 형성된 스핀 주입층; 및

상기 스핀 주입층 상에 형성된 스핀-전하 변환층을 포함하는 스핀 로직 소자.

#### 청구항 2

제1항에 있어서,

상기 자성체층은 상기 전류전달층을 통해 흐르는 전류에 의해 자화 방향이 스위칭되는 스핀 로직 소자.

#### 청구항 3

제2항에 있어서,

상기 전류는 전류 공급부로부터 공급되며,

상기 전류 공급부는,

입력 노드와 접지 사이에 접속되는 커패시터; 및

게이트 전극이 상기 입력 노드에 접속되고, 제1 전극이 종속 전원에 접속되며, 제2 전극이 상기 전류전달층의 일단에 접속되는 트랜지스터를 포함하는 스핀 로직 소자.

#### 청구항 4

제3항에 있어서,

상기 종속 전원은 상기 커페시터의 양단 전압의 극성에 대응하는 전원을 공급하는 스핀 로직 소자.

#### 청구항 5

제3항에 있어서,

상기 전류전달층의 타단은 접지에 접속되는 스핀 로직 소자.

#### 청구항 6

제1항에 있어서,

상기 전류전달층은,

중금속 및 위상절연체 중에서 적어도 하나를 포함하는 스핀 로직 소자.

#### 청구항 7

제1항에 있어서,

상기 스핀 주입층은,

상기 자성체층의 상기 자화 방향에 따라 결정되는 스핀 전류를 스핀 필터로서 상기 스핀-전하 변환층에 주입하는 스핀 로직 소자.

#### 청구항 8

제1항에 있어서,

상기 스핀-전하 변환층은,

상기 스핀 주입층으로부터 주입받은 상기 스핀 전류를 전하 전류로 변환하여 출력 전류로서 출력하는 스핀 로직 소자.

#### 청구항 9

입력 노드를 통해 공급되는 전류에 의해 커패시터를 충전하는 단계;

상기 커패시터의 양단 전압의 극성에 대응하는 방향으로 전류전달층을 통해 전류를 공급하는 단계;

상기 전류의 상기 방향에 의해 자성체층의 자화 방향을 스위칭하는 단계;

상기 자성체층의 상기 자화 방향에 따라 결정되는 스핀 전류를 스핀-전하 변환층에 주입하는 단계; 및

상기 스핀 전류를 전하 전류로 변환하여 출력 전류로서 출력하는 단계를 포함하는 스핀 로직 소자의 동작 방법.

#### 청구항 10

제9항에 있어서,

상기 전류전달층은 상기 자성체층의 일면 상에 형성되고,

상기 스핀 주입층은 상기 자성체층의 상기 일면 상에 상기 전류전달층과 이격되어 형성되며,

상기 스핀-전하 변환층은 상기 스핀 주입층 상에 형성되는 스핀 로직 소자의 동작 방법.

#### 청구항 11

제10항에 있어서,

상기 전류전달층은,

중금속 및 위상절연체 중에서 적어도 하나를 포함하는 스핀 로직 소자의 동작 방법.

#### 청구항 12

제10항에 있어서,

상기 스핀 주입층은 스핀 필터로서 동작하는 스핀 로직 소자의 동작 방법.

#### 발명의 설명

#### 기 술 분 야

[0001] 본 발명은 스핀 로직 소자 및 이의 동작 방법에 관한 것으로, 특히, 일반적인 유전체 커패시터와 추가 트랜지스 터를 이용해 동작할 수 있는 스핀 로직 소자 및 이의 동작 방법에 관한 것이다.

#### 배경기술

- [0002] 2016년 C. Murapaka et. al에서는 수직/수평 나노선에 입력 신호를 인가하고 상부에 별도 자성 게이트를 이용하여 로직 함수를 선택하는 방식을 제안하였다(Sci. Rep. 6, 20130 (2016) 참조). 입력 신호가 전류 신호 또는 전압 신호가 아닌 자기 신호이며, 자구벽 이동 방식을 사용하였다.

- [0003] 2017년 M. G. Mankalale et. al.에서는 전압기반 스위칭 및 자구벽 이동을 통한 로직을 구현하였다(IEEE J. Explore. Solid-State Comput. Devices Circuits 3, 27 (2017) 참조). 이는 듀얼-레일(dual-rail) CMOS 인버터 를 포함하고 4개 제어 신호를 사용한다. 간단한 인버터의 기능을 수행하기 위해 회로에 CMOS 인버터를 포함하고 있어 CMOS 인버터 대비 이점이 적으며, 재구성 가능 로직 구현이 어렵다.

- [0004] 2019년 N. Rangarajan et. al.에서는 스핀 홀(spin hall) 효과와 자기 쌍극자 결합(magnetic dipole coupling) 기반의 단위소자와 자기터널접합을 이용하여 블리언(Boolean) 함수를 구현하였다. MUX를 이용하여 로직 함수를 선택할 수 있지만, 수평(lateral) 구조와 쌍극자 결합(dipolar coupling) 구현이 실제 공정상 용이하지 않다.

- [0005] 스핀 로직소자에 대한 연구는 전 세계적으로 여러 가지 구조에 대한 제안이 되고 있지만, CMOS 기반 소자의 특성을 뛰어넘을 수 있는 수준의 결과는 나타나지 않았다.

- [0006] 하지만, 2019년에 Intel社에서 이론적으로 제안한 MESO(magnetoelectric spin-orbit) 소자는 CMOS 기반 소자와 비교하여도 손색 없는 저전력 스핀 로직소자로 구현이 가능할 것으로 예상된다(Nature 565, 35 (2019) 참조).

- [0007] 종래의 재구성 가능 스핀 로직은 자기(magnetic) 신호를 이용하거나 증착 온도가 높아 반도체 양산 공정에 용이하지 않은 단결정 다강체(multi-ferroic: 강자성 + 강유전 특성을 동시에 가짐) 재료를 이용한 자기전기 (magnetoelectric) 효과를 기반으로 하고 있다. 또한, 단위 소자가 이론 및 개념 수준에 머물러 있기 때문에 반도체 양산공정 호환성 및 실험적 소자 검증이 안된 상태이다. 저전력, 고 면적 효율 응용분야에 사용되기 위해전압제어 자화스위칭 및 스핀-전하 변환을 이용한 인버터/버퍼/NAND/NOR 등의 블리언(Boolean) 함수를 실시간으로 재구성할 수 있는 회로가 요구된다.

- [0008] 종래의 MESO 구조는 다강체(multi-ferroic)/강자성체간의 자기-전기 결합(magneto-electric coupling)과 스핀 간의 교환 결합(exchange coupling)을 이용하여 스핀을 스위칭 시킨다.

- [0009] 이론적으로 훌륭한 개념이지만 종래의 MESO 구조는 섭씨 600도 이상의 고온에서 성장시킨 단결정 기판위에서 이루어진 결과로 트랜지스터와 강자성체가 집적된 백-엔드(back-end) 공정에서 사용될 수 없다. 또한, 종래의 MESO 구조는 스위칭 시 발생되는 스트레인으로 피로현상이 일어나 로직 소자의 내구성(endurance)을 보장할 수 없다. 더하여, 종래의 MESO 구조에서는 스핀-전하 변환층의 부호가 하나로 정해져 있어 인버터로만 쓰이며 버퍼는 만들 수 없다.

#### 발명의 내용

#### 해결하려는 과제

[0010] 본 발명이 이루고자 하는 기술적인 과제는 일반적인 유전체 커패시터와 추가 트랜지스터를 이용해 동작할 수 있는 스핀 로직 소자 및 이의 동작 방법을 제공하는 것이다.

#### 과제의 해결 수단

- [0011] 본 발명의 실시 예에 따른 스핀 로직 소자는 자성체충, 상기 자성체충의 일면 상에 형성된 전류전달충, 상기 자성체충의 상기 일면 상에 상기 전류전달충과 이격되어 형성된 스핀 주입충 및 상기 스핀 주입충 상에 형성된 스핀-전하 변환충을 포함한다.

- [0012] 실시 예에 따라, 상기 자성체층은 상기 전류전달층을 통해 흐르는 전류에 의해 자화 방향이 스위칭될 수 있다.

- [0013] 실시 예에 따라, 상기 전류는 전류 공급부로부터 공급되며, 상기 전류 공급부는 입력 노드와 접지 사이에 접속되는 커패시터 및 게이트 전극이 상기 입력 노드에 접속되고, 제1 전극이 종속 전원에 접속되며, 제2 전극이 상기 전류전달층의 일단에 접속되는 트랜지스터를 포함할 수 있다.

- [0014] 실시 예에 따라, 상기 종속 전원은 상기 커패시터의 양단 전압의 극성에 대응하는 전원을 공급할 수 있다.

- [0015] 실시 예에 따라, 상기 전류전달층의 타단은 접지에 접속될 수 있다.

- [0016] 상기 전류전달층은 중금속 및 위상절연체 중에서 적어도 하나를 포함할 수 있다.

- [0017] 상기 스핀 주입층은 상기 자성체층의 상기 자화 방향에 따라 결정되는 스핀 전류를 스핀 필터로서 상기 스핀-전 하 변환층에 주입할 수 있다.

- [0018] 실시 예에 따라, 상기 스핀-전하 변환층은 상기 스핀 주입층으로부터 주입받은 상기 스핀 전류를 전하 전류로 변환하여 출력 전류로서 출력할 수 있다.

- [0019] 본 발명의 실시 예에 따른 스핀 로직 소자의 동작 방법은 입력 노드를 통해 공급되는 전류에 의해 커패시터를 충전하는 단계, 상기 커패시터의 양단 전압의 극성에 대응하는 방향으로 전류전달층을 통해 전류를 공급하는 단계, 상기 전류의 상기 방향에 의해 자성체층의 자화 방향을 스위칭하는 단계, 상기 자성체층의 상기 자화 방향에 따라 결정되는 스핀 전류를 스핀-전하 변환층에 주입하는 단계 및 상기 스핀 전류를 전하 전류로 변환하여 출력 전류로서 출력하는 단계를 포함한다.

- [0020] 실시 예에 따라, 상기 전류전달층은 상기 자성체층의 일면 상에 형성되고, 상기 스핀 주입층은 상기 자성체층의

상기 일면 상에 상기 전류전달층과 이격되어 형성되며, 상기 스핀-전하 변환층은 상기 스핀 주입층 상에 형성될 수 있다.

- [0021] 실시 예에 따라, 상기 전류전달층은 중금속 및 위상절연체 중에서 적어도 하나를 포함할 수 있다.

- [0022] 실시 예에 따라, 상기 스핀 주입층은 스핀 필터로서 동작할 수 있다.

#### 발명의 효과

- [0023] 본 발명의 실시 예에 따른 스핀 로직 소자 및 이의 동작 방법은 일반적인 유전체 커패시터와 추가 트랜지스터를 이용해 동작할 수 있다.

- [0024] 본 발명의 실시 예에 따른 스핀 로직 소자는 종래의 반도체 공정(실리콘 기반 공정)을 이용해 제조될 수 있다.

- [0025] 종래의 소자들은 강자성 재료와 자화 스위칭을 위해 전류 신호를 이용하지만, 본 발명의 실시 예에 따른 스핀 로직 소자는 유전체 커패시터에 걸리는 전압 신호를 이용해 제어할 수 있다.

- [0026] 본 발명의 실시 예에 따른 스핀 로직 소자는 전력 소모가 적고, 면적 효율이 높으며, 실시간 회로 재구성이 가능하다.

#### 도면의 간단한 설명

- [0027] 본 발명의 상세한 설명에서 인용되는 도면을 보다 충분히 이해하기 위하여 각 도면의 상세한 설명이 제공된다.

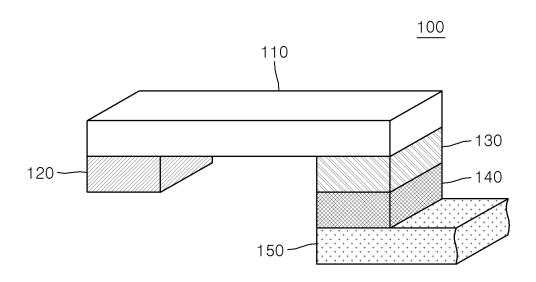

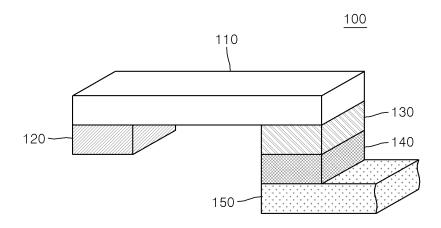

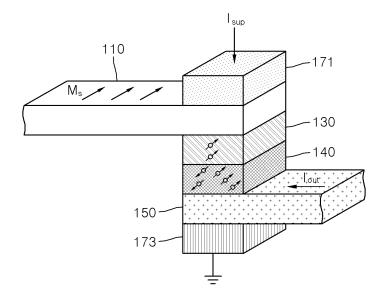

- 도 1은 본 발명의 실시 예에 따른 스핀 로직 소자를 나타내는 모식도이다.

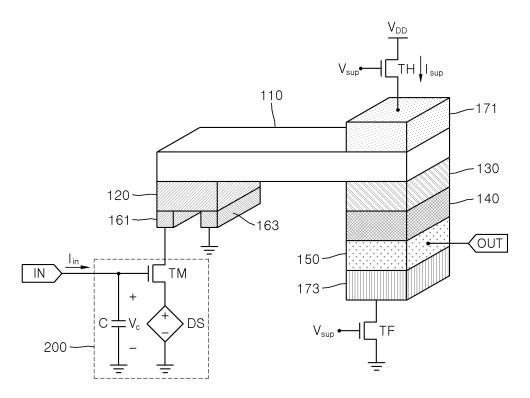

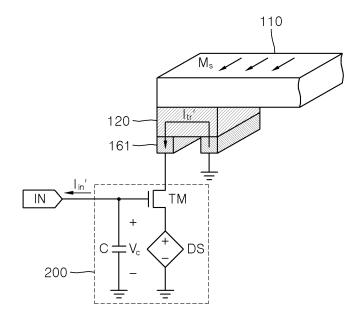

- 도 2는 도 1에 도시된 스핀 로직 소자와 관련 회로의 연결 관계를 상세하게 나타내는 도면이다.

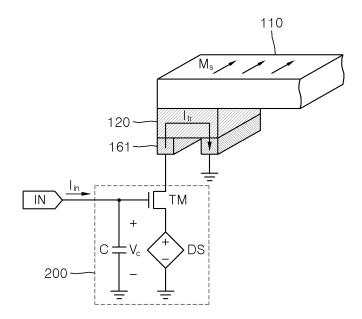

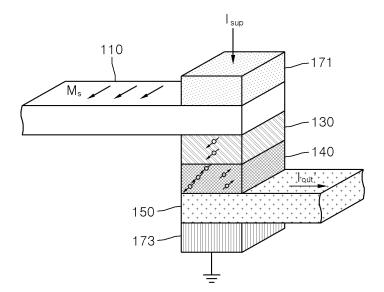

- 도 3은 입력 전류에 대응하여 자성체층의 자화 방향이 스위칭되는 과정의 일례를 나타내는 도면이다.

- 도 4는 자성체의 자화 방향에 따라 출력 전류가 발생하는 과정의 일례를 나타내는 도면이다.

- 도 5는 입력 전류에 대응하여 자성체층의 자화 방향이 스위칭되는 과정의 다른 예를 나타내는 도면이다.

- 도 6은 자성체의 자화 방향에 따라 출력 전류가 발생하는 과정의 다른 예를 나타내는 도면이다.

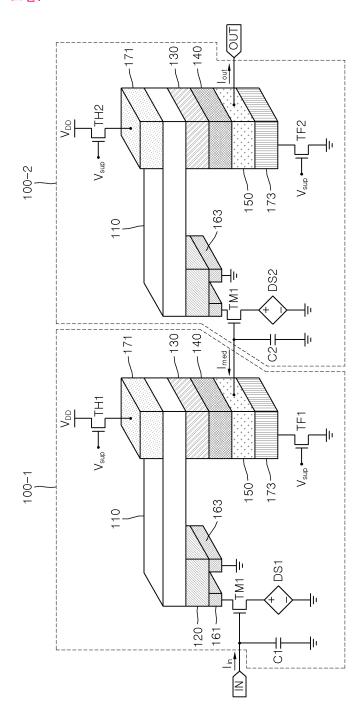

- 도 7은 도 1에 도시된 스핀 로직 소자를 이용해 구성된 버퍼를 나타내는 도면이다.

- 도 8은 본 발명의 실시 예에 따른 스핀 로직 소자의 동작을 나타내는 순서도이다.

- 도 9는 본 발명의 실시 예에 따른 스핀 로직 소자를 이용해 구현될 수 있는 다수결 게이트를 설명하기 위한 도면이다.

- 도 10은 본 발명의 실시 예에 따른 스핀 로직 소자를 이용해 구현될 수 있는 반전 다수결 게이트를 설명하기 위한 도면이다.

- 도 11은 본 발명의 실시 예에 따른 스핀 로직 소자를 이용해 구현될 수 있는 1-비트 가산기(1-bit adder)를 설명하기 위한 도면이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0028] 본 명세서에 개시되어 있는 본 발명의 개념에 따른 실시 예들에 대해서 특정한 구조적 또는 기능적 설명들은 단지 본 발명의 개념에 따른 실시 예들을 설명하기 위한 목적으로 예시된 것으로서, 본 발명의 개념에 따른 실시 예들은 다양한 형태들로 실시될 수 있으며 본 명세서에 설명된 실시 예들에 한정되지 않는다.

- [0029] 본 발명의 개념에 따른 실시 예들은 다양한 변경들을 가할 수 있고 여러 가지 형태들을 가질 수 있으므로 실시 예들을 도면에 예시하고 본 명세서에 상세하게 설명하고자 한다. 그러나, 이는 본 발명의 개념에 따른 실시 예들을 특정한 개시 형태들에 대해 한정하려는 것이 아니며, 본 발명의 사상 및 기술 범위에 포함되는 모든 변경, 균등물, 또는 대체물을 포함한다.

- [0030] 제1 또는 제2 등의 용어는 다양한 구성 요소들을 설명하는데 사용될 수 있지만, 상기 구성 요소들은 상기 용어들에 의해 한정되어서는 안 된다. 상기 용어들은 하나의 구성 요소를 다른 구성 요소로부터 구별하는 목적으로 만, 예컨대 본 발명의 개념에 따른 권리 범위로부터 이탈되지 않은 채, 제1구성요소는 제2구성요소로 명명될 수

있고, 유사하게 제2구성요소는 제1구성요소로도 명명될 수 있다.

- [0031] 어떤 구성요소가 다른 구성요소에 "연결되어" 있다거나 "접속되어" 있다고 언급된 때에는, 그 다른 구성요소에 직접적으로 연결되어 있거나 또는 접속되어 있을 수도 있지만, 중간에 다른 구성요소가 존재할 수도 있다고 이 해되어야 할 것이다. 반면에, 어떤 구성요소가 다른 구성요소에 "직접 연결되어" 있다거나 "직접 접속되어" 있다고 언급된 때에는, 중간에 다른 구성요소가 존재하지 않는 것으로 이해되어야 할 것이다. 구성요소들 간의 관계를 설명하는 다른 표현들, 즉 "~사이에"와 "바로 ~사이에" 또는 "~에 이웃하는"과 "~에 직접 이웃하는" 등도 마찬가지로 해석되어야 한다.

- [0032] 본 명세서에서 사용한 용어는 단지 특정한 실시 예를 설명하기 위해 사용된 것으로, 본 발명을 한정하려는 의도 가 아니다. 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다. 본 명세서에서, "포함하다" 또는 "가지다" 등의 용어는 설시된 특징, 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것이 존재함을 지정하려는 것이지, 하나 또는 그 이상의 다른 특징들이나 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것들의 존재 또는 부가 가능성을 미리 배제하지 않는 것으로 이해되어야 한다.

- [0033] 다르게 정의되지 않는 한, 기술적이거나 과학적인 용어를 포함해서 여기서 사용되는 모든 용어들은 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에 의해 일반적으로 이해되는 것과 동일한 의미를 가진다. 일반적으로 사용되는 사전에 정의되어 있는 것과 같은 용어들은 관련 기술의 문맥상 가지는 의미와 일치하는 의미를 갖는 것으로 해석되어야 하며, 본 명세서에서 명백하게 정의하지 않는 한, 이상적이거나 과도하게 형식적인 의미로 해석되지 않는다.

- [0034] 이하, 첨부한 도면을 참조하여 본 발명의 바람직한 실시 예를 설명함으로써, 본 발명을 상세히 설명한다.

- [0035] 도 1은 본 발명의 실시 예에 따른 스핀 로직 소자를 나타내는 모식도이다.

- [0036] 도 1을 참조하면, 스핀 로직 소자(100)는 자성체충(110), 전류전달충(120), 스핀 주입충(130), 스핀-전하 변환 충(140) 및 전류출력충(150)을 포함한다.

- [0037] 자성체층(110)은 초기에 임의의 자화 방향을 가질 수 있다.

- [0038] 자성체층(110)은 전류전달층(120)을 통해 흐르는 전류에 의해 자화 방향이 스위칭될 수 있다. 구체적으로, 자성 체층(110)은 전류전달층(120)을 통해 흐르는 전류에 의해 생성되는 스핀 전류 또는 스핀-궤도 토크에 의하여 자화 방향이 스위칭될 수 있다.

- [0039] 자성체층(110)은 강자성체(ferromagnet)로 형성되는 것이 바람직하다.

- [0040] 전류전달층(120)은 자성체층(110)의 일면 상에 형성되되, 스핀 주입층(130)과 이격되도록 형성될 수 있다.

- [0041] 전류전달층(120)은 전류 공급부(200)로부터 공급되는 전류를 접지로 흐르게 한다. 이때, 전류전달층(120)은 전류 공급부(200)로부터 공급되는 전류의 방향에 대응하는 자기장을 유도함으로써 자성체층(110)의 자화 방향을 스위칭할 수 있다.

- [0042] 전류전달층(120)은 스핀 홀 각도(spin hall angle)가 큰 중금속 또는 위상절연체로 형성되는 것이 바람직하다.

- [0043] 스핀 주입층(spin injection layer, 130)은 자성체층(110)의 상기 일면 상에 형성되되, 전류전달층(120)과 이 격되도록 형성될 수 있다.

- [0044] 스핀 주입층(130)은 자성체층(110)으로부터 스핀전류를 주입받을 수 있다. 구체적으로, 스핀 주입층(130)은 스핀 필터로서 자성체층(110)의 자화 방향에 대응하는 방향을 갖는 스핀 전류를 통과시킨다.

- [0045] 스핀 주입층(130)은 MgO 기반의 절연층으로 형성될 수 있다.

- [0046] 스핀-전하 변환층(spin-charge conversion layer, 140)은 스핀 주입층(130) 상에 형성될 수 있다.

- [0047] 스핀-전하 변환층(140)은 스핀 주입층(130)을 통해 주입된 스핀전류를 전하전류로 변환하여 출력할 수 있다. 구체적으로, 스핀-전하 변환층(140)은 스핀 궤도 상호 작용(spin orbit interaction) 등을 통해 스핀 주입층 (120)을 통과한 스핀 전류를 전하전류로 변환한다.

- [0048] 전류출력층(150)은 스핀-전하 변환층(140) 상에 형성될 수 있다.

- [0049] 전류출력층(150)은 스핀-전하 변환층(140)에 의해 변환된 전하전류를 출력한다.

- [0050] 전류출력층(150)은 전하전류가 흐를 수 있는 소재로 형성될 수 잇다.

- [0051] 도 1에 도시되어 있지는 않으나, 자성체층(110)과 스핀 주입층(130) 사이에 인공반강자성체가 구비될 수 있다. 인공반강자성체가 구비하면, 전류출력층(150)을 통해 흐르는 전하전류의 방향을 반전시킬 수 있다.

- [0052] 즉, 인공반강자성체의 구비 여부에 따라 스핀 로직 소자(100)를 인버터 또는 버퍼로 구현할 수 있다.

- [0053] 예를 들어, 인공반강자성체는 Ruderman-Kittle-Kasuya-Yosida 결합에 의해 자성층/비자성층/자성층 구조에서 두 개의 자성층의 자화가 반대로 정렬되는 인공구조로 구현될 수 있다.

- [0054] 도 2는 도 1에 도시된 스핀 로직 소자와 관련 회로의 연결 관계를 상세하게 나타내는 도면이다.

- [0055] 도 2를 참조하면, 전류전달층(120)은 전극(161)을 통해 전류공급부(200)에 접속되고, 전극(163)을 통해 접지에 접속될 수 있다.

- [0056] 전류공급부(200)는 입력 노드(IN)를 통해 공급되는 입력 전류(I<sub>in</sub>)에 대응하는 전류를 전극(161)을 통해 전류전 달층(120)으로 공급할 수 있다.

- [0057] 실시 예에 따라, 전류공급부(200)는 입력 전류(I<sub>in</sub>)의 방향과 동일한 방향의 전류를 전류전달층(120)으로 공급할 수 있다.

- [0058] 전류 공급부(200)는 커패시터(C), 종속 전원(DS) 및 전달 트랜지스터(TM)를 포함할 수 있다.

- [0059] 커패시터(C)는 입력 노드(IN)로부터 공급되는 입력 전류( $I_{in}$ )를 충전한다. 즉, 커패시터(C)는 입력 전류( $I_{in}$ )에 대응하는 전압( $V_{C}$ )을 저장한다.

- [0060] 종속 전원(DS)은 커패시터(C)에 저장된 전압(Vc)에 따라 결정되는 전원을 공급한다.

- [0061] 예를 들어, 전압(Vc)이 충전되어 있을 때, 즉, 양(positive)일 때, 종속 전원(DS)은 양의 전압을 갖는 전원으로 동작할 수 있다. 반대로, 전압(Vc)이 방전되어 있을 때, 종속 전원(DS)은 음의 전압을 갖는 전원으로 동작할 수 있다.

- [0062] 다른 예를 들어, 전압(Vc)이 소정의 기준 전압 이상일 때 종속 전원(DS)은 양의 전압을 갖는 전원으로 동작하고, 전압(Vc)이 소정의 기준 전압 미만일 때 종속 전원(DS)은 음의 전압을 갖는 전원으로 동작할 수 있다.

- [0063] 도 2에 도시된 전류공급부(200)의 구조는 단순한 예시일 뿐이며, 다양한 형태로 구현될 수 있다. 다시 말해, 전류공급부(200)는 Bi-directional current amplifier의 기능을 갖는 다양한 구조로 구현될 수 있다.

- [0064] 전달 트랜지스터(TM)의 게이트 전극은 입력 노드(IN)에 접속되고, 제1 전극은 종속 전원(DS)에 접속되며, 제2 전극은 전극(161)에 접속될 수 있다.

- [0065] 전달 트랜지스터(TM)는 종속 전원(DS)의 출력 전압에 대응하는 전류를 전극(161)으로 공급할 수 있다. 상기 전류는 전극(161)과 전류전달층(120), 전극(163)을 통해 접지로 흐를 수 있다.

- [0066] 전류전달층(120)을 통해 전류가 흐르면, 전류전달층(120)에서 스핀-홀 효과(spin hall errect) 또는 라쉬바 효과(Rashba effect)에 의해 생성되는 스핀 전류 또는 스핀-궤도 토크에 의하여 자성체층(110)의 자화 방향이 스위칭될 수 있다.

- [0067] 자성체충(110)과 전원(V<sub>DD</sub>) 사이에는 헤더 트랜지스터(TH)가 구비되며, 전류출력충(150)과 접지 사이에는 풋터 트랜지스터(TF)가 구비될 수 있다.

- [0068] 헤더 트랜지스터(TH)는 전극층(171)을 통해 자성체층(110)에 접속되며, 풋터 트랜지스터(TF)는 전극층(173)을 통해 전류출력층(173)에 접속될 수 있다.

- [0069] 헤더 트랜지스터(TH)는 전원(V<sub>DD</sub>)과 전극층(171) 사이에 접속되며, 제어신호(Vsup)에 응답하여 온(on)될 수 있다.

- [0070] 풋터 트랜지스터(TF)는 전원(V<sub>DD</sub>)과 전극층(173) 사이에 접속되며, 제어신호(Vsup)에 응답하여 온(on)될 수 있다.

- [0071] 헤더 트랜지스터(TH)와 풋터 트랜지스터(TF)는, 제어신호(Vsup)가 공급될 때 수직 전류(Isup)가 자성체층(110), 스핀 주입층(130), 스핀-전하 변환층(140) 및 전류 출력층(150)을 통해 흐를 수 있도록, 자성체층(110), 스핀 주입층(130), 스핀-전하 변환층(140) 및 전류 출력층(150)의 수직 방향으로 형성되는 것이 바람직하다.

- [0072] 도 2에서는 헤더 트랜지스터(TH)와 풋터 트랜지스터(TF)가 동시에 구비되는 경우를 도시하였으나, 본 발명의 실시 예는 이에 한정되지 않는다. 예를 들어, 헤더 트랜지스터(TH)와 풋터 트랜지스터(TF)는 둘 중에 적어도 하나만 구비되면 충분하다.

- [0073] 입력 노드(IN)로부터 공급되는 입력 전류(I<sub>in</sub>)의 방향에 따른 스핀 로직 소자(100)의 동작은 도 3 내지 도 6을 통해 보다 상세하게 설명될 것이다.

- [0074] 도 3은 입력 전류에 대응하여 자성체충의 자화 방향이 스위칭되는 과정의 일례를 나타내는 도면이다. 도 3은 입력 전류(I<sub>in</sub>)가 입력 노드(IN)로부터 전류 공급부(200)로 흐를 때 자성체충(110)의 자화 방향(Ms)이 스위칭되는 과정을 설명하기 위한 도면이다.

- [0075] 도 3을 참조하면, 입력 전류(I<sub>in</sub>)가 입력 노드(IN)로부터 전류 공급부(200)로 공급되면 커패시터(C)가 충전될 수 있다. 다시 말해, 커패시터(C)의 양단 전압(Vc)은 입력 전류(I<sub>in</sub>)에 의해 소정의 기준 전압 이상으로 충전될 수 있다.

- [0076] 종속 전원(DS)은 커패시터(C)의 양단 전압(Vc)에 따라 양의 전압을 출력한다.

- [0077] 이때, 전달 트랜지스터(TM)는 NMOS(N-channel MOSFET)로서 입력 전류( $I_{in}$ )를 증폭하여 스핀 로직 소자(100)로 출력할 수 있다. 구체적으로, 전달 트랜지스터(TM)는 증폭된 전류(Itr)를 전극(161), 전류전달층(120) 및 전극(163)을 통해 접지 방향으로 공급할 수 있다.

- [0078] 전류전달층(120)은 증폭된 전류(Itr)이 흐를 때 증폭된 전류(Itr)의 방향으로 스핀 전류 또는 스핀-궤도 토크가 생성된다. 그 결과, 자성체층(110)의 자화 방향(Ms)이 도 3에 도시된 바와 같이 유도된 자기장에 의해 스위칭될 수 있다.

- [0079] 도 4는 자성체의 자화 방향에 따라 출력 전류가 발생하는 과정의 일례를 나타내는 도면이다. 도 4는 도 3에 도 시된 바와 같이 자성체층(110)의 자화 방향(Ms)이 스위칭되었을 때 출력 전류(Iout)의 방향이 결정되는 과정을 설명하기 위한 도면이다.

- [0080] 도 4를 참조하면, 자성체층(110)의 자화 방향(Ms)이 스위칭 된 이후 수직 전류(Isup)가 자성체층(110), 스핀 주 입층(130), 스핀-전하 변환층(140) 및 전류 출력층(150)을 통해 흐르면 출력 전류(Iout)가 발생할 수 있다.

- [0081] 스핀 주입층(130)은 자성체층(110)의 자화 방향에 대응하는 방향의 스핀전류를 주입받을 수 있다. 구체적으로, 스핀 주입층(130)은 스핀 필터로서 자성체층(110)의 자화 방향에 대응하는 방향을 갖는 스핀 전류를 통과시킬 수 있다.

- [0082] 스핀-전하 변환층(140)은 스핀 주입층(130)을 통과한 스핀전류를 전하전류로 변환하여 출력한다. 이때, 스핀-전 하 변환층(140)으로부터 출력된 상기 전하전류가 전류출력층(150)을 통해 흐르면서 출력 전류(Iout)로서 역할할 수 있다.

- [0083] 도 3에 도시된 입력 전류( $I_{in}$ )의 방향과 출력 전류( $I_{out}$ )의 방향이 반대인 바 스핀 로직 소자( $I_{in}$ )는 인버터로 동작함을 이해할 수 있다.

- [0084] 도 5는 입력 전류에 대응하여 자성체충의 자화 방향이 스위칭되는 과정의 다른 예를 나타내는 도면이다. 도 5는 입력 전류(I<sub>in</sub>')가 전류 공급부(200)로부터 입력 노드(IN)로 흐를 때, 즉, 입력 노드(IN)로 입력 전류(I<sub>in</sub>')가 싱크(sink)될 때 자성체충(110)의 자화 방향(Ms)이 스위칭되는 과정을 설명하기 위한 도면이다.

- [0085] 도 5를 참조하면, 입력 전류(I<sub>in</sub>')가 입력 노드(IN)로부터 전류 공급부(200)로 공급되면 커패시터(C)는 방전될 수 있다.

- [0086] 도 3을 참조하면, 입력 전류(I<sub>in'</sub>)가 입력 노드(IN)로부터 전류 공급부(200)로 공급되면 커패시터(C)가 방전될 수 있다. 다시 말해, 커패시터(C)의 양단 전압(Vc)은 입력 전류(I<sub>in</sub>')에 의해 소정의 기준 전압 미만으로 방전될

수 있다.

- [0087] 종속 전원(DS)은 커패시터(C)의 양단 전압(Vc)에 따라 음의 전압을 출력한다.

- [0088] 이때, 전달 트랜지스터(TM)는 NMOS로서 입력 전류(I<sub>in</sub>')를 증폭하여 스핀 로직 소자(100)로 출력할 수 있다. 구체적으로, 전달 트랜지스터(TM)는 증폭된 전류(Itr')를 접지로부터 전극(163), 전류전달층(120) 및 전극(161)을 통해 전달 트랜지스터(TM) 방향으로 공급할 수 있다. 즉, 전달 트랜지스터(TM)는 접지로부터 전류전달층(120)을 통해 전류(Itr')를 싱크(sink)할 수 있다.

- [0089] 전류전달층(120)은 증폭된 전류(Itr')이 흐를 때 증폭된 전류(Itr')의 방향에 대응하는 스핀 전류 또는 스핀-궤도 토크를 생성할 수 있다. 그 결과, 자성체층(110)의 자화 방향(Ms)이 도 5에 도시된 바와 같이 스위칭될 수 있다.

- [0090] 도 6은 자성체의 자화 방향에 따라 출력 전류가 발생하는 과정의 다른 예를 나타내는 도면이다. 도 6는 도 5에 도시된 바와 같이 자성체층(110)의 자화 방향(Ms)이 스위칭되었을 때 출력 전류(Iout')의 방향이 결정되는 과정을 설명하기 위한 도면이다.

- [0091] 도 6을 참조하면, 자성체층(110)의 자화 방향(Ms)이 스위칭 된 이후 수직 전류(Isup)가 자성체층(110), 스핀 주 입층(130), 스핀-전하 변환층(140) 및 전류 출력층(150)을 통해 흐르면 출력 전류(Iout')가 발생할 수 있다.

- [0092] 스핀 주입층(130)은 자성체층(110)의 자화 방향에 대응하는 방향의 스핀전류를 주입받을 수 있다. 구체적으로, 스핀 주입층(130)은 스핀 필터로서 자성체층(110)의 자화 방향에 대응하는 방향을 갖는 스핀 전류를 통과시킬 수 있다.

- [0093] 스핀-전하 변환층(140)은 스핀 주입층(130)을 통과한 스핀전류를 전하전류로 변환하여 출력한다. 이때, 스핀-전 하 변환층(140)으로부터 출력된 상기 전하전류가 전류출력층(150)을 통해 흐르면서 출력 전류(Iout')로서 역할할 수 있다.

- [0094] 도 5에 도시된 입력 전류( $I_{in}$ ')의 방향과 출력 전류( $I_{out}$ ')의 방향이 반대인 바 스핀 로직 소자( $I_{in}$ ')의 인버터로 동작함을 이해할 수 있다.

- [0095] 도 7은 도 1에 도시된 스핀 로직 소자를 이용해 구성된 버퍼를 나타내는 도면이다. 도 7은 도 2에 도시된 스핀 로직 소자 2개를 직렬로 연결한 것으로서 첫번째 스테이지(좌측 스핀 로직 소자, 100-1)의 전류 출력층(150)과 두번째 스테이지(우측 스핀 로직 소자, 100-2)의 입력 노드가 전기적으로 접속된 것으로 이해될 수 있다.

- [0096] 도 7을 참조하면, 앞서 설명한 바와 같이 스핀 로직 소자들(100-1, 100-2)은 각각 인버터로 동작하므로 입력 전류(I<sub>in</sub>)의 방향과 중간 출력 전류(Imed)의 방향은 반대가 되며 중간 출력 전류(Imed)의 방향과 출력 전류(Iout)의 방향이 반대가 된다. 즉, 입력 전류(I<sub>in</sub>)의 방향과 출력 전류(Iout)의 방향이 동일하게 된다.

- [0097] 도 7을 통해, 짝수 개의 스핀 로직 소자들을 직렬로 연결할 경우 버퍼로 동작할 수 있음을 알 수 있다.

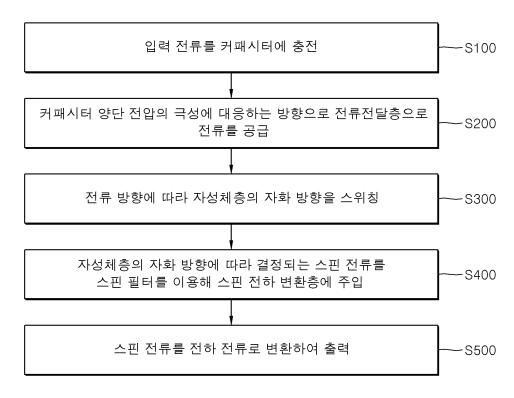

- [0098] 도 8은 본 발명의 실시 예에 따른 스핀 로직 소자의 동작을 나타내는 순서도이다.

- [0099] 도 8을 참조하면, 입력 노드(IN)을 통해 공급되는 입력 전류(I<sub>in</sub>)에 의해 커패시터(C)가 충전된다(S100). 다시 말해, 전류 공급부(200)로 입력 전류(I<sub>in</sub>)가 공급되면 이를 커패시터(C)에 충전한다.

- [0100] 커패시터(C)의 양단 전압(Vc)에 따라 결정된 방향으로 전류전달층(120)을 통해 전류를 공급한다(S200). 커패시터(C)에 입력 전류(I<sub>in</sub>)에 대응하는 전압(Vc)이 충전되면, 종속 전원(DS)은 커패시터(C)의 양단 전압(Vc)에 대응하는 전압을 출력한다. 이에 따라, 전달 트랜지스터(TM)은 커패시터(C)의 양단 전압(Vc)에 대응하는 방향, 즉, 입력 전류(I<sub>in</sub>)의 방향에 대응하는 방향의 전류를 전류전달층(120)으로 공급한다.

- [0101] 전류전달층(120)을 통해 흐르는 전류의 방향에 의해 자성체층의 자화 방향을 스위칭한다(S300). 전류전달층 (120)을 통해 전류가 흐르면 전류의 방향에 대응하여 자기장이 유도되고, 유도된 자기장에 의해 자성체층(110)의 자화 방향이 스위칭된다.

- [0102] 자성체층(100)의 자화 방향에 따라 결정되는 스핀 전류를 스핀 필터를 이용해 스핀-전하 변환층에 주입한다 (S400). 수직 전류(Isup)가 자성체층(110), 스핀 주입층(130), 스핀-전하 변환층(140) 및 전류 출력층(150)을 통해 흐르면, 스핀 주입층(130)이 스핀 필터로서 동작하여 스핀 전류를 스핀-전하 변환층(140)으로 공급한다.

- [0103] 스핀 전류를 전하 전류로 변환하여 출력 전류로서 출력된다(S500). 스핀-전하 변환층(140)은 주입된 스핀-전하를 전하 전류로 변환하고 변환된 전하 전류를 출력 전류로서 전류출력층(150)을 통해 출력 노드(OUT)로 출력한다.

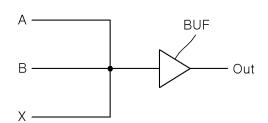

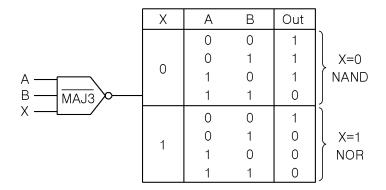

- [0104] 도 9는 본 발명의 실시 예에 따른 스핀 로직 소자를 이용해 구현될 수 있는 다수결 게이트를 설명하기 위한 도면이다.

- [0105] 도 9를 참조하면, 하나의 버퍼(BUF)를 이용해 다수결 게이트(majority gate, MAJ3)를 구현할 수 있다.

- [0106] 버퍼(BUF)는 입력 신호들(A, B, X) 중에서 다수를 차지하는 값을 출력 신호(Out)로서 출력한다.

- [0107] 다시 말해, 입력 신호들(A, B, X)은 전류 형태로서 해당하는 값에 따라 전류를 소싱(sourcing)또는 싱크(sink) 하는데, 버퍼(BUF)의 입력 단에는 다수를 차지하는 값에 대응하는 전류가 공급된다.

- [0108] 다수결 게이트(MAJ3)의 진리표는 도 9에 도시된 바와 같다.

- [0109] 입력 신호들(A, B, X) 중에서 어느 하나, 예를 들어, 입력 신호(X)의 값에 따라, 나머지들, 예를 들어, 입력신호들(A, B)에 대한 논리식(AND 또는 OR)이 결정됨을 이해할 수 있다.

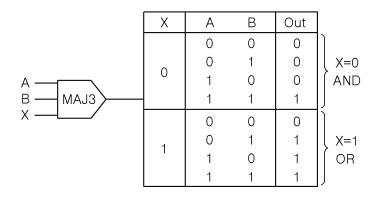

- [0110] 도 10은 본 발명의 실시 예에 따른 스핀 로직 소자를 이용해 구현될 수 있는 반전 다수결 게이트를 설명하기 위한 도면이다. 도 10에 도시된 논리 회로는 도 9에 도시된 논리 회로와 제4 인터버(INV4) 대신 버퍼(BUF)가 포함되는 점을 제외하고 동일하다.

- [0111] 도 10을 참조하면, 하나의 인버터(INV)를 이용해 반전 다수결 게이트(inverse majority gate, *MAJ3*)를 구현할 수 있다.

- [0112] 인버터(INV)는 입력 신호들(A, B, X) 중에서 다수를 차지하는 값을 반전하고 반전된 신호를 출력 신호(Out)로서 출력한다.

- [0113] 다시 말해, 입력 신호들(A, B, X)은 전류 형태로서 해당하는 값에 따라 전류를 소성(sourcing)또는 싱크(sink) 하는데, 인버터(INV)의 입력 단에는 다수를 차지하는 값에 대응하는 전류가 공급되며, 인버터(INV)는 공급된 전류를 반전하여 출력한다.

- [0114] 반전 다수결 게이트(MAJ3)의 진리표는 도 9에 도시된 바와 같다.

- [0115] 입력 신호들(A, B, X) 중에서 어느 하나, 예를 들어, 입력 신호(X)의 값에 따라, 나머지들, 예를 들어, 입력신호들(A, B)에 대한 논리식(NAND 또는 NOR)이 결정됨을 이해할 수 있다.

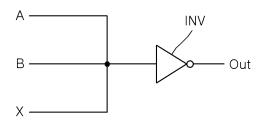

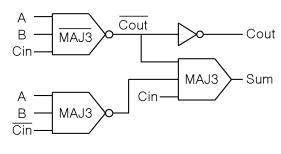

- [0116] 도 11은 본 발명의 실시 예에 따른 스핀 로직 소자를 이용해 구현될 수 있는 1-비트 전가산기(1-bit full adder)를 설명하기 위한 도면이다.

- [0117] 도 11을 참조하면, 1개의 반전 다수결 게이트(MAJ3)와 2개의 다수결 게이트(MAJ3), 1개의 인버터를 이용해 1-비트 전가산기를 구현할 수 있다.

- [0118] 이와 같이 구현된 1-비트 전가산기의 진리표는 도 11에 도시된 바와 같다.

- [0119] CMOS를 이용해 1-비트 전가산기를 구현할 경우 2개의 XOR 게이트, 3개의 NAND 게이트 및 28개의 트랜지스터를 이용해 점유하는 면적이 5800 [F<sup>2</sup>]로 계산된다. 이에 반해, 본 발명의 실시 예에 따른 스핀 로직 소자를 기반으로 1-비트 전가산기를 구현할 경우 스핀 로직 소자 4개로 구성되는 1개의 다수결 회로와 3개의 반전(또는 비반 전) 다수결 회로들을 이용함으로써 점유하는 면적이 최소 920 [F<sup>2</sup>]에 불과하다. 즉, 본 발명의 스핀 로직 소자를 기반으로 하여 약 85%의 공간 절약이 가능함을 알 수 있다.

- [0120] 더하여, 시뮬레이션 결과, CMOS 기반 1-비트 전가산기의 소모 에너지는 142 [aJ]로 계산되었는데 본 발명의 실시 예에 따른 스핀 로직 소자 기반 1-비트 전가산기의 소모 에너지는 27 [aJ]로서 CMOS 대비 78% 저감될 수 있다.

- [0121] 본 발명은 도면에 도시된 일 실시 예를 참고로 설명되었으나 이는 예시적인 것에 불과하며, 본 기술 분야의 통상의 지식을 가진 자라면 이로부터 다양한 변형 및 균등한 타 실시 예가 가능하다는 점을 이해할 것이다. 따라

서, 본 발명의 진정한 기술적 보호 범위는 첨부된 등록청구범위의 기술적 사상에 의해 정해져야 할 것이다.

### 부호의 설명

[0122] 100; 스핀 로직 소자

110, 110-1, 110-2; 자성체층

120, 120-1, 120-2; 전류전달층

130, 130-1, 130-2; 스핀 주입층

140, 140-1, 140-2; 스핀-전하 변환층

150, 150-1, 150-2; 전류 출력층

## 도면

#### 도면9

#### 다수결 게이트 (MAJ3)

## 반전 다수결 게이트 (MAJ3)

| Cin | Α | В | Cout | Sum |

|-----|---|---|------|-----|

| 0   | 0 | 0 | 0    | 0   |

| 0   | 0 | 1 | 0    | 1   |

| 0   | 1 | 0 | 0    | 1   |

| 0   | 1 | 1 | 1    | 0   |

| 1   | 0 | 0 | 0    | 1   |

| 1   | 0 | 1 | 1    | 0   |

| 1   | 1 | 0 | 1    | 0   |

| 1   | 1 | 1 | 1    | 1   |