# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**G09G 3/3233** (2016.01) **H01L 29/786** (2006.01)

(52) CPC특허분류

**G09G 3/3233** (2013.01) **H01L 29/78672** (2013.01)

(21) 출원번호 10-2019-0109685

(22) 출원일자 **2019년09월04일** 심사청구일자 **2019년09월04일**

(56) 선행기술조사문헌 KR1020150100459 A\*

\*는 심사관에 의하여 인용된 문헌

(24) 등록일자

(45) 공고일자

2021년01월06일

2020년12월30일

(11) 등록번호 10-2199338

(73) 특허권자

# 연세대학교 산학협력단

서울특별시 서대문구 연세로 50 (신촌동, 연세대 학교)

(72) 발명자

### 김현재

서울특별시 마포구 마포대로 195, 402동 1101호 (아현동, 마포 래미안 푸르지오)

#### 홍성환

인천광역시 남동구 논고개로68번길 49, 101동 3102호(논현동, 힐스테이트아파트) (뒷면에 계속)

(74) 대리인

특허법인우인

전체 청구항 수 : 총 3 항

심사관 : 이승민

# (54) 발명의 명칭 LTPO 기술을 이용한 AMOLED 디스플레이의 구동 트랜지스터

#### (57) 요 약

본 실시예들은 다결정 실리콘 트랜지스터와 산화물 트랜지스터를 병렬 연결하고, 다결정 실리콘 트랜지스터와 산화물 트랜지스터에 동형 외인성 반도체를 적용하여, 히스테리시스 특성을 보상하는 디스플레이의 구동 트랜지스터를 제공한다.

# 대 표 도 - 도1

구동 트랜지스터 (100)

다결정 실리콘 트랜지스터 (200)

> 산화물 트랜지스터 (300)

(52) CPC특허분류

**H01L 29/7869** (2013.01) G09G 2300/0809 (2013.01)

(72) 발명자

# 김형태

서울특별시 양천구 목동동로 100, 1315동 302호(신 정동, 목동신시가지아파트13단지)

### 정주성

경기도 성남시 분당구 발이봉로7번길 4(수내동)

이 발명을 지원한 국가연구개발사업

과제고유번호 2019020180

부처명 과학기술정보통신부

과제관리(전문)기관명 한국연구재단

연구사업명 나노소재기술개발사업

연구과제명 [Ezbaro] (총괄/1세부)굴곡표면상 3차원 구조 EHD 인쇄기술 개발 (1단계)(2/3)

기 여 율 1/1

과제수행기관명연세대학교 산학협력단연구기간2019.02.01 ~ 2020.01.31

# 이이삭

경기도 수원시 팔달구 중부대로223번길 102, 108동 109호(우만동, 주공1단지아파트)

#### 정수진

서울특별시 마포구 월드컵북로 235, 13동 803호(성 산동, 성산시영아파트)

# 명 세 서

# 청구범위

#### 청구항 1

발광 소자를 구동시키는 구동 트랜지스터에 있어서,

상기 구동 트랜지스터는 병렬 연결된 다결정 실리콘 트랜지스터와 산화물 트랜지스터를 포함하며,

상기 다결정 실리콘 트랜지스터와 상기 산화물 트랜지스터는 동형 외인성 반도체를 사용하여 히스테리시스에 의한 명암 변화를 감소시키며,

상기 다결정 실리콘 트랜지스터 및 상기 산화물 트랜지스터는 동시에 턴온 또는 턴오프 동작하고,

상기 다결정 실리콘 트랜지스터는 히스테리시스로 인한 전류 감소에 따라 저항이 M배 증가하고, 상기 산화물 트랜지스터는 상기 히스테리시스로 인한 전류 감소에 따라 저항이 N배 증가하고, 상기 N이 1보다 큰 양수이고 상기 M이 상기 N보다 큰 양수이고 L이 M/N이라고 정의할 때, 상기 구동 트랜지스터는 2M/(L+1)로 상기 히스테리시스로 인한 저항 증가를 보상하고,

상기 L이 1보다 커서 상기 히스테리시스에 따른 플리커링 현상을 억제하고, 상기 구동 트랜지스터의 균일도를 보상하는 것을 특징으로 하는 구동 트랜지스터.

### 청구항 2

제1항에 있어서,

상기 다결정 실리콘 트랜지스터에 P형 반도체가 적용되고 상기 산화물 트랜지스터에 P형 반도체가 적용되거나,

상기 다결정 실리콘 트랜지스터 또는 상기 산화물 트랜지스터 대신에 P형 유기 반도체가 적용되거나,

상기 다결정 실리콘 트랜지스터에 N형 반도체가 적용되고 상기 산화물 트랜지스터에 N형 반도체가 적용되거나,

상기 다결정 실리콘 트랜지스터 또는 상기 산화물 트랜지스터 대신에 N형 유기 반도체가 적용되는 것을 특징으로 하는 구동 트랜지스터.

# 청구항 3

제1항에 있어서,

상기 다결정 실리콘 트랜지스터와 상기 산화물 트랜지스터는 게이트를 공유하며, 상기 게이트를 기준으로 상기 다결정 실리콘 트랜지스터의 활성층과 상기 산화물 트랜지스터의 활성층이 대칭하여 위치하고,

상기 다결정 실리콘 트랜지스터의 활성층의 폭이 상기 산화물 트랜지스터의 활성층의 폭보다 크며,

상기 다결정 실리콘 트랜지스터와 상기 산화물 트랜지스터는 탑 게이트 구조 또는 바텀 게이트 구조로 형성되는 것을 특징으로 하는 구동 트랜지스터.

### 청구항 4

삭제

# 청구항 5

삭제

#### 발명의 설명

# 기 술 분 야

[0001] 본 발명이 속하는 기술 분야는 구동 트랜지스터 및 디스플레이에 관한 것이다.

## 배경기술

- [0002] 이 부분에 기술된 내용은 단순히 본 실시예에 대한 배경 정보를 제공할 뿐 종래기술을 구성하는 것은 아니다.

- [0003] LTPO(Low Temperature Poly-Si & Oxide)는 디스플레이 백플레인에 다결정 실리콘(Low Temperature Polycrystalline Silicon, LTPS) 트랜지스터와 산화물 (Oxide) 트랜지스터를 함께 사용하는 기술이며, 특히 픽셀 회로에서 스위칭 트랜지스터를 산화물 트랜지스터로 사용하는 추세이다.

- [0004] LTPO 기술을 사용하면 모바일 기기의 전력 소모를 크게 줄일 수 있는 장점이 있다. LTPO 기술이 적용된 디스플 레이 백플레인은 다결정 실리콘 반도체에서 캐리어 이동도가 높은 장점을 활용하고, 산화물 반도체에서 누설 전류가 적은 장점을 활용한다.

- [0005] 다만 LTPO 기술이 적용된 디스플레이 백플레인은 채널 내의 트래핑/디트래핑으로 인한 히스테리시스 문제가 있고, 전류 감소와 명암 변화를 발생시킨다. 다결정 실리콘 반도체의 히스테리시스 특성은 플리커링 현상을 발생시킨다.

# 선행기술문헌

# 특허문헌

- [0006] (특허문헌 0001) 한국등록특허공보 제10-1892510호 (2018.08.22)

- (특허문헌 0002) 한국등록특허공보 제10-1672091호 (2016.10.27.)

# 발명의 내용

### 해결하려는 과제

- [0007] 본 발명의 실시예들은 다결정 실리콘 트랜지스터와 산화물 트랜지스터를 병렬 연결하고, 다결정 실리콘 트랜지스터와 산화물 트랜지스터에 동형 외인성 반도체를 적용함으로써, 디스플레이의 구동 트랜지스터가 가진 히스테 리시스 특성을 보상하는 데 발명의 주된 목적이 있다.

- [0008] 본 발명의 명시되지 않은 또 다른 목적들은 하기의 상세한 설명 및 그 효과로부터 용이하게 추론할 수 있는 범위 내에서 추가적으로 고려될 수 있다.

# 과제의 해결 수단

- [0009] 본 실시예의 일 측면에 의하면, 발광 소자를 구동시키는 구동 트랜지스터에 있어서, 상기 구동 트랜지스터는 병 렬 연결된 다결정 실리콘 트랜지스터와 산화물 트랜지스터를 포함하며, 상기 다결정 실리콘 트랜지스터와 상기 산화물 트랜지스터는 동형 외인성 반도체를 사용하여 히스테리시스에 의한 명암 변화를 감소시키는 것을 특징으로 하는 구동 트랜지스터를 제공한다.

- [0010] 상기 다결정 실리콘 트랜지스터에 P형 반도체가 적용되고 상기 산화물 트랜지스터에 P형 반도체가 적용될 수 있다.

- [0011] 상기 다결정 실리콘 트랜지스터 또는 상기 산화물 트랜지스터 대신에 P형 유기 반도체가 적용될 수 있다.

- [0012] 상기 다결정 실리콘 트랜지스터에 N형 반도체가 적용되고 상기 산화물 트랜지스터에 N형 반도체가 적용될 수 있다.

- [0013] 상기 다결정 실리콘 트랜지스터 또는 상기 산화물 트랜지스터 대신에 N형 유기 반도체가 적용될 수 있다.

- [0014] 상기 다결정 실리콘 트랜지스터와 상기 산화물 트랜지스터는 게이트를 공유할 수 있다. 상기 게이트를 기준으로 상기 다결정 실리콘 트랜지스터의 활성층과 상기 산화물 트랜지스터의 활성층이 대칭하여 위치할 수 있다.

- [0015] 상기 다결정 실리콘 트랜지스터의 활성층의 폭이 상기 산화물 트랜지스터의 활성층의 폭보다 크게 형성될 수 있다.

- [0016] 상기 다결정 실리콘 트랜지스터와 상기 산화물 트랜지스터는 탑 게이트 구조 또는 바텀 게이트 구조로 형성될

수 있다.

- [0017] 상기 다결정 실리콘 트랜지스터 및 상기 산화물 트랜지스터는 동시에 턴온 또는 턴오프 동작할 수 있다.

- [0018] 상기 다결정 실리콘 트랜지스터는 히스테리시스로 인한 전류 감소에 따라 저항이 M배 증가하고, 상기 산화물 트랜지스터는 히스테리시스로 인한 전류 감소에 따라 저항이 N배 증가하고, 상기 N이 1보다 큰 양수이고 상기 M이 상기 N보다 큰 양수이고 L이 M/N이라고 정의할 때, 상기 구동 트랜지스터는 2M/(L+1)로 히스테리시스로 인한 저항 증가를 보상할 수 있다.

# 발명의 효과

- [0019] 이상에서 설명한 바와 같이 본 발명의 실시예들에 의하면, 다결정 실리콘 트랜지스터와 산화물 트랜지스터를 병렬 연결하고, 다결정 실리콘 트랜지스터와 산화물 트랜지스터에 동형 외인성 반도체를 적용함으로써, 디스플레이의 구동 트랜지스터가 가진 히스테리시스 특성을 보상할 수 있는 효과가 있다.

- [0020] 여기에서 명시적으로 언급되지 않은 효과라 하더라도, 본 발명의 기술적 특징에 의해 기대되는 이하의 명세서에 서 기재된 효과 및 그 잠정적인 효과는 본 발명의 명세서에 기재된 것과 같이 취급된다.

### 도면의 간단한 설명

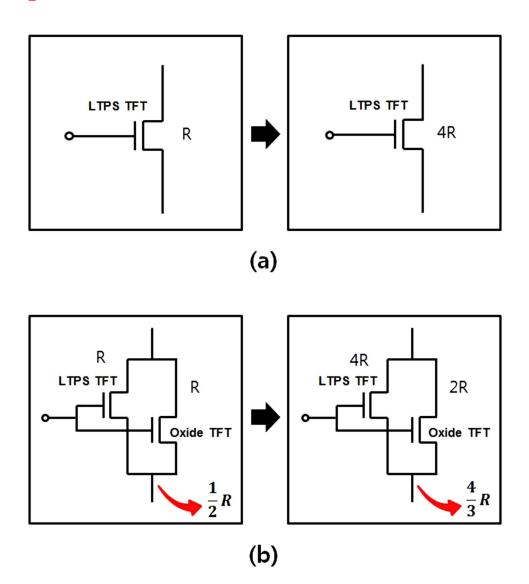

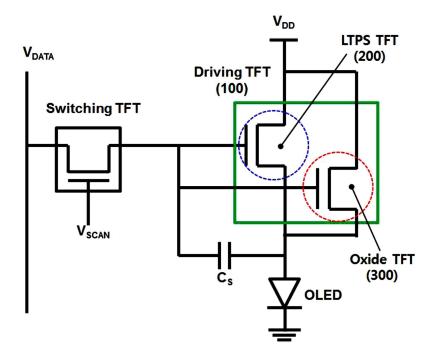

- [0021] 도 1은 본 발명의 일 실시예에 따른 구동 트랜지스터를 예시한 블록도이다.

- 도 2는 본 발명의 일 실시예에 따른 구동 트랜지스터의 회로도를 예시한 것이다.

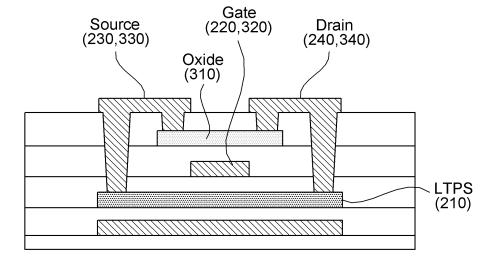

- 도 3은 본 발명의 일 실시예에 따른 구동 트랜지스터의 단면도를 예시한 것이다.

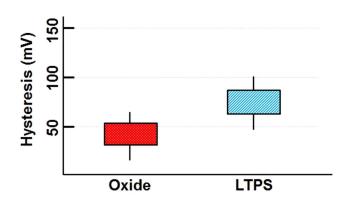

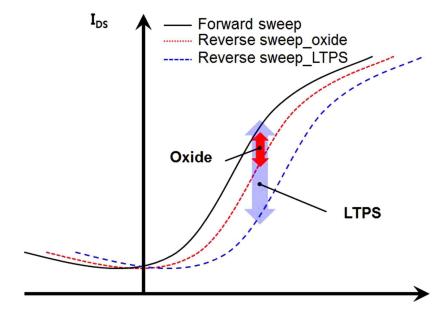

- 도 4는 다결정 실리콘 트랜지스터 및 산화물 트랜지스터의 히스테리시스 특성을 예시한 것이다.

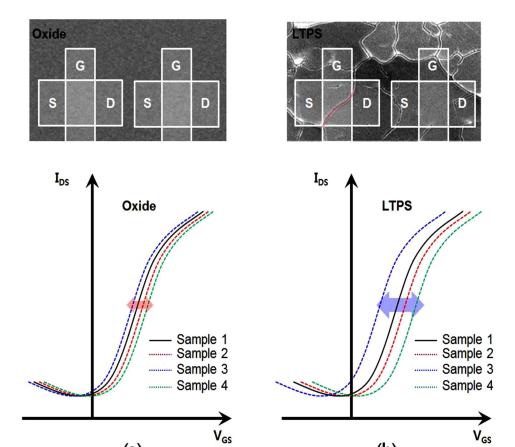

- 도 5는 다결정 실리콘 트랜지스터 및 산화물 트랜지스터의 균일도를 예시한 것이다.

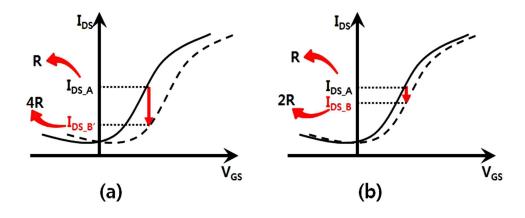

- 도 6 및 도 7은 본 발명의 일 실시예에 따른 구동 트랜지스터의 히스테리시스 특성을 예시한 것이다.

## 발명을 실시하기 위한 구체적인 내용

- [0022] 이하, 본 발명을 설명함에 있어서 관련된 공지기능에 대하여 이 분야의 기술자에게 자명한 사항으로서 본 발명의 요지를 불필요하게 흐릴 수 있다고 판단되는 경우에는 그 상세한 설명을 생략하고, 본 발명의 일부 실시예들을 예시적인 도면을 통해 상세하게 설명한다.

- [0023] 본 실시예에 따른 구동 트랜지스터는 디스플레이에 적용될 수 있다.

- [0024] 디스플레이의 구동 트랜지스터가 가진 히스테리시스 특성을 보상하기 위해, 다결정 실리콘 트랜지스터와 산화물 트랜지스터를 병렬 연결하고, 다결정 실리콘 트랜지스터와 산화물 트랜지스터에 동형 외인성 반도체를 적용하여, 다결정 실리콘 트랜지스터와 산화물 트랜지스터를 동시에 턴온 또는 턴오프 동작시킨다.

- [0025] 도 1은 본 발명의 일 실시예에 따른 구동 트랜지스터를 예시한 블록도이고, 도 2는 본 발명의 일 실시예에 따른 구동 트랜지스터의 회로도를 예시한 도면이고, 도 3은 본 발명의 일 실시예에 따른 구동 트랜지스터의 단면도를 예시한 도면이다.

- [0026] 디스플레이는 발광 소자를 포함하고, 스캔 라인과 데이터 라인에 연결된 스위칭 트랜지스터를 포함하고, 발광 소자를 구동시키는 구동 트랜지스터(100)를 포함한다. 스위칭 트랜지스터와 구동 트랜지스터(100)는 전기적으로 연결된다.

- [0027] 구동 트랜지스터(100)는 다결정 실리콘 트랜지스터(200) 및 산화물 트랜지스터(300)를 포함한다.

- [0028] 다결정 실리콘 트랜지스터(200)는 다결정 실리콘 활성층(210), 게이트 전극(220), 소스 전극(230), 및 드레인 전극(240)를 포함하고, 산화물 트랜지스터(300)는 산화물 활성층(310), 게이트 전극(220), 소스 전극(230), 및 드레인 전극(240)를 포함한다.

- [0029] 도 2를 참조하면, 본 실시예에 따른 구동 트랜지스터(100)에서 다결정 실리콘 트랜지스터(200)와 산화물 트랜지스터(300)는 병렬 연결된다. 다결정 실리콘 트랜지스터(200)의 게이트 전극(220)와 산화물 트랜지스터(300)의 게이트 전극(320)는 공유될 수 있다. 다결정 실리콘 트랜지스터(200)의 소스 전극(230)와 산화물 트랜지스터 (300)의 소스 전극(330)은 공유될 수 있다. 다결정 실리콘 트랜지스터(200)의 드레인 전극(240)와 산화물 트랜

지스터(300)의 드레인 전극(340)은 공유될 수 있다.

- [0030] 도 3을 참조하면, 본 실시예에 따른 구동 트랜지스터(100)에서 다결정 실리콘 트랜지스터(200)와 산화물 트랜지스터(300)는 일부 영역 또는 전체 영역이 적충된다. 다결정 실리콘 트랜지스터(200)의 다결정 실리콘 활성층 (210)과 산화물 활성층(310)은 일부 영역이 중첩된다.

- [0031] 다결정 실리콘 트랜지스터(200)와 산화물 트랜지스터(300)는 게이트(220, 320)를 공유할 수 있다. 게이트를 기준으로 다결정 실리콘 트랜지스터의 활성층과 산화물 트랜지스터의 활성층이 대칭하여 위치할 수 있다.

- [0032] 도 3에서는 다결정 실리콘 활성층(210)을 게이트(220, 320)의 하단에 위치시키고, 산화물 활성층(310)을 게이트 (220, 320)의 상단에 위치시켰으나, 반대 위치도 가능하다.

- [0033] 소스 전극(230, 330)과 드레인 전극(240, 340)의 배치로 인하여 다결정 실리콘 트랜지스터의 활성층(210)의 폭이 산화물 트랜지스터의 활성층(310)의 폭보다 크게 형성되도록 하였으나, 다결정 실리콘 트랜지스터의 활성층 (210)과 산화물 트랜지스터의 활성층(310)의 위치를 바꾸어, 폭의 길이를 변경하는 것도 가능하다.

- [0034] 다결정 실리콘 트랜지스터와 산화물 트랜지스터는 게이트를 공유하지 않고 각각의 게이트를 배치할 수도 있다. 다결정 실리콘 트랜지스터와 산화물 트랜지스터는 탑 게이트 구조 또는 바텀 게이트 구조로 다양하게 형성될 수 있다.

- [0035] 필요에 따라 층 또는 전극 사이에 절연층 또는 버퍼층이 존재할 수 있다.

- [0036] 다결정 실리콘 트랜지스터와 산화물 트랜지스터를 병렬 연결된 상태에서 다결정 실리콘 트랜지스터와 산화물 트랜지스터에 동형 외인성 반도체를 적용하여, 다결정 실리콘 트랜지스터와 산화물 트랜지스터를 동시에 턴온 또는 턴오프 동작시킴으로써, 디스플레이의 구동 트랜지스터가 가진 히스테리시스 특성을 보상할 수 있다.

- [0037] 도 4는 다결정 실리콘 트랜지스터 및 산화물 트랜지스터의 히스테리시스 특성을 예시한 것이고, 도 5는 다결정 실리콘 트랜지스터 및 산화물 트랜지스터의 균일도를 예시한 것이고, 도 6 및 도 7은 본 발명의 일 실시예에 따른 구동 트랜지스터의 히스테리시스 특성을 예시한 것이다.

- [0038] 도 4에 도시된 바와 같이 산화물 트랜지스터는 다결정 실리콘 트랜지스터보다 히스테리시스 특성이 우수하고, 도 5에 도시된 바와 같이 산화물 트랜지스터는 다결정 실리콘 트랜지스터보다 균일도가 높다. 산화물 트랜지스터의 높은 균일도로 인하여 구동 트랜지스터의 균일도의 보상 효과도 기대할 수 있다.

- [0039] 본 실시예에 따른 구동 트랜지스터는 병렬 연결된 다결정 실리콘 트랜지스터와 산화물 트랜지스터에 동형 외인 성 반도체를 적용하여, 다결정 실리콘 트랜지스터와 산화물 트랜지스터를 동시에 턴온 또는 턴오프 동작시킨다.

- [0040] 참고로, 이형 외인성 반도체는 다결정 실리콘 트랜지스터와 산화물 트랜지스터를 선택적으로 동작시킨다. 예컨 대, 다결정 실리콘 트랜지스터를 턴온하고 산화물 트랜지스터를 턴오프 동작시키거나, 다결정 실리콘 트랜지스터를 턴온 동작시킨다.

- [0041] 다결정 실리콘 트랜지스터와 산화물 트랜지스터를 함께 동작시키기 위해서, 다결정 실리콘 트랜지스터에 P형 반도체가 적용되고 산화물 트랜지스터에 P형 반도체가 적용될 수 있다. 다결정 실리콘 트랜지스터 또는 산화물 트랜지스터 대신에 P형 유기 반도체가 적용될 수 있다.

- [0042] 다결정 실리콘 트랜지스터에 N형 반도체가 적용되고 산화물 트랜지스터에 N형 반도체가 적용될 수 있다. 다결정 실리콘 트랜지스터 또는 산화물 트랜지스터 대신에 N형 유기 반도체가 적용될 수 있다.

- [0043] 상호 연결되지 않은 다결정 실리콘 트랜지스터와 산화물 트랜지스터를 각각 동작시키면, 다결정 실리콘 트랜지스터는 히스테리시스로 인한 전류 감소에 따라 저항이 M배 증가하고, 산화물 트랜지스터는 히스테리시스로 인한 전류 감소에 따라 저항이 N배 증가한다.

- [0044] N이 1보다 큰 양수이고 M이 N보다 큰 양수이고 L이 M/N이라고 정의할 때, 상호 연결된 다결정 실리콘 트랜지스 터와 산화물 트랜지스터는 동시에 동작하며, 구동 트랜지스터는 2M/(L+1) = 2MN/(M+N)로 히스테리시스로 인한 저항 증가를 보상할 수 있다.

- [0045] 예컨대, 다결정 실리콘 트랜지스터(LTPS TFT)를 단독으로 사용하면 R -> 4R로 4배 증가하는 반면에, 동형 외인 성 반도체를 적용한 다결정 실리콘 트랜지스터(LTPS TFT) 및 산화물 트랜지스터(Oxide TFT)는 R/2 -> 4R/3으로 8/3배 증가한다.

- [0046] 즉, L이 1보다 크므로, 2M/(L+1)는 M보다 작은 값을 갖고 히스테리시스 특성에 따른 플리커링 현상을 억제할 수

있다. 아울러 균일도 보상 효과도 기대할 수 있다.

[0047] 구동 트랜지스터에 구성요소들이 도 1에서는 분리되어 도시되어 있으나, 복수의 구성요소들은 상호 결합되어 적어도 하나의 모듈로 구현될 수 있다.

[0048] 디스플레이는 하드웨어, 펌웨어, 소프트웨어 또는 이들의 조합에 의해 로직회로 내에서 구현될 수 있고, 범용 또는 특정 목적 컴퓨터를 이용하여 구현될 수도 있다. 장치는 고정배선형(Hardwired) 기기, 필드 프로그램 가능한 게이트 어레이(Field Programmable Gate Array, FPGA), 주문형 반도체(Application Specific Integrated Circuit, ASIC) 등을 이용하여 구현될 수 있다. 또한, 장치는 하나 이상의 프로세서 및 컨트롤러를 포함한 시스템은칩(System on Chip, SoC)으로 구현될 수 있다.

[0049] 디스플레이는 패널을 포함하며, 하드웨어적 요소가 마련된 컴퓨팅 디바이스에 소프트웨어, 하드웨어, 또는 이들의 조합하는 형태로 탑재될 수 있다. 컴퓨팅 디바이스는 각종 기기 또는 유무선 통신망과 통신을 수행하기 위한 통신 모뎀 등의 통신장치, 프로그램을 실행하기 위한 데이터를 저장하는 메모리, 프로그램을 실행하여 연산 및 명령하기 위한 마이크로프로세서 등을 전부 또는 일부 포함한 다양한 장치를 의미할 수 있다.

본 실시예들은 본 실시예의 기술 사상을 설명하기 위한 것이고, 이러한 실시예에 의하여 본 실시예의 기술 사상의 범위가 한정되는 것은 아니다. 본 실시예의 보호 범위는 아래의 청구범위에 의하여 해석되어야 하며, 그와 동등한 범위 내에 있는 모든 기술 사상은 본 실시예의 권리범위에 포함되는 것으로 해석되어야 할 것이다.

## 부호의 설명

[0051] 100: 구동 트랜지스터

[0050]

200: 다결정 실리콘 트랜지스터

300: 산화물 트랜지스터

# 도면

### 도면1

구동 트랜지스터 (100)

다결정 실리콘 트랜지스터 (200)

산화물 트랜지스터 (300)

# 도면2

# 도면3

도면4

도면5

도면6

(a)

(b)

# 도면7