# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(45) 공고일자 2021년04월27일

(11) 등록번호 10-2245385

(24) 등록일자 2021년04월22일

(51) 국제특허분류(Int. Cl.)

**HO3K 19/177** (2020.01) **G11C 11/16** (2006.01)

(52) CPC특허분류

*H03K* 19/17728 (2013.01) *G11C* 11/1653 (2013.01)

(21) 출원번호 **10-2017-0038994**

(22) 출원일자 **2017년03월28일**

심사청구일자 2020년03월02일

(65) 공개번호 10-2018-0109365

(43) 공개일자 2018년10월08일

(56) 선행기술조사문헌

KR1020160073324 A\*

KR1020160073335 A

US07406668 B1

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

에스케이하이닉스 주식회사

경기도 이천시 부발읍 경충대로 2091

연세대학교 산학협력단

서울특별시 서대문구 연세로 50 (신촌동, 연세대

학교)

(72) 발명자

조강욱

경기도 고양시 일산서구 성저로 121 1101-803

김정빈

서울시 서대문구 연희로18길 42-6 207

(뒷면에 계속)

(74) 대리인

김선종

전체 청구항 수 : 총 20 항

심사관 : 최규돈

## (54) 발명의 명칭 자기 소자를 포함하는 LUT, 이를 포함하는 FPGA 및 기술 매핑 방법

#### (57) 요 약

본 기술에 의한 LUT는 입력 신호에 따라 디코딩 신호를 출력하는 디코더, 디코딩 신호에 대응하는 하나 또는 둘이상의 자기 소자를 선택하는 저장부 및 저장부에서 선택된 자기 소자의 프로그램 상태에 대응하는 신호를 출력하거나 선택된 자기 소자를 프로그램할 신호를 입력받는 신호 입출력부를 포함한다.

#### 대 표 도 - 도3

(52) CPC특허분류

**G11C 11/1675** (2013.01)

(72) 발명자

## 임민영

서울특별시 영등포구 양평로17길 36 102-303

#### 유태희

인천광역시 계양구 둥그재산길 27 (동양동, 주공아 파트4단지) 403-505

공지예외<u>적용 : 있음</u>

## 정의영

경기도 성남시 분당구 야탑로 124 612-1501

## 윤홍일

서울특별시 서초구 서운로 197 102-304

## 명세서

## 청구범위

#### 청구항 1

입력 신호에 따라 디코딩 신호를 출력하는 디코더;

제 1 단과 제 2 단 사이에 연결되며 다수의 자기 소자를 포함하며 상기 디코딩 신호를 반전한 신호에 따라 대응하는 자기 소자를 선택하는 제 1 저장부;

제 3 단과 제 4 단 사이에 연결되며 다수의 자기 소자를 포함하며 상기 디코딩 신호에 따라 대응하는 자기 소자를 선택하는 제 2 저장부; 및

상기 제 2 단과 상기 제 3 단 사이에 연결되며, 상기 제 1 저장부에서 선택된 자기 소자의 상태에 대응하는 신호를 출력하거나, 상기 제 1 저장부에서 선택된 자기 소자 또는 상기 제 2 저장부에서 선택된 자기 소자의 상태를 변경할 신호를 입력받는 신호 입출력부;

를 포함하는 LUT(Look Up Table) 회로.

#### 청구항 2

청구항 1에 있어서, 제 1 시간 동안 상기 디코딩 신호에 따라 상기 제 1 저장부 및 상기 제 2 저장부에서 선택된 자기 소자의 상태에 대응하는 신호를 출력하고, 상기 제 1 시간 경과 후 상기 제 1 저장부, 상기 제 2 저장부, 및 상기 신호 입출력부를 통해 전원단에서 접지단으로 흐르는 전류 경로를 차단하도록 상기 신호 입출력부를 제어하는 신호 입출력 제어부를 더 포함하는 LUT 회로.

#### 청구항 3

청구항 2에 있어서, 상기 신호 입출력 제어부는 상기 제 1 시간 동안 상기 신호 입출력부에서 출력된 신호가 상기 제 1 시간 경과 후에도 유지되도록 상기 신호 입출력부를 제어하는 LUT 회로.

## 청구항 4

삭제

#### 청구항 5

청구항 1에 있어서, 상기 제 1 단에 전원단이 연결되고 상기 제 4 단에 접지단이 연결되는 LUT 회로.

#### 청구항 6

청구항 5에 있어서, 상기 신호 입출력부는 상기 제 2단과 상기 제 3단 사이에서 직렬 연결되는 제 1 PMOS 트랜지스터와 제 1 NMOS 트랜지스터를 포함하되, 상기 제 1 PMOS 트랜지스터와 제 1 NMOS 트랜지스터의 공통 드레인이 제 1 노드에 연결되어 상기 제 1 노드를 통해 신호가 입출력되는 LUT 회로.

#### 청구항 7

청구항 6에 있어서, 제 1 시간 동안 상기 제 1 PMOS 트랜지스터와 상기 제 1 NMOS 트랜지스터는 모두 턴온되고, 상기 제 1 시간 경과 후 상기 제 1 PMOS 트랜지스터와 상기 제 1 NMOS 트랜지스터 중 적어도 하나는 턴오프되도록 상기 제 1 PMOS 트랜지스터와 상기 제 1 NMOS 트랜지스터의 케이트를 제어하는 신호 입출력 제어부를 더 포함하는 LUT 회로.

## 청구항 8

청구항 7에 있어서, 상기 신호 입출력 제어부는 상기 제 1 시간 동안 상기 신호 입출력부에서 출력된 출력 신호가 상기 제 1 시간 경과 후에도 유지되도록 상기 제 1 PMOS 트랜지스터와 상기 제 1 NMOS 트랜지스터의 게이트를 제어하는 LUT 회로.

## 청구항 9

청구항 8에 있어서, 상기 신호 입출력 제어부는 제 1 클록 신호와 상기 출력 신호를 노어 연산하여 상기 제 1 PMOS 트랜지스터의 게이트를 제어하는 노어 게이트와 상기 제 1 클록 신호와 위상이 반대인 제 2 클록 신호와 상기 출력 신호를 낸드 연산하여 상기 제 1 NMOS 트랜지스터의 게이트를 제어하는 낸드 게이트를 포함하는 LUT 회로.

## 청구항 10

청구항 9에 있어서, 상기 신호 입출력 제어부는 클록 신호와 쓰기 활성화 신호를 오어 연산하여 상기 제 1 클록 신호를 출력하는 오어 게이트와 상기 클록 신호와 상기 쓰기 활성화 신호를 노어 연산하여 상기 제 2 클록 신호 를 출력하는 노어 게이트를 더 포함하는 LUT 회로.

## 청구항 11

청구항 6에 있어서, 상기 신호 입출력부는 쓰기 동작 시 턴온되며 상기 제 1 PMOS 트랜지스터와 병렬 연결되는 제 2 NMOS 트랜지스터와 쓰기 동작 시 턴온되며 상기 제 1 NMOS 트랜지스터와 병렬 연결되는 제 2 PMOS 트랜지스터를 더 포함하는 LUT 회로.

## 청구항 12

청구항 6에 있어서, 쓰기 동작 시 상기 제 1 노드에 제 1 쓰기 신호를 제공하는 스위치, 상기 제 1 단에 제 2 쓰기 신호를 제공하는 스위치, 및 상기 제 4 단에 제 3 쓰기 신호를 제공하는 스위치를 더 포함하는 LUT 회로.

## 청구항 13

제 1 시간 동안 입력 신호에 대응하는 자기 소자의 상태에 따라 신호를 출력하는 다수의 제 2 LUT 회로; 및 상기 제 1 시간과 중첩되지 않는 제 2 시간 동안 상기 입력 신호에 대응하는 자기 소자의 상태에 따라 신호를 출력하는 다수의 제 3 LUT 회로

를 포함하는 FPGA.

#### 청구항 14

청구항 13에 있어서, 상기 제 2 LUT 회로는 상기 제 1 시간 동안 출력된 신호를 상기 제 1 시간 경과 후에도 유지하고 상기 제 3 LUT 회로는 상기 제 2 시간 동안 출력된 신호를 상기 제 2 시간 경과 후에도 유지하는 FPGA.

#### 청구항 15

청구항 13에 있어서, 상기 제 2 LUT 회로는

입력 신호에 따라 디코딩 신호를 출력하는 디코더;

상기 디코딩 신호에 대응하는 하나 또는 둘 이상의 자기 소자를 선택하는 저장부;

상기 저장부에서 선택된 자기 소자의 상태에 대응하는 신호를 출력하거나 상기 선택된 자기 소자의 상태를 변경할 신호를 입력받는 신호 입출력부; 및

상기 제 1 시간 동안 상기 디코딩 신호에 따라 선택된 자기 소자의 상태에 대응하는 신호를 출력하고, 상기 제 1 시간 경과 후 상기 저장부와 상기 신호 입출력부를 통해 전원단에서 접지단으로 흐르는 전류 경로를 차단하도록 상기 신호 입출력부를 제어하는 신호 입출력 제어부

를 포함하는 FPGA.

#### 청구항 16

청구항 15에 있어서,

상기 저장부는

제 1 단과 제 2 단 사이에 연결되며 다수의 자기 소자를 포함하며 상기 디코딩 신호를 반전한 신호에 따라 대응

하는 자기 소자를 선택하는 제 1 저장부; 및

제 3 단과 제 4 단 사이에 연결되며 다수의 자기 소자를 포함하며 상기 디코딩 신호에 따라 대응하는 자기 소자를 선택하는 제 2 저장부

를 포함하고,

상기 신호 입출력부는

상기 제 2단과 상기 제 3단 사이에서 직렬 연결되는 제 1 PMOS 트랜지스터와 제 1 NMOS 트랜지스터를 포함하되, 상기 제 1 PMOS 트랜지스터와 제 1 NMOS 트랜지스터의 공통 드레인이 제 1 노드에 연결되어 상기 제 1 노드를 통해 신호가 입출력되고,

상기 신호 입출력 제어부는

상기 제 1 시간 동안 상기 제 1 PMOS 트랜지스터와 상기 제 1 NMOS 트랜지스터는 모두 턴온되고, 상기 제 1 시간 경과 후 상기 제 1 PMOS 트랜지스터와 상기 제 1 NMOS 트랜지스터 중 적어도 하나는 턴오프되도록 상기 제 1 PMOS 트랜지스터와 상기 제 1 NMOS 트랜지스터의 게이트를 제어하는 FPGA.

## 청구항 17

청구항 13에 있어서, 상기 제 3 LUT 회로는

입력 신호에 따라 디코딩 신호를 출력하는 디코더;

상기 디코딩 신호에 대응하는 하나 또는 둘 이상의 자기 소자를 선택하는 저장부;

상기 저장부에서 선택된 자기 소자의 상태에 대응하는 신호를 출력하거나 상기 선택된 자기 소자의 상태를 변경할 신호를 입력받는 신호 입출력부; 및

상기 제 2 시간 동안 상기 디코딩 신호에 따라 선택된 자기 소자의 상태에 대응하는 신호를 출력하고, 상기 제 2 시간 경과 후 상기 저장부와 상기 신호 입출력부를 통해 전원단에서 접지단으로 흐르는 전류 경로를 차단하도록 상기 신호 입출력부를 제어하는 신호 입출력 제어부

를 포함하는 FPGA.

## 청구항 18

청구항 17에 있어서,

상기 저장부는

제 1 단과 제 2 단 사이에 연결되며 다수의 자기 소자를 포함하며 상기 디코딩 신호를 반전한 신호에 따라 대응하는 자기 소자를 선택하는 제 1 저장부; 및

제 3 단과 제 4 단 사이에 연결되며 다수의 자기 소자를 포함하며 상기 디코딩 신호에 따라 대응하는 자기 소자를 선택하는 제 2 저장부

를 포함하고,

상기 신호 입출력부는

상기 제 2단과 상기 제 3단 사이에서 직렬 연결되는 제 1 PMOS 트랜지스터와 제 1 NMOS 트랜지스터를 포함하되, 상기 제 1 PMOS 트랜지스터와 제 1 NMOS 트랜지스터의 공통 드레인이 제 1 노드에 연결되어 상기 제 1 노드를 통해 신호가 입출력되고,

상기 신호 입출력 제어부는

상기 제 2 시간 동안 상기 제 1 PMOS 트랜지스터와 상기 제 1 NMOS 트랜지스터는 모두 턴온되고, 상기 제 2 시간 경과 후 상기 제 1 PMOS 트랜지스터와 상기 제 1 NMOS 트랜지스터 중 적어도 하나는 턴오프되도록 상기 제 1 PMOS 트랜지스터와 상기 제 1 NMOS 트랜지스터의 게이트를 제어하는 FPGA.

#### 청구항 19

청구항 13에 있어서, 상기 제 1 시간은 클록 신호가 하이 레벨인 구간에 대응하고 상기 제 2 시간은 상기 클록 신호가 로우 레벨인 구간에 대응하는 FPGA.

#### 청구항 20

제 1 시간 동안 입력 신호에 대응하는 자기 소자의 상태에 따라 신호를 출력하는 다수의 제 2 LUT 회로; 및 상기 제 1 시간과 중첩하지 않는 제 2 시간 동안 상기 입력 신호에 대응하는 자기 소자의 상태에 따라 신호를 출력하는 다수의 제 3 LUT 회로를 포함하는 FPGA의 기술 맵핑 방법으로서.

입력된 게이트 레벨 넷리스트를 AIG(And-Inverter Graph)로 변환하는 단계;

AIG의 노드들을 순차적으로 선택하면서 선택된 매 노드에 대응하는 하나 또는 둘 이상의 컷들을 포함하는 컷 집합을 생성하고 상기 컷 집합에 포함된 컷들을 일정한 기준에 따라 정렬하여 어느 한 컷을 선택하는 단계; 및

상기 매 노드에 대해서 선택된 컷들을 포함하는 LUT 레벨 넷리스트를 출력하는 단계를 포함하되,

컷은 하나의 제 2 LUT 회로 또는 하나의 제 3 LUT 회로에 대응하는 하나 또는 둘 이상의 AIG의 노드들의 집합을 의미하고,

컷의 레벨 수는 컷과 AIG의 주 입력 노드 사이에 일렬로 연결된 컷들의 개수에 연관된 값이고,

상기 일정한 기준은 컷에 연결된 하위 컷들의 레벨 수의 최대 차이를 제 1 기준으로 하는 FPGA의 기술 맵핑 방법.

#### 청구항 21

청구항 20에 있어서, 상기 일정한 기준은 상기 제 1 기준에 의한 값이 동일한 컷이 존재하는 경우 컷에 대응하는 지연량을 제 2 기준으로 적용하고, 상기 제 2 기준에 의한 값이 동일한 컷이 존재하는 경우 상기 컷이 차지하는 면적을 제 3 기준으로 적용하는 FPGA의 기술 맵핑 방법.

## 발명의 설명

## 기 술 분 야

- [0001] 본 발명은 자기 소자를 포함하는 LUT(Look Up Table), 이를 포함하는 FPGA(Field Programmable Gate Array) 및 이에 사용되는 기술 맵핑 방법에 관한 것이다.

- [0002] 보다 구체적으로 본 발명은 스위칭 소자를 공유하여 셀의 면적을 줄이고 스태틱 전류를 줄일 수 있는 LUT, 이를 포함하는 FPGA 및 이에 사용되는 기술 맵핑 방법에 관한 것이다.

## 배경기술

- [0003] FPGA(Field Programmable Gate Array)는 프로그램을 통해 특정 동작을 수행하는 디지털 회로를 설계하는데 널리 사용되는 PLD(Programmable Logic Device)의 일종이다.

- [0004] FPGA는 CLB(Configurable Logic Block)와 IOB(Input Output Block) 및 둘 사이를 연결하는 구성 가능한 연결 회로를 포함한다. FPGA는 DLL, RAM 등의 구성을 더 포함할 수 있다.

- [0005] CLB는 적어도 두 종류의 하위 회로를 포함하는데 이 중 하나는 플립플롭과 같은 레지스터 회로이고 나머지 하나는 LUT로 구현될 수 있는 함수 생성 회로이다.

- [0006] 종래에는 다수의 SRAM과 MUX를 포함하여 MUX를 제어하는 입력 신호들의 조합에 따라 SRAM에 프로그램 된 데이터를 출력하여 함수 기능을 수행하는 LUT가 사용되었다.

- [0007] 이러한 종래의 LUT는 조합 논리 회로 및 순차 논리 회로를 구현하기 용이하나 전원이 차단되는 경우 SRAM에 저장된 데이터가 소멸되어 프로그램을 새로 수행해야 하는 문제가 있다.

- [0008] 이에 따라 SRAM 대신 자기 소자 등의 비휘발성 소자를 포함하는 LUT가 제안되었다.

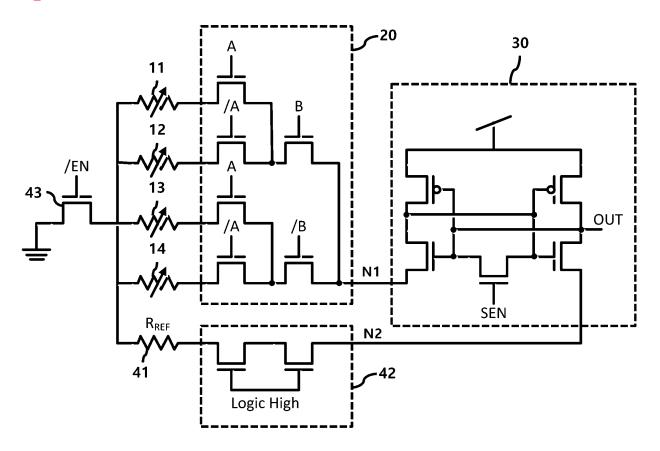

- [0009] 도 1은 종래의 MTJ를 포함하는 LUT(1) 회로를 나타낸다.

- [0010] 종래의 LUT(1)는 MTJ 셀(11, 12, 13, 14), 먹스(20), 센스앰프(30), 기준 저항(41), 제 1 스위치(42), 제 2 스위치(43)를 포함한다.

- [0011] LUT 회로의 동작 시 제 1 스위치(41)와 제 2 스위치(42)는 턴온 상태가 된다.

- [0012] 먹스(20)는 두 입력 신호(A, B)의 논리 레벨에 따라 MTJ 셀(11 14) 중 하나를 선택하여 제 1 노드(N1)에 연결한다.

- [0013] MTJ 셀(11 14)은 저저항 또는 고저항을 가지도록 미리 프로그램 된다. 또한 기준 저항(41)은 MTJ 셀의 저저항 과 고저항의 중간값을 가진다.

- [0014] 제 2 노드(N2)는 기준 저항(41)이 연결된다.

- [0015] 센스 앰프(30)는 동작 전에 센스 신호(SEN)를 활성화하여 프리차지 동작을 수행한다.

- [0016] 이후 센스 신호(SEN)가 비활성화되면 센스 앰프(30)는 선택된 MTJ 셀과 기준 저항의 차이에 따라 발생하는 전류 차이를 증폭하여 출력 신호(OUT)를 결정한다.

- [0017] 이러한 종래의 LUT(1)는 입력 신호(A, B)가 바뀔 때마다 센스 신호(SEN)를 활성화 후 비활성화 해야 하므로 입력 신호에 따라 출력 신호가 즉시 바뀌는 조합 논리 회로를 구성하기 곤란하며 클록 신호에 동기되는 순차 조합 논리 회로만을 구성할 수 있는 단점이 있다.

- [0018] 아울러 전류 모드로 동작하는 센스 앰프(30)의 특성 상 동작 속도가 상대적으로 느리다.

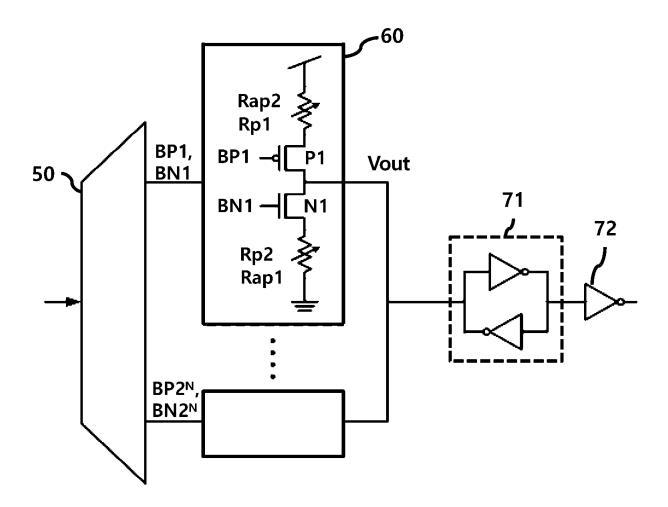

- [0019] 도 2는 종래의 또 다른 LUT(2) 회로를 나타낸다.

- [0020] 종래의 LUT(2)는 디코더(50), 다수의 자기 회로(60), 래치(71) 및 인버터(72)를 포함한다.

- [0021] 래치(71)는 다수의 자기 회로(60)의 출력을 반전하여 저장하고 인버터(72)는 래치(71)의 출력을 반전하여 출력 한다.

- [0022] 디코더(50)는 N:2<sup>N</sup> 디코더로 N개의 입력 신호를 디코딩하여 2<sup>N</sup> 개의 출력 신호를 선택한다.

- [0023] 도 2에서 디코더(50)는 N개의 선택 신호에 따라  $2^N$  개의 자기 회로 중 어느 하나를 활성화시키고 나머지는 비활성화시킨다.

- [0024] 자기 회로(60)가 활성화되는 경우는 PMOS 트랜지스터(P1), NMOS 트랜지스터(N1)가 모두 턴온되는 경우이고 자기 회로(60)가 비활성화되는 경우는 PMOS 트랜지스터(P1), NMOS 트랜지스터(N1)가 모두 턴오프되는 경우이다.

- [0025] 자기 회로(60)가 턴온되는 경우 출력 전압(Vout)은 상위 MTJ 셀과 PMOS 트랜지스터(N1)에 의한 상위 저항과 NMOS 트랜지스터(N1)과 하위 MTJ 셀에 의한 하위 저항의 비에 의해 결정된다.

- [0026] 도 2에서 선택된 자기 회로(60)는 신호 출력을 위하여 지속적으로 정전류가 흘러야 하므로 전력 소모가 큰 문제가 있다.

- [0027] 또한 다수의 자기 회로(60)가 하나의 래치(71)에 공통 연결되므로 자기 회로(60)의 출력 노드에서 기생 커패시턴스가 크게 되고 이에 따라 속도가 저하되는 문제가 있다.

- [0028] 또한 자기 회로(60) 내의 두 트랜지스터(N1, P1) 중 하나는 포화 영역에서 동작하고 나머지 하나는 선형 영역에 서 동작해야 하는데 이를 보장하기 위해서는 트랜지스터 자체의 크기가 커야 한다.

- [0029] 도 2에서 두 트랜지스터(N1, P1)는 각각의 자기 회로(60)마다 별도로 포함되므로 전체 회로의 면적이 증가하는 문제가 있다.

- [0030] 이에 따라 LUT 회로의 면적과 소비 전력을 줄일 수 있는 새로운 기술이 요구되고 있다.

## 선행기술문헌

#### 특허문헌

[0031] (특허문헌 0001) US 9437260 B2

## 비특허문헌

[0032] (비특허문헌 0001) S. Paul, S. Mukhopadhyay, and S. Bhunia, "Hybrid CMOS-STTRAM non-volatile FPGA: design challenges and optimization approaches," in Proceedings of the 2008 IEEE/ACM International Conference on Computer-Aided Design, ser. ICCAD '08. Piscataway, NJ, USA: IEEE Press, 2008, pp. 589-592.

(비특허문헌 0002) W. Zhao, E. Belhaire, C. Chappert, and P. Mazoyer, "Spin transfer torque (STT)-MRAM-based runtime reconfiguration FPGA circuit," ACM Trans. Embed. Comput. Syst., vol. 9, no. 2, pp. 14:1-14:16, Oct. 2009.

(비특허문헌 0003) Valavan Manohararajah, Stephen D. Brown and Zvonko G. Vranesic, "Heuristics for Area Minimization in LUT-Based FPGA Technology Mapping," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 25, issue. 11, pp. 2331 - 2340, Nov. 2006.

## 발명의 내용

[0034]

## 해결하려는 과제

- [0033] 본 발명은 회로 면적을 줄이고 소비 전력을 줄일 수 있는 LUT와 이를 포함하는 FPGA를 제공한다.

- 아울러 본 발명은 이러한 FPGA 장치를 사용하는데 적용할 수 있는 기술 맵핑 방법을 제공한다.

#### 과제의 해결 수단

- [0035] 본 발명의 일 실시예에 의한 LUT는 입력 신호에 따라 디코딩 신호를 출력하는 디코더, 디코딩 신호에 대응하는 하나 또는 둘 이상의 자기 소자를 선택하는 저장부 및 저장부에서 선택된 자기 소자의 프로그램 상태에 대응하는 신호를 출력하거나 선택된 자기 소자를 프로그램할 신호를 입력받는 신호 입출력부를 포함한다.

- [0036] 본 발명의 일 실시예에 의한 FPGA는 제 1 시간 동안 입력 신호에 대응하는 자기 소자의 프로그램 상태에 따라 신호를 출력하는 다수의 제 2 LUT; 및 제 2 시간 동안 입력 신호에 대응하는 자기 소자의 프로그램 상태에 따라 신호를 출력하는 다수의 제 3 LUT를 포함한다.

- [0037] 본 발명의 일 실시예에 의한 FPGA의 기술 맵핑 방법은 입력된 게이트 레벨 넷리스트를 AIG(And-Inverter Graph)로 변환하는 단계; AIG의 노드들을 순차적으로 선택하면서 선택된 매 노드에 대응하는 하나 또는 둘 이상의 컷들을 포함하는 컷 집합을 생성하고 상기 컷 집합에 포함된 컷들을 일정한 기준에 따라 정렬하여 어느 한 컷을 선택하는 단계; 및 매 노드에 대해서 선택된 컷들을 포함하는 LUT 넷리스트를 출력하는 단계를 포함하되, 일정한 기준은 컷에 연결된 하위 컷들의 레벨 수의 최대 차이를 제 1 기준으로 한다.

## 발명의 효과

- [0038] 본 발명에 의한 LUT는 자기 메모리를 포함하므로 전원 재개 시 프로그램을 새로 진행할 필요가 없다.

- [0039] 본 발명에 의한 LUT는 크기가 작은 스위칭 트랜지스터를 자기 소자마다 구비하고 크기가 상대적으로 큰 클램프 트랜지스터를 다수의 자기 소자에 대해서 공통적으로 사용하여 회로의 면적을 줄일 수 있다.

- [0040] 본 발명에 의한 LUT는 클록 신호를 이용하여 일정한 시간 동안만 정전류가 흐르도록 하여 소비 전력을 줄일 수 있다.

## 도면의 간단한 설명

[0041] 도 1은 종래 기술에 의한 LUT 회로도.

도 2는 종래 기술에 의한 LUT 회로도.

- 도 3은 본 발명의 일 실시예에 의한 LUT 회로도.

- 도 4는 본 발명의 다른 실시예에 의한 LUT 회로도.

- 도 5는 본 발명의 다른 실시예에 의한 LUT 회로도.

- 도 6은 본 발명의 일 실시예에 의한 FPGA에서의 기술 맵핑 방법을 설명하는 순서도.

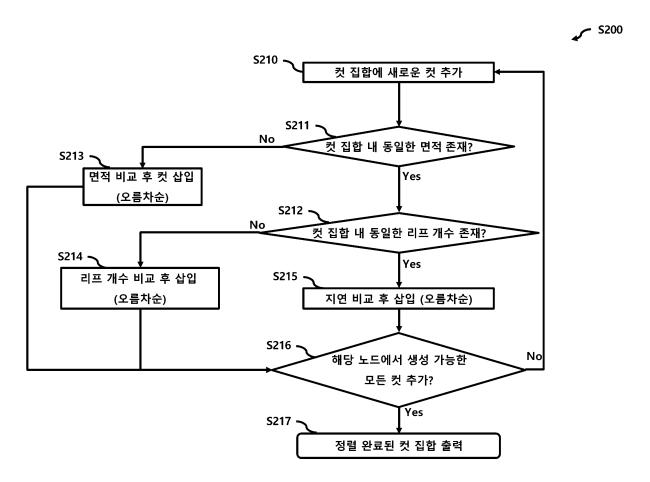

- 도 7은 도 6에서 정렬된 컷 집합 생성 방법을 나타낸 순서도.

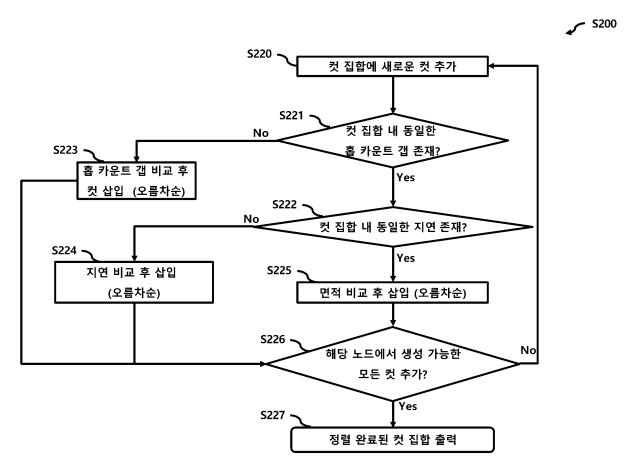

- 도 8은 도 6에서 정렬된 컷 집합 생성 방법을 나타낸 다른 순서도.

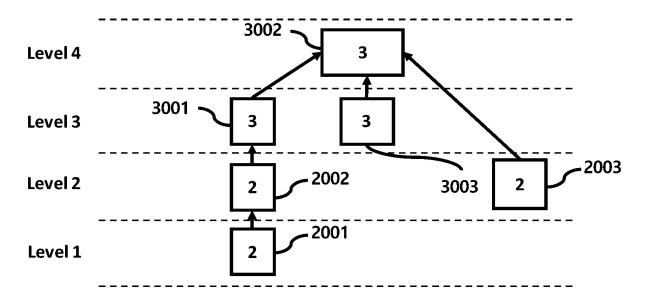

- 도 9는 본 발명의 일 실시예에 의한 FPGA에서 LUT 매칭 동작을 설명하는 설명도.

## 발명을 실시하기 위한 구체적인 내용

- [0042] 이하에서는 도면을 참조하여 본 발명의 실시예를 개시한다.

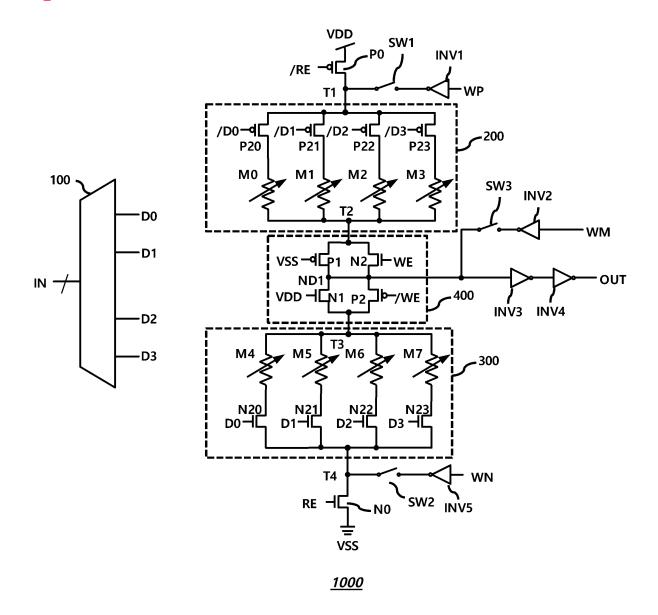

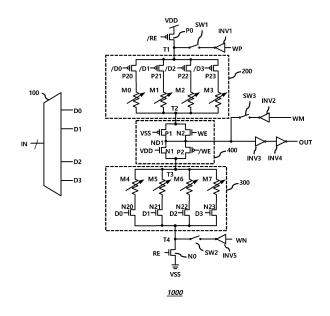

- [0043] 도 3은 본 발명의 일 실시예에 의한 LUT의 회로도이다.

- [0044] 본 실시예에서는 2비트 입력 신호를 위한 LUT의 회로를 예시한다. 다른 비트 수의 입력 신호에 대응하는 LUT 회로는 본 개시로부터 통상의 기술자가 용이하게 도출할 수 있을 것이다.

- [0045] 본 발명의 일 실시예에 의한 LUT(1000)는 디코더(100), 제 1 저장부(200), 제 2 저장부(300), 신호 입출력부 (400)를 포함한다.

- [0046] 본 실시예에서 디코더(100)는 2:4 디코더로서 2비트 입력 신호(IN)에 따라 4개의 디코딩 신호(D0, D1, D2, D3)를 출력한다. 이때 네 개의 디코딩 신호 중 어느 하나만 활성화되고 나머지는 비활성화된다.

- [0047] 제 1 저장부(200)는 제 1 단(T1)과 제 2 단(T2)을 구비하고 그 사이에서 직렬로 연결된 MTJ 셀과 스위칭 트랜지 스터의 쌍을 다수 개 포함한다.

- [0048] 도 3에서 제 1 저장부(200)는 4개의 MTJ 셀(MO, M1, M2, M3)과 이와 직렬 연결된 4 개의 PMOS 트랜지스터(P20, P21, P22, P23)를 포함한다.

- [0049] 4개의 PMOS 트랜지스터(P20, P21, P22, P23)에는 4개의 디코딩 신호(/D0, /D1, /D2, /D3)가 순차적으로 입력된 다

- [0050] 2비트 입력 신호(IN)에 따라 4개의 PMOS 트랜지스터(P20, P21, P22, P23) 중 어느 하나가 턴온되어 대응하는 MTJ 셀이 선택된다.

- [0051] 제 2 저장부(300)는 제 3 단(T3)과 제 4 단(T4)을 구비하고 그 사이에서 직렬로 연결된 MTJ 셀과 스위칭 트랜지 스터의 쌍을 다수 개 포함한다.

- [0052] 도 3에서 제 2 저장부(300)는 4개의 MTJ 셀(M4, M5, M6, M7)과 이와 직렬 연결된 4 개의 NMOS 트랜지스터(N20, N21, N22, N23)를 포함한다.

- [0053] 4개의 NMOS 트랜지스터(N20, N21, N22, N23)에는 4개의 디코딩 신호(D0, D1, D2, D3)가 순차적으로 입력된다.

- [0054] 2비트 입력 신호(IN)에 따라 4개의 NMOS 트랜지스터(N20, N21, N22, N23) 중 어느 하나가 턴온되어 대응하는 MTJ 셀이 선택된다.

- [0055] 신호 입출력부(400)는 제 1 저장부(200)의 제 2 단(T2)과 제 2 저장부(300) 의 제 3 단(T3) 사이에 연결된다.

- [0056] 신호 입출력부(400)는 읽기 동작 시 읽기 신호에 따라 제 1 저장부(200)와 제 2 저장부(300)의 대응하는 MTJ 셀의 프로그램 상태에 따라 신호를 출력한다.

- [0057] 본 실시예에서 신호 입출력부(400)는 제 1 저장부(200)와 제 2 저장부(300) 사이에 직렬 연결되며 게이트에 접 지 전압(VSS)이 인가되는 제 1 PMOS 트랜지스터(P1)와 게이트에 전원 전압(VDD)이 인가되는 제 1 NMOS 트랜지스터(N1)을 포함한다.

- [0058] 제 1 PMOS 트랜지스터(P1)와 제 1 NMOS 트랜지스터(N1)는 제 1 저장부(200), 제 2 저장부(300)를 통해 흐르는 전류를 고정하는 클램프 트랜지스터로 기능한다.

- [0059] 동작 시 제 1 PMOS 트랜지스터(P1)와 제 1 NMOS 트랜지스터(N1) 중 하나는 포화 영역에서 동작하고 나머지 하나

- 는 선형 영역에서 동작하는 것이 바람직하다.

- [0060] 이에 따라 제 1 PMOS 트랜지스터(P1)와 제 1 NMOS 트랜지스터(N1)의 크기는 제 1 저장부(200)와 제 2 저장부 (300)에 포함된 스위칭 트랜지스터(P20 ~ P23, N20 ~ N23)보다는 상대적으로 크게 설계될 수 있다.

- [0061] 제 1 노드(ND1)는 제 1 PMOS 트랜지스터(P1)와 제 1 NMOS 트랜지스터(N1)의 공통 노드로서 제 1 노드(ND1)에서 읽기 신호가 출력된다.

- [0062] LUT(1000)는 제 1 노드(ND1)의 출력을 버퍼링하여 출력신호(OUT)를 제공하는 2 개의 직렬 연결된 인버터(INV3, INV4)를 더 포함할 수 있다.

- [0063] 신호 입출력부(400)는 쓰기 동작 시 외부에서 인가된 신호를 제 1 저장부(200) 또는 제 2 저장부(300)에 제공한다.

- [0064] 본 실시예에서 LUT(1000)는 쓰기 신호(WE)에 의해 턴온되며 제 1 저장부(200)와 제 2 저장부(300) 사이에 직렬 연결된 제 2 NMOS 트랜지스터(N2)와 제 2 PMOS 트랜지스터(P2)를 더 포함할 수 있다.

- [0065] 제 2 PMOS 트랜지스터(P2)와 제 2 NMOS 트랜지스터(N2)는 쓰기 동작 시 제 1 저장부(200) 또는 제 2 저장부 (300)에 쓰기 전류가 추가로 제공될 수 있도록 한다.

- [0066] 제 2 PMOS 트랜지스터(P2)와 제 2 NMOS 트랜지스터(N2)의 공통 노드는 제 1 노드(ND1)와 연결된다.

- [0067] 또한 제 2 NMOS 트랜지스터(N2)는 제 1 PMOS 트랜지스터(P1)와 병렬로 연결되고, 제 2 PMOS 트랜지스터(P2)는 제 1 NMOS 트랜지스터(N1)와 병렬로 연결된다.

- [0068] LUT(1000)는 제 1 노드(ND1)에 제 1 쓰기 신호(WM)를 인가하는 스위치(SW3)와 인버터(INV2)를 더 포함할 수 있다.

- [0069] 본 실시예에 의한 LUT(1000)는 읽기 신호(RE)가 활성화되는 경우 턴온되어 제 1 저장부(200)에 전원 전압(VDD)을 인가하는 PMOS 트랜지스터(PO)를 더 포함할 수 있다.

- [0070] 이때 PMOS 트랜지스터(PO)는 전원단과 제 1 저장부(200)의 제 1 단(T1) 사이에 연결될 수 있다.

- [0071] 본 실시예에 의한 LUT(1000)는 읽기 신호(RE)가 활성화되는 경우 턴온되어 제 2 저장부(300)에 접지 전압을 인가하는 NMOS 트랜지스터(NO)를 더 포함할 수 있다.

- [0072] 이때 NMOS 트랜지스터(NO)는 접지단과 제 2 저장부(300)의 제 4 단(T4) 사이에 연결될 수 있다.

- [0073] 본 실시예에 의한 LUT(1000)는 쓰기 신호(WE)가 활성화되는 경우 제 2 쓰기 신호(WP)를 제 1 저장부(200)의 제 1 단(T1)에 인가하는 스위치(SW1)와 인버터(INV1)를 더 포함할 수 있다.

- [0074] 본 실시예에 의한 LUT(1000)는 쓰기 신호(WE)가 활성화되는 경우 제 3 쓰기 신호(WN)를 제 2 저장부(300)의 제 4 단(T4)에 인가하는 스위치(SW2)와 인버터(INV5)를 더 포함할 수 있다.

- [0075] 스위치(SW1 SW3)는 쓰기 신호(WE)가 활성화되는 경우 각각 독립적으로 제어되어 온오프될 수 있다.

- [0076] 도 3의 LUT(1000) 회로에서 읽기 동작을 설명하면 아래와 같다.

- [0077] 예를 들어 입력 신호(IN)가 "00"인 경우 디코딩 신호 중 DO는 활성화되고 나머지 디코딩 신호(D1 ~ D3)는 비활성화된다.

- [0078] 이에 따라 제 1 저장부(200)에서 스위칭 트랜지스터(P20)가 턴온되어 MTJ 셀(M0)이 신호 입출력부(400)에 연결되고 제 2 저장부(300)에서 스위칭 트랜지스터(N20)가 턴온되어 MTJ 셀(M4)이 신호 입출력부(400)에 연결된다.

- [0079] 이때 MTJ 셀(MO, M4)은 서로 반대 저항 상태를 가지도록 미리 프로그램된 상태이다.

- [0080] 예를 들어 MTJ 셀(MO)이 고저항 상태이고 MTJ 셀(M4)이 저저항 상태로 프로그램된 경우 제 1 노드(ND1)는 저항 분배에 의해 저전압 신호를 출력하고, 그 반대로 프로그램된 경우에는 고전압 신호를 출력한다.

- [0081] 도 3의 LUT(1000) 회로에서 쓰기 동작을 설명하면 아래와 같다.

- [0082] 쓰기 동작 시 읽기 신호(RE)가 비활성화되므로 트랜지스터(PO, NO)는 턴오프 상태가 된다.

- [0083] 예를 들어 입력 신호(IN)가 "00"인 경우 디코딩 신호 중 DO는 활성화되고 나머지 디코딩 신호(D1 ~ D3)는 비

활성화된다.

- [0084] 이에 따라 제 1 저장부(200)에서 스위칭 트랜지스터(P20)가 턴온되어 MTJ 셀(M0)이 신호 입출력부(400)에 연결되고 제 2 저장부(300)에서 스위칭 트랜지스터(N20)가 턴온되어 MTJ 셀(M4)이 신호 입출력부(400)에 연결된다.

- [0085] 예를 들어 MTJ 셀(MO)을 고저항 상태로 프로그램하고 MTJ 셀(M4)을 저저항 상태로 프로그램하는 경우를 가정한다.

- [0086] 먼저 스위치(SW1, SW3)를 턴온하고, 스위치(SW2)를 턴오프한다.

- [0087] 또한 쓰기 신호(WM)에 하이 레벨을 인가하고 쓰기 신호(WP)에 하이 레벨을 인가한다. 이에 따라 MTJ 셀(MO)은 고저항 상태로 프로그램된다.

- [0088] 제 2 NMOS 트랜지스터(N2)는 쓰기 동작 시 턴온되어 MTJ 셀(M0)에 쓰기 전류를 추가로 제공할 수 있다.

- [0089] 이후 스위치(SW2, SW3)를 턴온하고, 스위치(SW1)를 턴오프한다.

- [0090] 이때 쓰기 신호(WM)에 하이 레벨을 유지하고 쓰기 신호(WN)에 로우 레벨을 인가한다. 이에 따라 MTJ 셀(M4)은 저저항 상태로 프로그램된다.

- [0091] 제 2 PMOS 트랜지스터(P2)는 쓰기 동작 시 턴온되어 MTJ 셀(M4)에 쓰기 전류를 추가로 제공할 수 있다.

- [0092] 이와 같이 본 실시예에서는 클램프 트랜지스터인 제 1 PMOS 트랜지스터 및 제 1 NMOS 트랜지스터(P1, N1)를 다수의 MTJ 셀에 대해서 공유하여 사용하므로 종래의 기술에 비하여 회로 면적을 줄일 수 있는 효과가 있다.

- [0093] 도 3의 LUT(1000)는 입력 신호(IN)의 변화에 의해 출력 신호(OUT)가 실질적으로 즉시 변경되므로 조합 논리 회로를 구성하는데 용이하며 출력 신호(OUT)를 래치하는 회로를 부가함으로써 순차 논리 회로를 구성하는데도 용이하게 사용할 수 있다.

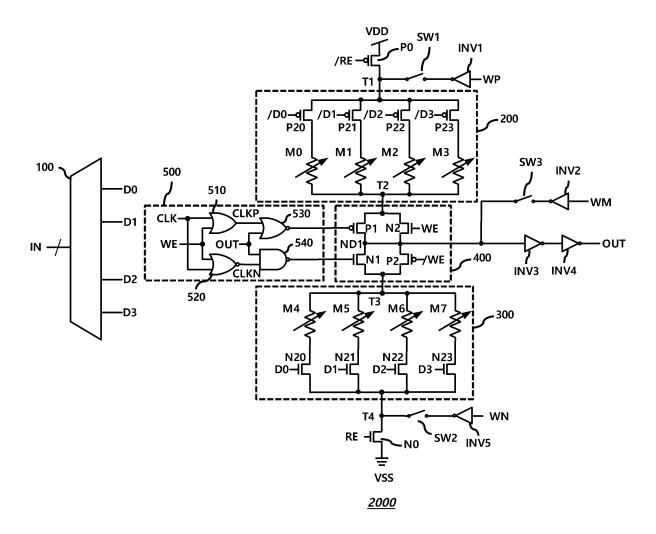

- [0094] 도 4는 본 발명의 다른 실시예에 의한 LUT의 회로도이다.

- [0095] 도 4에 도시된 실시예는 신호 입출력 제어부(500)를 더 포함하는 점에서 도 3의 실시예와 상이하다.

- [0096] 도 3에서 신호 입출력부(400)의 제 1 PMOS 트랜지스터(P1)의 게이트에는 전원 전압(VDD)이 인가되고 제 1 NMOS 트랜지스터(N1)의 게이트에는 접지 전압(VSS)이 인가된다.

- [0097] 도 4의 실시예에서 신호 입출력부(400)의 제 1 PMOS 트랜지스터(P1)와 제 1 NMOS 트랜지스터(N1)의 게이트 전압은 신호 입출력 제어부(500)에 의해 제어된다.

- [0098] 본 실시예에서 신호 입출력 제어부(500)는 클록 신호(CLK)와 출력 신호(OUT)에 따라 제 1 PMOS 트랜지스터와 제 1 NMOS 트랜지스터(P1, N1)의 게이트를 제어한다.

- [0099] 클록 신호(CLK)로부터 제 1 클록 신호(CLKP)와 제 2 클록 신호(CLKN)가 생성된다.

- [0100] 쓰기 신호(WE)가 활성화된 경우에는 제 1 클록 신호(CLKP)는 하이 레벨로 고정되고 제 2 클록 신호(CLKN)는 로우 레벨로 고정된다.

- [0101] 이에 따라 도 3의 실시예에서와 같이 제 1 PMOS 트랜지스터(P1)의 게이트에는 전원 전압(VDD)이 인가되고 제 1 NMOS 트랜지스터(N1)의 게이트에는 접지 전압(VSS)이 인가된다.

- [0102] 쓰기 신호(WE)가 비활성화된 경우 클록 신호(CLK)로부터 클록 신호(CLK)와 실질적으로 동일한 위상을 가지는 제 1 클록 신호(CLKP)와 실질적으로 반대 위상을 가지는 제 2 클록 신호(CLKN)가 생성된다.

- [0103] 이를 위하여 도 4에서 신호 입출력 제어부(500)는 클록 신호(CLK)와 쓰기 신호(WE)를 오어 연산하여 제 1 클록 신호(CLKP)를 출력하는 오어 게이트(510)와 클록 신호(CLK)와 쓰기 신호(WE)를 노어 연산하여 제 2 클록 신호 (CLKN)를 출력하는 노어 게이트(520)를 포함한다.

- [0104] 신호 입출력 제어부(500)는 제 1 클록 신호(CLKP)와 출력 신호(OUT)를 노어 연산하여 제 1 PMOS 트랜지스터(P 1)의 게이트를 제어하는 노어 게이트(530)와 제 2 클록 신호(CLKN)와 출력 신호(OUT)를 낸드 연산하여 제 1 NMOS 트랜지스터(N1)의 게이트를 제어하는 낸드 게이트(530)를 포함한다.

- [0105] 출력 신호(OUT)가 로우 레벨인 경우 낸드 게이트(540)의 출력은 하이 레벨로 고정되고 노어 게이트(530)의 출력은 제 1 클록 신호(CLKP)의 반대 레벨을 가진다.

- [0106] 이에 따라 제 1 NMOS 트랜지스터(N1)는 턴온 상태를 유지하는데 비하여, 제 1 PMOS 트랜지스터(P1)는 클록 신호 (CLK)가 하이 레벨인 경우 턴온 상태가 되고 클록 신호(CLK)가 로우 레벨인 경우 턴오프 상태가 된다.

- [0107] 출력 신호(OUT)가 하이 레벨인 경우 노어 게이트(530)의 출력은 로우 레벨로 고정되고 낸드 게이트(540)의 출력은 제 2 클록 신호(CLKN)의 반대 레벨을 가진다.

- [0108] 이에 따라 제 1 PMOS 트랜지스터(P1)는 턴온 상태를 유지하는데 비하여, 제 1 NMOS 트랜지스터(N1)는 클록 신호 (CLK)가 하이 레벨인 경우 턴온 상태가 되고 클록 신호(CLK)가 로우 레벨인 경우 턴오프 상태가 된다.

- [0109] 이와 같이 도 4의 실시예에서 신호 입출력 제어부(500)는 클록 신호가 하이 레벨인 상태에서 제 1 PMOS 트랜지스터 및 제 1 NMOS 트랜지스터(P1, N1)를 모두 턴온하여 정상적인 신호를 출력한다.

- [0110] 클록 신호가 로우 레벨인 경우 출력 신호(OUT)에 따라 제 1 PMOS 및 제 1 NMOS 트랜지스터(P1, N1) 둘 중 하나 만 턴온되므로 신호 입출력부(400)를 관통하는 정전류는 차단된다.

- [0111] 예를 들어 출력 신호(OUT)가 하이 레벨인 경우 제 1 PMOS 트랜지스터(P1)만 턴온되어 출력 신호(OUT)가 하이 레벨로 유지되고, 출력 신호(OUT)가 로우 레벨인 경우 제 1 NMOS 트랜지스터(N1)만 턴온되어 출력 신호(OUT)가 로우 레벨로 유지된다.

- [0112] 이에 따라 읽기 동작 시 제 1 저장부(200)와 신호 입출력부(400) 및 제 2 저장부(300)를 관통하여 흐르는 정전 류는 클록 신호의 반주기 동안만 흐르게 되어 전력 소비가 줄어들 수 있다.

- [0113] 이와 같이 도 4의 LUT 회로는 입력 신호(IN)의 변화에 의해 출력 신호(OUT)가 실질적으로 즉시 변경되는 조합 논리 회로를 구성할 수 있으나 이것이 클록 신호(CLK)의 반주기 동안으로 제한된다.

- [0114] 도 4에 도시된 LUT 회로는 클록 신호가 하이 레벨인 구간에서 입력 신호에 대응하는 신호를 출력하는데 이로부터 클록 신호가 로우 레벨인 구간에서 입력 신호에 대응하는 신호를 출력하는 LUT 회로를 도출할 수 있다.

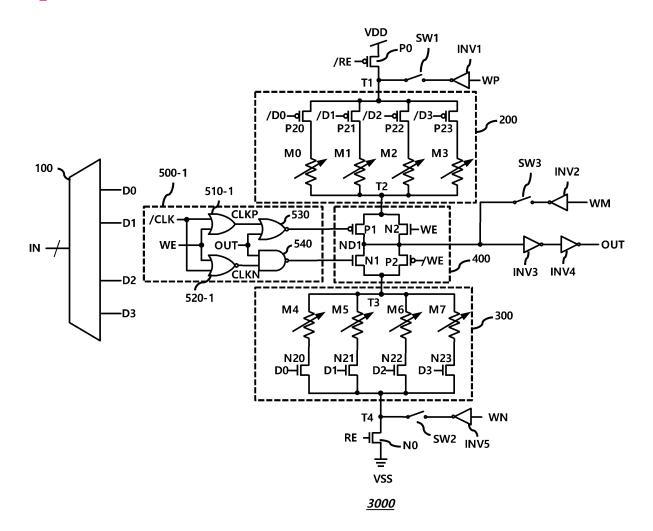

- [0115] 예를 들어 도 5와 같이 오어 게이트(510-1)와 노어 게이트(520-1)에 클록 신호(CLK) 대신에 이를 반전한 클록 신호(/CLK)를 인가함으로써 이러한 LUT 회로를 구현할 수 있을 것이다.

- [0116] 도 5의 LUT(3000)는 신호 입력 제어부(520-1)에 클록 신호(CLK)를 반전한 클록 신호(/CLK)가 인가되는 점을 제외하고 도 4의 LUT(2000)와 실질적으로 동일하다.

- [0117] 이하에서는 도 3에 도시된 LUT를 제 1 LUT(1000), 도 4에 도시된 LUT(2000)를 제 2 LUT, 도 5에 도시된 LUT(2000-1)를 제 3 LUT로 지칭할 수 있다.

- [0118] 일반적으로 FPGA는 다수의 LUT를 포함하며 원하는 디지털 논리 회로로 동작하도록 프로그램 된다.

- [0119] 본 발명의 일 실시예에 의한 FPGA는 제 1 LUT(1000), 제 2 LUT(2000), 제 3 LUT(3000) 중 적어도 한 종류의 LUT를 포함할 수 있다.

- [0120] 특히 본 발명의 일 실시예에 의한 FPGA는 제 2 LUT와 제 3 LUT를 동시에 포함할 수 있다.

- [0121] 이는 FPGA가 클록 신호의 반주기 동안 동작하는 LUT와 클록 신호의 나머지 반주기 동안 동작하는 LUT를 모두 포함하는 것을 의미한다.

- [0122] FPGA가 원하는 디지털 논리 회로로 동작하도록 하기 위해서는 프로그램을 통해 그 내부에 포함된 다수의 LUT를 연결하는 작업이 필요한데 이러한 작업을 기술 맵핑(Technology Mapping)이라고 한다.

- [0123] 보다 구체적으로 기술 맵핑은 디지털 논리 회로를 기술하는 게이트 레벨의 넷리스트를 FPGA의 구성 단위인 LUT 레벨의 넷리스트로 변환하는 작업을 지칭한다.

- [0124] 본 발명의 일 실시예에 의한 FPGA 중에서 제 2 LUT(2000) 및 제 3 LUT(3000)와 같이 클록 신호의 서로 다른 위상에서 동작하는 LUT를 함께 포함하는 실시예에 종래의 기술 맵핑을 그대로 적용하는 경우 제 2 LUT와 제 3 LUT를 균일하게 사용하지 못하여 효율이 떨어지는 문제가 있다. 이에 따라 본 실시예에 적합한 기술 맵핑 방법이요구된다.

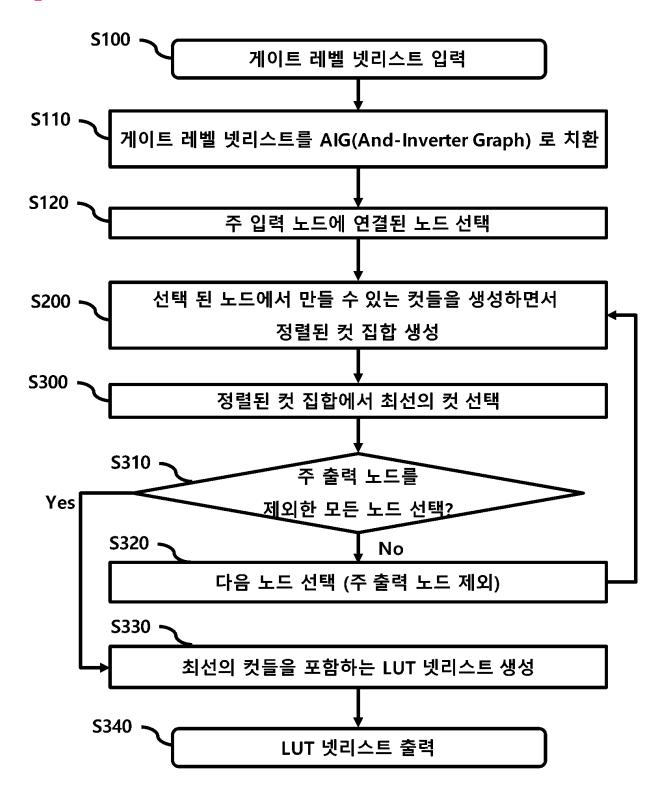

- [0125] 도 6은 본 발명의 일 실시예에 의한 FPGA 장치에서의 기술 맵핑 방법을 설명하는 순서도이다.

- [0126] 먼저 게이트 레벨의 넷리스트(netlist)가 입력된다(S100).

- [0127] 다음으로 게이트 레벨 넷리스트를 앤드-인버터 그래프(AIG: AND-INVERTER GRAPH)로 치환한다(S110).

- [0128] 다음으로 주 입력 노드에 연결된 노드를 선택한다(S120).

- [0129] AIG에서 각 노드는 낸드 게이트 또는 앤드 게이트 중 어느 하나에 대응하게 되는데 이때 하나의 LUT 를 이용하여 만들 수 있는 하나 또는 둘 이상의 노드들의 집합을 컷으로 지칭할 수 있다.

- [0130] 그래프에서 신호 입력단은 주 입력 노드로 표현되며 신호 출력단은 주 출력 노드로 표현된다. 주 입력 노드와 주 출력 노드는 게이트가 아닌 입력단 또는 출력단 그 자체에 대응한다.

- [0131] 이후 선택된 노드에서 만들 수 있는 모든 컷을 생성하면서 정렬된 컷 집합을 생성한다(S200).

- [0132] 이때 컷이란 하나의 LUT에 포함될 수 있는 노드들의 집합인데 선택된 노드에서 만들 수 있는 컷은 선택된 노드를 포함하여 다른 노드를 더 포함하거나 포함하지 않을 수 있다.

- [0133] 선택된 노드에서 만들 수 있는 컷은 하나 이상이 될 수 있으며 컷 집합은 이들을 포함하는 집합으로서 일정한 기준에 의해 정렬될 수 있다.

- [0134] 예를 들어 해당 컷을 사용하는 경우의 면적, 해당 컷을 사용하는 경우의 지연량 등을 다른 컷을 사용하는 경우의 면적이나 지연량과 비교하여 정렬할 수 있다.

- [0135] 이와 같이 정렬된 컷 집합에서 가장 바람직한 컷을 선택한다(S300).

- [0136] 바람직한 컷은 면적을 가정 적게 소모하도록 하는 컷, 지연량을 최소로 하는 컷 등에 대응할 수 있다.

- [0137] 이후 주 출력 노드를 제외한 모든 노드를 선택하였는지 확인한다(S310).

- [0138] 주 출력 노드를 제외하고 모든 노드가 선택된 상태가 아니라면 다음 노드를 선택하여 단계(S200)로 돌아간다.

- [0139] 만일 주 출력 노드를 제외한 모든 노드를 선택하였다면 모든 노드에 대해서 최선의 컷이 선택된 상태로서 이들 최선의 컷들을 포함하는 LUT 넷리스트를 생성한다(S330).

- [0140] 마지막으로 생성된 LUT 넷리스트를 출력한다(S340).

- [0141] 도 7은 도 6에서 정렬된 컷 집합을 생성하는 단계(S200)를 구체적으로 나타낸 순서도이다.

- [0142] 도 7의 실시예는 FPGA내에 제 1 LUT(1000)만이 포함되는 경우에 유리하게 사용될 수 있다.

- [0143] 도 7의 실시예는 면적, 리프 개수, 지연량 순으로 우선 순위를 가지고 컷 집합 내에서 컷들을 정렬한다.

- [0144] 먼저 컷 집합에 새로운 컷이 추가된다(S210).

- [0145] 새로운 컷에 대응하는 면적을 계산하고 컷 집합에 포함된 다른 컷들 중에 동일한 면적에 대응하는 것이 있는지 판단한다(S211).

- [0146] 이때 면적은 해당 것이 차지하는 면적으로서 것의 면적을 산정하여 면적에 따라 정렬하는 기술은 비특허문헌 3 과 같이 종래 기술을 통해 산출할 수 있는 것이므로 구체적인 설명은 생략한다.

- [0147] 면적이 동일한 것이 없는 경우 면적을 기준으로 오름 차순이 되도록 새로운 컷을 기존 컷들 사이에 삽입하고 (S213), 단계(S216)로 진행한다.

- [0148] 면적이 동일한 것이 있는 경우 새로운 컷에 대응하는 리프 개수를 계산하고 컷 집합에 포함된 면적이 동일한 컷 들 중에 리프 개수가 동일한 것이 있는지 판단한다(S212). 이때 리프는 컷에 포함된 노드들을 지칭한다.

- [0149] 리프 개수가 동일한 것이 없는 경우 리프 개수를 기준으로 오름 차순이 되도록 새로운 컷을 기존 컷들 사이에 삽입하고(S214), 단계(S216)로 진행한다.

- [0150] 리프 개수가 동일한 것이 있는 경우 새로운 컷에 대응하는 지연을 계산하고 지연을 기준으로 오름차순이 되도록 새로운 컷을 기존 컷들 사이에 삽입한다(S215). 컷에서의 지연량 계산은 게이트를 통과하는 시간을 산출하는 것인데 이는 종래의 기술을 통해 용이하게 알 수 있는 것이므로 구체적인 설명은 생략한다.

- [0151] 이후 해당 노드에서 생성 가능한 모든 컷을 추가했는지 판단한다(S216).

- [0152] 모든 컷을 추가한 경우 정렬 완료된 컷 집합을 출력하고(S217), 그렇지 않은 경우 단계(S210) 이하의 동작을 반복한다.

- [0153] 도 8은 도 6에서 정렬된 컷 집합을 생성하는 단계(S200)를 구체적으로 나타낸 다른 순서도이다.

- [0154] 도 8의 실시예는 FPGA내에 제 2 LUT(2000)와 제 3 LUT(3000)가 같은 개수로 함께 포함되는 경우에 유리하게 사용될 수 있다.

- [0155] 도 8의 실시예는 홉 카운트 갭, 지연, 면적 순으로 우선 순위를 가지고 컷 집합 내에서 컷들을 정렬한다.

- [0156] 홉 카운트 갭은 현재 컷에 연결된 하위 컷들의 레벨 수의 최대 차이를 나타낸다.

- [0157] 예를 들어 현재 컷이 두 개의 하위 컷들과 연결되는 경우 하나는 하위 레벨 개수가 3이고 나머지 하나는 0인 경우 홉 카운트 갭은 3이 된다.

- [0158] 본 실시예에서는 컷에 대응하는 홉 카운트 갭이 작을수록 바람직한 컷으로 본다.

- [0159] 먼저 컷 집합에 새로운 컷이 추가된다(S210).

- [0160] 새로운 컷에 대해서 홉 카운트 갭을 계산하고 이를 컷 집합 내의 다른 컷들의 합 카운트 갭과 비교하여 동일한 것이 있는지 판단한다(S221).

- [0161] 홉 카운트 갭이 동일한 것이 없으면 홉 카운트 갭을 기준으로 오름 차순이 되도록 현재 컷을 기존 컷들 사이에 끼워 넣고(S223), 단계(S226)로 진행한다.

- [0162] 홉 카운트 갭이 동일한 것이 있으면 새로운 컷에 대응하는 지연을 계산하고 컷 집합에 포함된 홉 카운트 갭이 동일한 컷들 중에 지연이 동일한 것이 있는지 판단한다(S222).

- [0163] 지연이 동일한 것이 없는 경우 지연을 기준으로 오름 차순이 되도록 새로운 컷을 기존 컷들 사이에 삽입하고 (S224), 단계(S226)로 진행한다.

- [0164] 지연이 동일한 것이 있는 경우 새로운 컷에 대응하는 면적을 계산하고 면적을 기준으로 오름차순이 되도록 새로 운 컷을 기존 컷들 사이에 삽입한다(S225).

- [0165] 이후 해당 노드에서 생성 가능한 모든 컷을 추가했는지 판단한다(S226).

- [0166] 모든 컷을 추가한 경우에는 LUT 넷리스트를 출력하고(S227), 모든 컷을 추가하지 않은 경우 단계(S220) 이하의 동작을 반복한다.

- [0167] FPGA가 제 2 LUT(2000)와 제 3 LUT(3000)를 동일하게 포함하는 경우 도 6 및 도 8의 순서도에 따라 출력된 LUT 넷리스트에 대해서 각 LUT를 제 2 LUT(2000) 또는 제 3 LUT(3000) 중 어느 하나로 매칭시키는 동작을 추가로 수행할 수 있다.

- [0168] 예를 들어 출력된 LUT 넷리스트에 포함된 각 LUT는 제 2 LUT(2000) 또는 제 3 LUT(3000) 중 어느 하나로 고정되어 매칭될 수도 있고, 제 2 LUT(2000) 또는 제 3 LUT(3000) 중 임의의 하나로 유동적으로 매칭될 수 있다.

- [0169] 도 9는 LUT 넷리스트에 포함된 각 LUT의 종류를 매칭하는 방법을 설명한다.

- [0170] LUT 넷리스트가 완성되면 도 8과 같이 가장 긴 신호 전달 경로를 기준으로 각 LUT의 레벨을 구분할 수 있다.

- [0171] 도면에서 사각형은 각각의 LUT를 나타내고 화살표는 신호 전달 경로를 나타내며 사각형 내의 숫자는 해당 LUT가 제 2 LUT(2000) 또는 제 3 LUT(3000) 중 어느 것에 매칭되는지를 표시하는데 숫자 2는 제 2 LUT(2000)에 매칭된 것을 나타내고 숫자 3은 제 3 LUT(3000)에 매칭된 것을 나타낸다.

- [0172] 제 2 LUT(2000)는 클록 신호가 하이 레벨이 경우 신호를 출력하고 제 3 LUT(3000)는 클록 신호가 로우 레벨인 경우 신호를 출력한다.

- [0173] 이에 따라 4개의 레벨을 반으로 나누어 하위 레벨에 포함되는 LUT는 제 2 LUT(2000)로 매칭하고 상위 레벨에 포함되는 LUT는 제 3 LUT(3000)로 매칭하다.

- [0174] 이에 따라 도 9에서 LUT(2001, 2002)는 제 2 LUT(2000)로 매칭되고, LUT(3001, 3002)는 제 3 LUT(3000)로 매칭된다.

- [0175] 도 9에서 LUT(2003, 3003)는 레벨 1 내지 3 중 어느 것에 속해도 무방하다.

- [0176] 이러한 LUT들은 제 2 LUT(2000) 또는 제 3 LUT(3000) 중 어느 하나로 유동적으로 매칭될 수 있다.

- [0177] 다만 최종적으로 매칭되는 경우 제 2 LUT(2000)로 매칭된 LUT의 개수와 제 3 LUT(3000)로 매칭된 LUT의 개수는 1:1에 가까울수록 바람직하다.

- [0178] 도 9의 예에서는 LUT(2003)를 제 2 LUT(2000)로 매칭시키고, LUT(3003)를 제 3 LUT(3000)로 매칭시켰다.

- [0179] 이에 따라 전체 LUT 6개 중에서 3개는 제 2 LUT(2000)로 매칭되고 나머지 3개는 제 3 LUT(3000)로 매칭될 수 있다.

- [0180] 본 발명의 발명자들은 제 2 LUT(2000)와 제 3 LUT(3000)가 균등한 개수로 포함되는 FPGA에서 기술 맵핑을 수행하는 경우 전술한 홉 카운트 갭이 작은 순서로 최선의 컷을 선택하는 경우 최종적으로 제 2 LUT(2000)와 제 3 LUT(3000)를 균등하게 사용하는데 유리함을 발견하였다.

- [0181] 이상에서 도면을 참조하여 본 발명의 실시예를 개시하였으나 이상의 개시가 본 발명의 권리범위를 한정하는 것은 아니다. 본 발명의 권리범위는 아래의 특허청구범위에 문언적으로 기재된 범위와 그 균등 범위로 정해질 수 있다.

## 부호의 설명

[0182] 1, 2: 종래의 LUT

10: 먹스

30: 센스 앰프

50, 100: 디코더

60: 자기 회로

200: 제 1 저장부

300: 제 2 저장부

400: 신호 입출력부

500, 500-1: 신호 입출력 제어부

1000: 제 1 LUT

2000: 제 2 LUT

3000: 제 3 LUT

# 도면1

<u>1</u>

<u>2</u>