## (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

G06F 7/544 (2017.01) G06N 3/063 (2006.01) G11C 7/12 (2006.01) G11C 8/08 (2006.01) H03M 1/12 (2006.01) H03M 1/66 (2006.01)

(52) CPC특허분류

**G06F** 7/544 (2018.05) **G06N** 3/063 (2013.01)

(21) 출원번호 10-2019-0126711

(22) 출원일자 **2019년10월14일** 심사청구일자 **2019년10월14일**

(56) 선행기술조사문헌

KR1020180101276 A\*

US20190042199 A1\*

US20190205729 A1\*

\*는 심사관에 의하여 인용된 문헌

(45) 공고일자 2021년03월08일

(11) 등록번호 10-2225558

(24) 등록일자 2021년03월03일

(73) 특허권자

#### 연세대학교 산학협력단

서울특별시 서대문구 연세로 50 (신촌동, 연세대 학교)

(72) 발명자

#### 정성욱

서울특별시 서대문구 연세로 50, 제3공학관 C513 (신촌동, 연세대학교)

#### 이영규

서울특별시 서대문구 연세로 50, 제3공학관 C206 (신촌동, 연세대학교)

(뒷면에 계속)

(74) 대리인

특허법인우인

전체 청구항 수 : 총 15 항

심사관 : 지정훈

#### (54) 발명의 명칭 온칩 활성화 함수가 구현된 아날로그 신호 전달 기반의 멀티 레이어 연산 회로

#### (57) 요 약

본 실시예들은 곱셈 및 덧셈을 수행하는 복수의 연산 영역으로 구분된 연산 메모리를 포함하고, 복수의 연산 영역은 학습 네트워크의 레이어로 동작하고, 아날로그 버퍼가 복수의 연산 영역에 연결되어 데이터를 하나의 연산 영역에서 다른 연산 영역으로 전송함으로써, 학습 네트워크의 레이어 간에 데이터 전송 시간을 최소화할 수 있는 멀티 레이어 연산 회로를 제공한다.

#### 대 표 도 - 도2

멀티 레이어 연산 회로 (200)

> 연산 메모리 **(210)**

아날로그 버퍼 (220) (52) CPC특허분류

*G11C 7/12* (2013.01) *G11C 8/08* (2013.01)

**HO3M 1/12** (2019.01) **HO3M 1/66** (2019.01)

(72) 발명자

#### 송병규

서울특별시 서대문구 연세로 50, 제3공학관 C206( 신촌동, 연세대학교)

이 발명을 지원한 국가연구개발사업

과제고유번호 SRFC-IT1802-06

부처명 삼성미래기술육성재단 과제관리(전문)기관명 연세대학교 산학협력단

연구사업명 ICT 창의과제

연구과제명 실시간 초해상도 복원작업에 적용 가능한 저전력 신경망 단일 칩 기술개발

기 여 율 1/1

과제수행기관명 삼성전자(주)

연구기간 2018.12.01 ~ 2020.11.30

서울특별시 서대문구 연세로 50, 제3공학관 C206( 신촌동, 연세대학교)

#### 명 세 서

### 청구범위

#### 청구항 1

아날로그 입력 신호를 입력받고 상기 아날로그 입력 신호를 처리하여 아날로그 출력 신호를 출력하는 복수의 연 산 영역을 포함하는 연산 메모리; 및

상기 복수의 연산 영역에 연결되어 상기 아날로그 출력 신호를 하나의 연산 영역에서 다른 연산 영역으로 전송 하는 아날로그 버퍼를 포함하며,

상기 연산 영역은 학습 네트워크의 레이어로 동작하며,

상기 연산 메모리 및 상기 아날로그 버퍼는 제어부로부터 제어 신호를 수신하고,

상기 제어 신호는 상기 하나의 연산 영역에서 상기 아날로그 버퍼로 상기 아날로그 출력 신호가 전송되고 상기 아날로그 버퍼의 안정화 시간이 지난 후에 상기 다른 연산 영역을 동작시키도록 상기 연산 메모리 및 상기 아날 로그 버퍼의 동작 시간을 제어하며,

상기 제어부는 상기 제어 신호에 상기 동작 시간을 포함시켜 전송하거나, 상기 연산 메모리 및 상기 아날로그 버퍼는 다음 순서의 소자로 완료 신호를 전송하고 상기 다음 순서의 소자는 상기 완료 신호를 수신하여 상기 동 작 시간을 설정하여, 상기 아날로그 버퍼에서 안정화 전의 일부 신호가 일부 연산 영역의 신호와 중첩되지 않도 록 하고, 상기 아날로그 버퍼에서 안정화 전의 일부 신호가 다른 연산 영역으로 전송되지 않도록 하는 것을 특 장으로 하는 멀티 레이어 연산 회로.

#### 청구항 2

삭제

#### 청구항 3

제1항에 있어서,

상기 연산 영역은 복수의 워드 라인, 복수의 비트 라인, 및 복수의 메모리 셀을 포함하고,

상기 메모리 셀은 가중치를 저장하고,

상기 워드 라인과 상기 비트 라인은 상기 메모리 셀에 연결되는 것을 특징으로 하는 멀티 레이어 연산 회로.

#### 청구항 4

제3항에 있어서.

상기 연산 영역은 (i) 상기 아날로그 입력 신호와 상기 가중치를 곱하여 출력하는 곱셈 영역과 (ii) 상기 곱셈 영역의 출력을 누산하여 상기 아날로그 출력 신호를 출력하는 누산 영역을 포함하는 것을 특징으로 하는 멀티 레이어 연산 회로.

#### 청구항 5

제4항에 있어서,

상기 누산 영역은 상기 복수의 비트 라인이 포지티브 라인 및 네거티브 라인에 연결되어 전하 공유(Charge Sharing) 방식으로 상기 곱셈 영역의 출력을 누산하는 것을 특징으로 하는 멀티 레이어 연산 회로.

### 청구항 6

제1항에 있어서,

상기 아날로그 버퍼는 상기 아날로그 버퍼에 입력된 신호가 0보다 작으면 0을 출력하고, 상기 아날로그 버퍼에 입력된 신호가 0보다 크면 상기 아날로그 버퍼에 입력된 신호를 그대로 출력하는 것을 특징으로 하는 멀티 레이 어 연산 회로.

#### 청구항 7

제1항에 있어서,

상기 아날로그 버퍼의 등가 회로는 연산 증폭기의 출력 단자와 상기 연산 증폭기의 반전 입력 단자가 연결된 피드백을 갖고, 상기 아날로그 버퍼는 상기 학습 네트워크의 활성화 함수로 동작하는 것을 특징으로 하는 멀티 레이어 연산 회로.

#### 청구항 8

제7항에 있어서,

상기 아날로그 버퍼의 등가 회로는 상기 연산 증폭기의 최소 출력 전압 결정하는 전원 단자를 0 V로 설정하는 것을 특징으로 하는 멀티 레이어 연산 회로.

#### 청구항 9

제8항에 있어서.

상기 아날로그 버퍼는 복수의 트랜지스터를 포함하고, 상기 피드백을 사용하는 연산 증폭기가 발진 (Oscillation)하지 않도록 상기 복수의 트랜지스터에 보상 캐패시터가 연결되는 것을 특징으로 하는 멀티 레이어 연산 회로.

#### 청구항 10

제8항에 있어서,

상기 아날로그 버퍼는 복수의 트랜지스터를 포함하고, 기 설정된 안정화 시간(Settling Time)에서 동작하도록 상기 복수의 트랜지스터의 사이즈와 바이어스 전압이 설정된 것을 특징으로 하는 멀티 레이어 연산 회로.

#### 청구항 11

제1항에 있어서,

상기 복수의 연산 영역은 (i) 제1 레이어에 해당하는 제1 연산 영역과 (ii) 제2 레이어에 해당하는 제2 연산 영역을 포함하며,

상기 제1 연산 영역과 상기 제2 연산 영역 사이에 상기 아날로그 버퍼가 연결되며,

상기 제1 연산 영역의 출력 신호가 상기 아날로그 버퍼를 거쳐 상기 제2 연산 영역으로 전송되는 것을 특징으로 하는 멀티 레이어 연산 회로.

#### 청구항 12

제11항에 있어서,

상기 제1 연산 영역의 입력단에 디지털 아날로그 컨버터(Digital to Analog Converter, DAC)가 연결되고,

상기 제2 연산 영역의 출력단에 아날로그 디지털 컨버터(Analog to Digital Converter, ADC)가 연결되는 것을 특징으로 하는 멀티 레이어 연산 회로.

#### 청구항 13

제12항에 있어서,

상기 디지털 아날로그 컨버터는 제1 아날로그 신호를 상기 제1 연산 영역으로 전송하고, 상기 제1 연산 영역은 상기 제1 아날로그 신호를 처리하여 제2 아날로그 신호를 생성하고, 상기 제1 연산 영역은 상기 제2 아날로그 신호를 상기 아날로그 버퍼로 전송하고, 상기 아날로그 버퍼는 상기 제2 아날로그 신호를 처리하여 제3 아날로 그 신호를 생성하고, 상기 아날로그 버퍼는 상기 제3 아날로그 신호를 상기 제2 연산 영역으로 전송하고, 상기 제2 연산 영역은 상기 제3 아날로그 신호를 처리하여 제4 아날로그 신호를 생성하고, 상기 제2 연산 영역은 상

기 제4 아날로그 신호를 상기 아날로그 디지털 컨버터로 전송하는 것을 특징으로 하는 멀티 레이어 연산 회로.

#### 청구항 14

제13항에 있어서,

상기 디지털 아날로그 컨버터, 상기 연산 메모리, 상기 아날로그 버퍼, 및 상기 아날로그 디지털 컨버터는 제어 부로부터 제어 신호를 수신하고,

상기 제어 신호는 상기 디지털 아날로그 컨버터의 처리 시간, 상기 제1 연산 영역의 처리 시간, 상기 아날로그 버퍼의 안정화 시간, 및 상기 제2 연산 영역의 처리 시간이 충돌하지 않도록, 상기 디지털 아날로그 컨버터, 상기 연산 메모리, 상기 아날로그 버퍼, 및 상기 아날로그 디지털 컨버터의 동작 시간을 제어하는 것을 특징으로 하는 멀티 레이어 연산 회로.

#### 청구항 15

시각 정보를 표시하는 화소를 갖는 표시부;

상기 표시부에 연결되어 상기 화소의 동작을 제어하는 제어부; 및

상기 제어부에 연결되어 이미지 데이터를 전송하는 멀티 레이어 연산 회로를 포함하며,

상기 멀티 레이어 연산 회로는,

아날로그 입력신호를 입력받고 상기 아날로그 입력신호를 처리하여 아날로그 출력신호를 출력하는 복수의 연산 영역을 포함하는 연산 메모리; 및

상기 복수의 연산 영역에 연결되어 상기 아날로그 출력신호를 하나의 연산 영역에서 다른 연산 영역으로 전송하는 아날로그 버퍼를 포함하며,

상기 연산 영역은 학습 네트워크의 레이어로 동작하며,

상기 연산 메모리 및 상기 아날로그 버퍼는 상기 제어부로부터 제어 신호를 수신하고,

상기 제어 신호는 상기 하나의 연산 영역에서 상기 아날로그 버퍼로 상기 아날로그 출력 신호가 전송되고 상기 아날로그 버퍼의 안정화 시간이 지난 후에 상기 다른 연산 영역을 동작시키도록 상기 연산 메모리 및 상기 아날 로그 버퍼의 동작 시간을 제어하며,

상기 제어부는 상기 제어 신호에 상기 동작 시간을 포함시켜 전송하거나, 상기 연산 메모리 및 상기 아날로그 버퍼는 다음 순서의 소자로 완료 신호를 전송하고 상기 다음 순서의 소자는 상기 완료 신호를 수신하여 상기 동 작 시간을 설정하여, 상기 아날로그 버퍼에서 안정화 전의 일부 신호가 일부 연산 영역의 신호와 중첩되지 않도 록 하고, 상기 아날로그 버퍼에서 안정화 전의 일부 신호가 다른 연산 영역으로 전송되지 않도록 하는 것을 특 징으로 하는 디스플레이.

#### 청구항 16

적어도 하나의 전기 신호를 발생시키는 전자 회로; 및

상기 전자 회로에 연결된 멀티 레이어 연산 회로를 포함하며,

상기 멀티 레이어 연산 회로는,

아날로그 입력신호를 입력받고 상기 아날로그 입력신호를 처리하여 아날로그 출력신호를 출력하는 복수의 연산 영역을 포함하는 연산 메모리; 및

상기 복수의 연산 영역에 연결되어 상기 아날로그 출력신호를 하나의 연산 영역에서 다른 연산 영역으로 전송하는 아날로그 버퍼를 포함하며,

상기 연산 영역은 학습 네트워크의 레이어로 동작하며,

상기 연산 메모리 및 상기 아날로그 버퍼는 제어부로부터 제어 신호를 수신하고,

상기 제어 신호는 상기 하나의 연산 영역에서 상기 아날로그 버퍼로 상기 아날로그 출력 신호가 전송되고 상기 아날로그 버퍼의 안정화 시간이 지난 후에 상기 다른 연산 영역을 동작시키도록 상기 연산 메모리 및 상기 아날 로그 버퍼의 동작 시간을 제어하며,

상기 제어부는 상기 제어 신호에 상기 동작 시간을 포함시켜 전송하거나, 상기 연산 메모리 및 상기 아날로그 버퍼는 다음 순서의 소자로 완료 신호를 전송하고 상기 다음 순서의 소자는 상기 완료 신호를 수신하여 상기 동 작 시간을 설정하여, 상기 아날로그 버퍼에서 안정화 전의 일부 신호가 일부 연산 영역의 신호와 중첩되지 않도 록 하고, 상기 아날로그 버퍼에서 안정화 전의 일부 신호가 다른 연산 영역으로 전송되지 않도록 하는 것을 특 장으로 하는 전자 장치.

#### 발명의 설명

#### 기술분야

[0001] 본 발명이 속하는 기술 분야는 메모리 내 연산(Compute-In-Memory) 회로에 관한 것이다.

#### 배경기술

- [0002] 이 부분에 기술된 내용은 단순히 본 실시예에 대한 배경 정보를 제공할 뿐 종래기술을 구성하는 것은 아니다.

- [0003] 스마트 TV, 스마트 스피커, 자율주행차, 무인 항공기, 증강 현실(Augmented Reality, AR) 장치, 및 가상 현실 (Virtual Reality, VR) 장치 등의 다양한 장치에 인공지능(Artificial Intelligence, AI) 칩이 필요하다. 온디 바이스(On-Device) AI 칩은 제품 자체에서 기계 학습(Machine Learning)과 추론을 구현할 수 있다.

- [0004] AI 칩은 전력소모 대비 성능이 중요하다. 범용 GPU는 데이터 세트를 훈련하는데 효율적이지만 전력 소모가 크고 발열이 심해서 상용 디바이스에 탑재하기 곤란하다.

- [0005] 기존의 메모리 내 연산(Compute-In-Memory) 회로는 단일 레이어의 MAC(Multiply Accumulate Circuit) 연산을 목표로 한다. 기존의 메모리 내 연산 회로를 이용하여 복수의 레이어를 연산하려면, 아날로그 디지털 컨버터 (Analog to Digital Converter, ADC), 디지털 활성화 함수 회로, 및 디지털 아날로그 컨버터(Digital to Analog Converter, DAC)를 추가로 사용하여 불필요한 데이터 변화 과정이 필요하므로, 멀티 레이어로 구성된 딥러닝 알고리즘에 적합하지 않다.

#### 선행기술문헌

#### 특허문헌

[0006] (특허문헌 0001) 미국공개특허공보 2019/0042199 (2019.02.07)

(특허문헌 0002) 미국공개특허공보 2019/0042928 (2019.02.07)

(특허문헌 0003) 미국공개특허공보 2017/0337466 (2017.11.23)

#### 비특허문헌

[0007] (비특허문헌 0001) "Conv-RAM: An Energy-Efficient SRAM with Embedded Convolution Computation for Low-Power CNN-Based Machine Learning Applications", ISSCC, pp.488-489, 2018

#### 발명의 내용

## 해결하려는 과제

- [0008] 본 발명의 실시예들은 곱셈 및 덧셈을 수행하는 복수의 연산 영역으로 구분된 연산 메모리를 포함하고, 복수의 연산 영역은 학습 네트워크의 레이어로 동작하고, 아날로그 버퍼가 복수의 연산 영역에 연결되어 데이터를 하나의 연산 영역에서 다른 연산 영역으로 전송함으로써, 학습 네트워크의 레이어 간에 데이터 전송 시간을 최소화하는 데 발명의 주된 목적이 있다.

- [0009] 본 발명의 명시되지 않은 또 다른 목적들은 하기의 상세한 설명 및 그 효과로부터 용이하게 추론할 수 있는 범

위 내에서 추가적으로 고려될 수 있다.

## 과제의 해결 수단

- [0010] 본 실시예의 일 측면에 의하면, 아날로그 입력 신호를 입력받고 상기 아날로그 입력 신호를 처리하여 아날로그 출력 신호를 출력하는 복수의 연산 영역을 포함하는 연산 메모리; 및 상기 복수의 연산 영역에 연결되어 상기 아날로그 출력 신호를 하나의 연산 영역에서 다른 연산 영역으로 전송하는 아날로그 버퍼를 포함하며, 상기 연산 영역은 학습 네트워크의 레이어로 동작하는 것을 특징으로 하는 멀티 레이어 연산 회로를 제공한다.

- [0011] 상기 연산 메모리 및 상기 아날로그 버퍼는 제어부로부터 제어 신호를 수신할 수 있다.

- [0012] 상기 제어 신호는 상기 하나의 연산 영역에서 상기 아날로그 버퍼로 상기 아날로그 출력 신호가 전송되고 상기 아날로그 버퍼의 안정화 시간이 지난 후에 상기 다른 연산 영역을 동작시키도록 상기 연산 메모리 및 상기 아날로그 버퍼의 동작 시간을 제어할 수 있다.

- [0013] 상기 연산 영역은 복수의 워드 라인, 복수의 비트 라인, 및 복수의 메모리 셀을 포함하고, 상기 메모리 셀은 상기 가중치를 저장하고, 상기 워드 라인과 상기 비트 라인은 상기 메모리 셀에 연결될 수 있다.

- [0014] 상기 연산 영역은 (i) 상기 아날로그 입력 신호와 상기 가중치를 곱하여 출력하는 곱셈 영역과 (ii) 상기 곱셈 영역의 출력을 누산하여 상기 아날로그 출력 신호를 출력하는 누산 영역을 포함할 수 있다.

- [0015] 상기 누산 영역은 상기 복수의 비트 라인이 포지티브 라인 및 네거티브 라인에 연결되어 전하 공유(Charge Sharing) 방식으로 상기 곱셈 영역의 출력을 누산할 수 있다.

- [0016] 상기 아날로그 버퍼는 상기 아날로그 버퍼에 입력된 신호가 0보다 작으면 0을 출력하고, 상기 아날로그 버퍼에 입력된 신호를 그대로 출력할 수 있다.

- [0017] 상기 아날로그 버퍼의 등가 회로는 연산 증폭기의 출력 단자와 상기 연산 증폭기의 반전 입력 단자가 연결된 피드백을 갖고, 상기 아날로그 버퍼는 상기 학습 네트워크의 활성화 함수로 동작할 수 있다.

- [0018] 상기 아날로그 버퍼의 등가 회로는 상기 연산 증폭기의 최소 출력 전압 결정하는 전원 단자를 0 V로 설정할 수 있다.

- [0019] 상기 아날로그 버퍼는 복수의 트랜지스터를 포함하고, 상기 피드백을 사용하는 연산 증폭기가 발진 (Oscillation)하지 않도록 상기 복수의 트랜지스터에 보상 캐패시터가 연결될 수 있다.

- [0020] 상기 아날로그 버퍼는 복수의 트랜지스터를 포함하고, 기 설정된 안정화 시간(Settling Time)에서 동작하도록 상기 복수의 트랜지스터의 사이즈와 바이어스 전압이 설정될 수 있다.

- [0021] 상기 복수의 연산 영역은 (i) 제1 레이어에 해당하는 제1 연산 영역과 (ii) 제2 레이어에 해당하는 제2 연산 영역을 포함할 수 있다.

- [0022] 상기 제1 연산 영역과 상기 제2 연산 영역 사이에 상기 아날로그 버퍼가 연결되며, 상기 제1 연산 영역의 출력 신호가 상기 아날로그 버퍼를 거쳐 상기 제2 연산 영역으로 전송될 수 있다.

- [0023] 상기 제1 연산 영역의 입력단에 디지털 아날로그 컨버터(Digital to Analog Converter, DAC)가 연결되고, 상기 제2 연산 영역의 출력단에 아날로그 디지털 컨버터(Analog to Digital Converter, ADC)가 연결될 수 있다.

- [0024] 상기 디지털 아날로그 컨버터는 제1 아날로그 신호를 상기 제1 연산 영역으로 전송하고, 상기 제1 연산 영역은 상기 제1 아날로그 신호를 처리하여 제2 아날로그 신호를 생성하고, 상기 제1 연산 영역은 상기 제2 아날로그 신호를 상기 아날로그 버퍼로 전송하고, 상기 아날로그 버퍼는 상기 제2 아날로그 신호를 처리하여 제3 아날로 그 신호를 생성하고, 상기 아날로그 버퍼는 상기 제3 아날로그 신호를 상기 제2 연산 영역으로 전송하고, 상기 제2 연산 영역은 상기 제3 아날로그 신호를 처리하여 제4 아날로그 신호를 생성하고, 상기 제2 연산 영역은 상기 제4 아날로그 신호를 상기 아날로그 디지털 컨버터로 전송할 수 있다.

- [0025] 상기 디지털 아날로그 컨버터, 상기 연산 메모리, 상기 아날로그 버퍼, 및 상기 아날로그 디지털 컨버터는 제어 부로부터 제어 신호를 수신할 수 있다.

- [0026] 상기 제어 신호는 상기 디지털 아날로그 컨버터의 처리 시간, 상기 제1 연산 영역의 처리 시간, 상기 아날로그 버퍼의 안정화 시간, 및 상기 제2 연산 영역의 처리 시간이 충돌하지 않도록, 상기 디지털 아날로그 컨버터, 상기 연산 메모리, 상기 아날로그 버퍼, 및 상기 아날로그 디지털 컨버터의 동작 시간을 제어할 수 있다.

- [0027] 본 실시예의 다른 측면에 의하면, 시각 정보를 표시하는 화소를 갖는 표시부; 상기 표시부에 연결되어 상기 화소의 동작을 제어하는 제어부; 및 상기 제어부에 연결되어 이미지 데이터를 전송하는 멀티 레이어 연산 회로를 포함하며, 상기 멀티 레이어 연산 회로는, 아날로그 입력신호를 입력받고 상기 아날로그 입력신호를 처리하여 아날로그 출력신호를 출력하는 복수의 연산 영역을 포함하는 연산 메모리; 및 상기 복수의 연산 영역에 연결되어 상기 아날로그 출력신호를 하나의 연산 영역에서 다른 연산 영역으로 전송하는 아날로그 버퍼를 포함하며, 상기 연산 영역은 학습 네트워크의 레이어로 동작하는 것을 특징으로 하는 디스플레이를 제공한다.

- [0028] 본 실시예의 또 다른 측면에 의하면, 적어도 하나의 전기 신호를 발생시키는 전자 회로; 및 상기 전자 회로에 연결된 멀티 레이어 연산 회로를 포함하며, 상기 멀티 레이어 연산 회로는, 아날로그 입력신호를 입력받고 상기 아날로그 입력신호를 처리하여 아날로그 출력신호를 출력하는 복수의 연산 영역을 포함하는 연산 메모리; 및 상기 복수의 연산 영역에 연결되어 상기 아날로그 출력신호를 하나의 연산 영역에서 다른 연산 영역으로 전송하는 아날로그 버퍼를 포함하며, 상기 연산 영역은 학습 네트워크의 레이어로 동작하는 것을 특징으로 하는 전자 장치를 제공한다.

#### 발명의 효과

- [0029] 이상에서 설명한 바와 같이 본 발명의 실시예들에 의하면, 곱셈 및 덧셈을 수행하는 복수의 연산 영역으로 구분된 연산 메모리를 포함하고, 복수의 연산 영역은 학습 네트워크의 레이어로 동작하고, 아날로그 버퍼가 복수의연산 영역에 연결되어 데이터를 하나의 연산 영역에서 다른 연산 영역으로 전송함으로써, 학습 네트워크의 레이어 간에 데이터 전송 시간을 최소화할 수 있는 효과가 있다.

- [0030] 여기에서 명시적으로 언급되지 않은 효과라 하더라도, 본 발명의 기술적 특징에 의해 기대되는 이하의 명세서에 서 기재된 효과 및 그 잠정적인 효과는 본 발명의 명세서에 기재된 것과 같이 취급된다.

#### 도면의 간단한 설명

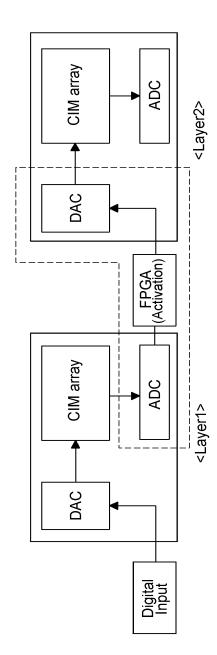

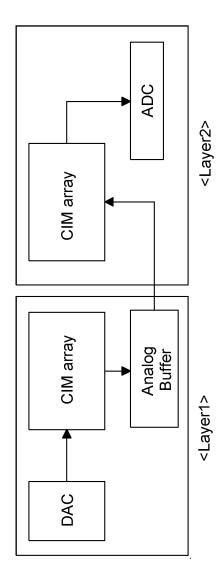

[0031] 도 1은 기존의 메모리 내 연산(Compute-In-Memory) 회로를 학습 네트워크의 레이어로 연결한 도면이다.

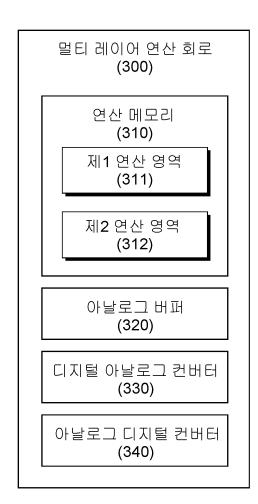

도 2 및 도 3는 본 발명의 실시예들에 따른 멀티 레이어 연산 회로를 예시한 블록도이다.

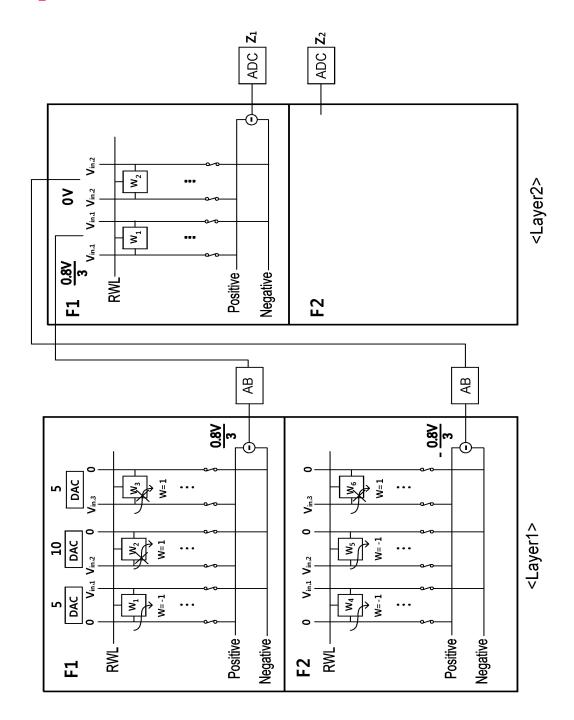

도 4 및 도 5는 본 발명의 일 실시예에 따른 멀티 레이어 연산 회로를 학습 네트워크의 레이어로 연결한 도면이다.

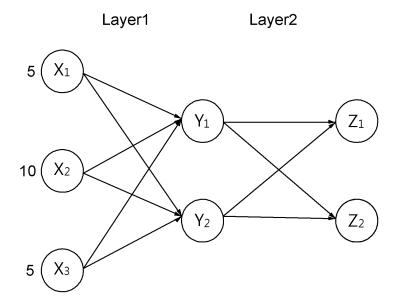

도 6은 학습 네트워크의 레이어를 예시한 도면이다.

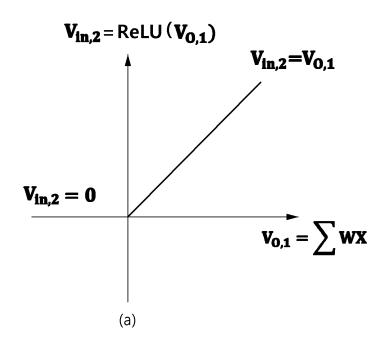

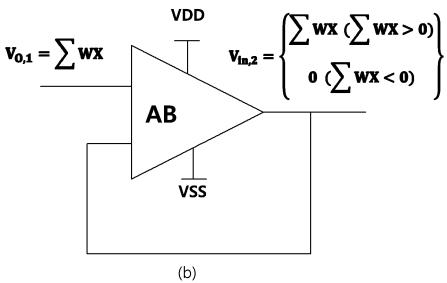

도 7은 본 발명의 일 실시예에 따른 멀티 레이어 연산 회로의 활성화 함수로 동작하는 아날로그 버퍼를 예시한 도면이다.

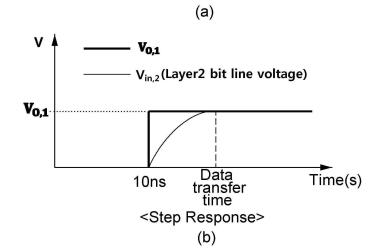

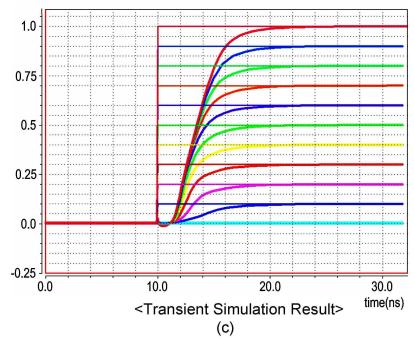

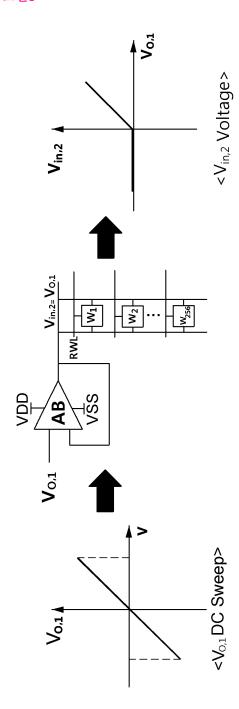

도 8 및 도 9는 본 발명의 일 실시예에 따른 멀티 레이어 연산 회로의 아날로그 버퍼의 출력을 예시한 도면이다.

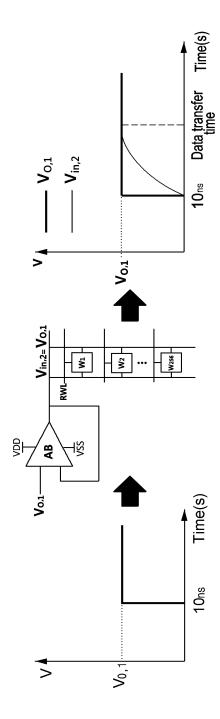

도 10 및 도 11은 본 발명의 일 실시예에 따른 멀티 레이어 연산 회로의 아날로그 버퍼의 안정화 시간을 예시한 도면이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0032] 이하, 본 발명을 설명함에 있어서 관련된 공지기능에 대하여 이 분야의 기술자에게 자명한 사항으로서 본 발명의 요지를 불필요하게 흐릴 수 있다고 판단되는 경우에는 그 상세한 설명을 생략하고, 본 발명의 일부 실시예들을 예시적인 도면을 통해 상세하게 설명한다.

- [0033] 딥러닝 알고리즘은 레이어를 적충하여 정확도를 높인다. 딥러닝 알고리즘은 이전 레이어의 결과값에 활성화 함수(Activation Function)를 취한 값이 다음 레이어의 입력 값으로 사용한다.

- [0034] 기존의 메모리 내 연산(Compute-In-Memory) 회로 아키텍처는 비효율적인 레이어 간 데이터 전송(Layer to Layer Data Transfer) 방식을 사용한다. 디지털 도메인에서 동작하는 FPGA(Field Programmable Gate Array) 또는 소 프트웨어를 이용하여 활성화 함수를 구현하고, FPGA의 입력단에 아날로그 디지털 컨버터(Analog to Digital Converter, ADC)이 연결되고, FPGA의 출력단에 디지털 아날로그 컨버터(Digital to Analog Converter, DAC)이 연결된다.

- [0035] 본 실시예에 따른 멀티 레이어 연산 회로는 효율적인 레이어 간 데이터 전송을 위해 아날로그 버퍼(Analog Buffer)를 사용하여 아날로그 도메인(Analog Domain)에서 데이터를 전송하므로, 레이어 간에 ADC 및 DAC가 불필요하다. 즉, 데이터 전송에 소모되는 지연 시간을 최소화할 수 있다.

- [0036] 본 실시예에 따른 멀티 레이어 연산 회로는 아날로그 버퍼를 사용하여 온칩 활성화 함수를 구현하고, 아날로그 버퍼의 Vss=0으로 설정하여 ReLU(Rectified Linear Unit) 함수를 구현한다. 본 실시예에 따른 멀티 레이어 연산 회로는 멀티 레이어 딥러닝 알고리즘에 적합한 메모리 내 연산(Compute-In-Memory) 회로 아키텍처를 구현할 수 있다.

- [0037] 도 1은 기존의 메모리 내 연산(Compute-In-Memory, CIM) 회로를 학습 네트워크의 레이어로 연결한 도면이다.

- [0038] 기존의 CIM 회로는 멀티 레이어로 구성되는 딥러닝 알고리즘의 특성에 맞지 않게, 단일 레이어의 MAC 연산 구현을 목표로 한다. 기존의 CIM 회로는 MAC 연산 구현만을 목표로 하므로, 딥러닝에서 사용되는 ReLU 함수와 같은 활성화 함수를 칩 내부에서 구현하는 것이 아닌, FPGA 또는 MATLAB과 같은 소프트웨어를 사용하여 구현한다.

- [0039] 기존 CIM를 이용하여 멀티 레이어 딥러닝 알고리즘을 구현하려면, 디지털 입력 데이터 -> DAC -> 아날로그 데이터 -> MAC(아날로그 도메인) -> ADC -> 디지털 데이터 -> FPGA(디지털 도메인) -> DAC -> 아날로그 데이터 -> MAC(아날로그 도메인) -> ADC -> 디지털 출력 데이터로 신호 전달 과정을 거친다.

- [0040] 멀티 레이어 구현을 위해 아날로그 형식으로 계산된 MAC 연산 결과를 ADC를 이용하여 디지털 값으로 변환하고, FPGA에서 활성화 함수를 취한 뒤에, 다시 DAC를 이용하여 아날로그 값으로 변환한다. 변환된 아날로그 값을 다음 레이어의 입력으로 넣어준다. 즉, 레이어를 통과할 때마다 ADC와 DAC가 추가로 필요하고 칩 외부에서 활성화함수를 적용하므로, 시간 측면에서 오버헤드가 발생한다. 따라서 레이서 간에 불필요한 데이터 변환 과정을 제거할 필요가 있다.

- [0041] 도 2 및 도 3는 본 발명의 실시예들에 따른 멀티 레이어 연산 회로를 예시한 블록도이다.

- [0042] 도 2에 도시한 바와 같이, 멀티 레이어 연산 회로(200)는 연산 메모리(210) 및 아날로그 버퍼(220)를 포함한다. 멀티 레이어 연산 회로(200)는 도 2에서 예시적으로 도시한 다양한 구성요소들 중에서 일부 구성요소를 생략하거나 다른 구성요소를 추가로 포함할 수 있다. 예컨대, 멀티 레이어 연산 회로(300)는 디지털 아날로그 컨버터(330), 아날로그 디지털 컨버터(340), 또는 이들의 조합을 추가로 포함할 수 있다.

- [0043] 멀티 레이어 연산 회로(200, 300)는 곱셈 및 덧셈을 수행하는 복수의 연산 영역으로 구분된 연산 메모리(210, 310)를 포함하고, 아날로그 버퍼(220, 320)가 복수의 연산 영역에 연결되어 데이터를 하나의 연산 영역에서 다른 연산 영역으로 전송한다. 복수의 연산 영역은 제1 연산 영역(311) 및 제2 연산 영역(312)을 포함할 수 있다.

- [0044] 연산 메모리(210, 310)는 아날로그 입력 신호를 입력받고 아날로그 입력 신호를 처리하여 아날로그 출력 신호를 출력하는 복수의 연산 영역을 포함한다. 연산 영역은 학습 네트워크의 레이어로 동작한다. 학습 네트워크는 딥러닝 네트워크이며, CNN(Convolutional Neural Network), RNN(Recurrent Neural Network), GAN(Generative Adversarial Network), RL(Relation Networks) 등의 다양한 네트워크가 적용될 수 있다.

- [0045] 연산 영역은 복수의 워드 라인(Word Line, WL), 복수의 비트 라인(Bit Line, BL), 및 복수의 메모리 셀을 포함한다. 워드 라인과 비트 라인은 메모리 셀에 연결되고, 메모리 셀은 가중치를 저장한다.

- [0046] 복수의 워드 라인은 리드 워드 라인(Read Word Line) 및/또는 라이트 워드 라인(Write Word Line)을 포함할 수 있다.

- [0047] 복수의 비트 라인은 비트 라인 쌍을 포함할 수 있다. 비트 라인 쌍은 비트 라인 및/또는 상보 비트 라인(Bit Line Bar)을 포함할 수 있다. 복수의 비트 라인은 입력 비트 라인 및 출력 비트 라인을 포함할 수 있다. 입력 비트 라인 및 출력 비트 라인은 물리적인 라인을 공유하되 시간적으로 구분될 수 있고, 물리적으로 구분되어 배치될 수 있다.

- [0048] 복수의 메모리 셀은 스위치와 저장부를 포함한다. 스위치는 트랜지스터일 수 있고, 저장부는 커패시터, 트랜지스터, 저항, 래치 회로, 또는 이들의 조합을 포함할 수 있다.

- [0049] 워드 라인을 통해 입력된 신호에 의해 스위치가 턴온 또는 턴오프되면, 스위치에 연결된 저장부가 데이터 리드 동작 또는 데이터 라이트 동작을 수행한다. 저장부는 비트 라인을 통해 프리 차지 또는 디스 차지 동작을 수행한다. 필요에 따라 메모리 셀은 데이터 리드 동작만을 수행할 수도 있다. 저장부는 비트 라인 및 상보 비트 라

- 인을 통해 신호를 전송할 수도 있고, 입력 비트 라인 및 출력 비트 라인을 통해 신호를 전송할 수도 있다.

- [0050] 메모리 셀에 저장된 가중치는 [-1, 1]의 값일 수 있으며, 필요에 따라 0을 포함하거나 다른 수치가 설정될 수 있다.

- [0051] 아날로그 버퍼(220, 320)는 복수의 연산 영역에 연결되어 아날로그 출력 신호를 하나의 연산 영역에서 다른 연산 영역으로 전송한다.

- [0052] 연산 메모리 및 아날로그 버퍼는 제어부(미도시)로부터 제어 신호를 수신한다. 제어부는 멀티 레이어 연산 회로 에 구현되거나 멀티 레이어 연산 회로의 외부에 구현될 수 있다.

- [0053] 제어 신호는 하나의 연산 영역에서 아날로그 버퍼로 아날로그 출력 신호가 전송되고 아날로그 버퍼의 안정화 시간이 지난 후에 다른 연산 영역을 동작시키도록 연산 메모리 및 아날로그 버퍼의 동작 시간을 제어한다.

- [0054] 제어 신호는 하나의 연산 영역의 처리 시간, 하나의 연산 영역에서 아날로그 버퍼로 아날로그 출력 신호가 전송되는 시간, 아날로그 버퍼의 동작 시간, 및 아날로그 버퍼에서 다른 연산 영역으로 아날로그 출력 신호가 전송되는 시간을 고려하여, 연산 메모리 및 아날로그 버퍼의 동작 시간을 제어할 수 있다.

- [0055] 연산 영역은 곱셈 영역과 누산 영역을 포함한다. 곱셈 영역은 아날로그 입력 신호와 가중치를 곱하여 출력하는 영역이고, 누산 영역은 곱셈 영역의 출력을 누산하여 아날로그 출력 신호를 출력하는 영역이다.

- [0056] 곱셈 영역은 계산 단계가 시간적/공간적으로 분리되어 신호를 특정 메모리 셀에서 다음 메모리 셀로 전달하여 계산할 수 있다. 해당하는 복수의 메모리 셀 전체가 동시에 계산할 수도 있다. 곱셈 영역은 셀 단위, 행 단위, 열 단위, 행렬 단위 등으로 계산할 수 있다. 곱셈 영역은 비트 라인과 메모리 셀의 연결 구조를 통해 덧셈을 반복하거나 전하 공유하여 곱셈을 수행할 수 있다. 메모리 셀은 레이어의 입력 벡터에 따른 차원 또는 값에 해당하는 개수만큼 배치될 수 있다.

- [0057] 누산 영역은 상기 복수의 비트 라인이 포지티브 라인 및 네거티브 라인에 연결되어 전하 공유(Charge Sharing) 방식으로 곱셈 영역의 출력을 누산할 수 있다.

- [0058] 멀티 레이어 연산 회로(200, 300)는 아날로그 버퍼를 이용하여 아날로그 데이터 형식을 기반으로 레이어 간에 데이터를 전송한다. 본 실시예에 따른 멀티 레이어 연산 회로는 디지털 입력 데이터 -> DAC -> 아날로그 데이터 -> MAC(아날로그 도메인) -> AB(Analog Buffer) -> MAC(아날로그 도메인) -> ADC -> 디지털 출력 데이터로 신호 전달 과정을 거친다.

- [0059] 본 실시예에 따른 멀티 레이어 연산 회로는 레이어와 레이어 간의 데이터 전송 과정을 아날로그 버퍼 단계로 변경하여 불필요한 데이터 형식 변환 과정을 생략할 수 있다. 본 실시예에 따른 멀티 레이어 연산 회로는 아날로 그 버퍼를 온칩 활성화 함수로 이용하여 멀티 레이어 딥러닝 알고리즘에 적합한 메모리 내 연산 회로 아키텍처를 구현할 수 있다.

- [0060] 도 4 및 도 5는 본 발명의 일 실시예에 따른 멀티 레이어 연산 회로를 학습 네트워크의 레이어로 연결한 도면이다. 도 6은 학습 네트워크의 레이어를 예시한 도면이다.

- [0061] 학습 네트워크는 다수의 레이어가 네트워크로 연결되며 입력 레이어, 히든 레이어, 및 출력 레이어를 포함한다. 레이어는 파라미터를 포함할 수 있고, 레이어의 파라미터는 학습 가능한 필터 집합을 포함한다. 레이어는 필터 영역에 대응할 수도 있다. 필터는 컨볼루션 필터를 적용할 수 있고, 일부 파라미터는 공유될 수 있다. 파라미터는 노드 간의 가중치 및/또는 바이어스를 포함할 수 있다.

- [0062] 학습 네트워크의 레이어가 입력 레이어, 히든 레이어, 및 출력 레이어 총 3개이면, 복수의 연산 영역은 (i) 제1 레이어에 해당하는 제1 연산 영역과 (ii) 제2 레이어에 해당하는 제2 연산 영역을 포함할 수 있다. 연산 메모리는 학습 네트워크의 레이어의 개수에 따라 제3 연산 영역, 제4 연산 영역 등을 포함할 수 있다.

- [0063] 제1 연산 영역과 제2 연산 영역 사이에 아날로그 버퍼가 연결된다. 제2 연산 영역과 제3 연산 영역 사이에 아날 로그 버퍼가 연결될 수 있고, 제3 연산 영역과 제4 연산 영역 사이에 아날로그 버퍼가 연결될 수 있다.

- [0064] 제1 연산 영역의 출력 신호가 아날로그 버퍼를 거쳐 제2 연산 영역에 입력된다. 제2 연산 영역의 출력 신호가 아날로그 버퍼를 거쳐 제3 연산 영역에 입력되고, 제3 연산 영역의 출력 신호가 아날로그 버퍼를 거쳐 제4 연산 영역에 입력될 수 있다.

- [0065] 학습 네트워크의 입력 레이어에 대응하는 연산 영역의 입력단에 디지털 아날로그 컨버터(Digital to Analog

Converter, DAC)가 연결될 수 있다. 예컨대, 학습 네트워크의 레이어가 3개이면, 제1 연산 영역의 입력단에 DAC 가 연결될 수 있다.

- [0066] 학습 네트워크의 히든 레이어가 복수이면, 마지막 히든 레이어에 대응하는 연산 영역의 출력단에 아날로그 디지털 컨버터(Analog to Digital Converter, ADC)가 연결될 수 있다. 예컨대, 학습 네트워크의 레이어가 3개이면, 제2 연산 영역의 출력단에 ADC가 연결될 수 있다.

- [0067] 디지털 아날로그 컨버터는 디지털 출력 신호를 제1 아날로그 신호로 변환할 수 있다. 디지털 아날로그 컨버터는 제1 아날로그 신호를 제1 연산 영역으로 전송할 수 있다. 제1 연산 영역은 제1 아날로그 신호를 처리하여 제2 아날로그 신호를 생성할 수 있다. 제1 연산 영역은 제2 아날로그 신호를 아날로그 버퍼로 전송할 수 있다.

- [0068] 아날로그 버퍼는 제2 아날로그 신호를 처리하여 제3 아날로그 신호를 생성할 수 있다. 아날로그 버퍼는 제3 아 날로그 신호를 제2 연산 영역으로 전송할 수 있다.

- [0069] 제2 연산 영역은 제3 아날로그 신호를 처리하여 제4 아날로그 신호를 생성할 수 있다. 제2 연산 영역은 제4 아날로그 신호를 아날로그 디지털 컨버터로 전송할 수 있다. 아날로그 디지털 컨버터는 제4 아날로그 신호를 디지털 출력 신호로 변환할 수 있다.

- [0070] 디지털 아날로그 컨버터, 연산 메모리, 아날로그 버퍼, 및 아날로그 디지털 컨버터는 제어부로부터 제어 신호를 수신할 수 있다.

- [0071] 제어 신호는 디지털 아날로그 컨버터의 처리 시간, 제1 연산 영역의 처리 시간, 아날로그 버퍼의 안정화 시간, 및 제2 연산 영역의 처리 시간이 충돌하지 않도록, 디지털 아날로그 컨버터, 연산 메모리, 아날로그 버퍼, 및 아날로그 디지털 컨버터의 동작 시간을 제어한다. 아날로그 버퍼에서 안정화 전의 일부 신호가 제1 연산 영역의 신호와 중첩되지 않도록 한다. 아날로그 버퍼에서 안정화 전의 일부 신호가 제2 연산 영역으로 전송되지 않도록 한다.

- [0072] 제어부는 디지털 아날로그 컨버터, 연산 메모리, 아날로그 버퍼, 및 아날로그 디지털 컨버터의 동작 시간마다 해당하는 소자로 제어 신호를 전송하거나 제어 신호에 동작 시간을 포함시켜 전송할 수 있다. 각 소자는 다음 순서의 소자로 완료 신호를 전송하거나 완료 신호를 수신하여 동작 타이밍을 설정할 수 있다.

- [0073] 제어 신호는 디지털 아날로그 컨버터의 처리 시간, 제1 연산 영역의 처리 시간, 아날로그 버퍼의 동작 시간, 및 제2 연산 영역의 처리 시간을 고려하여, 디지털 아날로그 컨버터, 연산 메모리, 아날로그 버퍼, 및 아날로그 디지털 컨버터의 동작 시간을 제어할 수 있다.

- [0074] 4 비트(bit) 입력 신호와 출력 신호를 예로 들어 설명한다. 4 비트는 십진수 0 내지 15를 나타낼 수 있다. 1을 0.08 V라고 가정하면, 5는 0.4 V이고 10은 0.8 V이고 15는 1.2 V에 해당한다.  $X_1$ 이 5이고  $X_2$ 이 10이고  $X_3$ 이 5이라고 가정한다.  $Y_1$ 은  $X_1$ ,  $X_2$ ,  $X_3$ , 제1 가중치, 제2 가중치, 제3 가중치가 조합된 결과이고,  $Y_2$ 는  $X_1$ ,  $X_2$ ,  $X_3$ , 제4 가중치, 제5 가중치, 제6 가중치가 조합된 결과이다.

- [0075] 제1 메모리 셀에 저장된 제1 가중치가 -1이고, 제2 메모리 셀에 저장된 제2 가중치가 1이고, 제3 메모리 셀에 저장된 제3 가중치가 1이면, 제1 레이어의 제1 MAC 연산 결과는 (0.4V\*(-1)+0.8V\*(1)+0.4V\*(1))/3 = 0.8/3 V가 된다.

- [0076] 제1 MAC 연산 결과는 아날로그 버퍼를 거쳐 제2 레이어에 입력된다.

- [0077] 제4 메모리 셀에 저장된 제4 가중치가 -1이고, 제5 메모리 셀에 저장된 제5 가중치가 -1이고, 제6 메모리 셀에 저장된 제6 가중치가 1이면, 제1 레이어의 제2 MAC 연산 결과(Y<sub>2</sub>)는 (0.4V\*(-1)+0.8V\*(-1)+0.4V\*(1))/3 = -0.8/3 V가 된다.

- [0078] 제2 MAC 연산 결과는 아날로그 버퍼를 거쳐 제2 레이어에 입력된다. 즉, 아날로그 버퍼를 통해 Y<sub>2</sub>의 결과에 ReLU 함수가 취해지고, -0.8/3 V는 0 V가 되고, 0 V가 제2 레이어에 입력된다.

- [0079] 멀티 레이어 연산 회로는 아날로그 버퍼를 ADC 및 DAC 사용없이 아날로그 도메인에서 데이터 전송을 구현하므로, 시간 지연 측면에서 유리한 장점이 있다.

- [0080] 멀티 레이어 연산 회로는 MAC 연산 후에 활성화 함수를 수행할 수 있다. 활성화 함수가 없으면 학습이 되지 않을 수 있다. 대표적인 활성화 함수는 ReLU 함수이며, 멀티 레이어 연산 회로는 아날로그 버퍼에 ReLU 함수를 적

용한다.

- [0081] 멀티 레이어 연산 회로는 아날로그 버퍼를 ADC 및 DAC 사용없이 아날로그 도메인에서 데이터 전송 및 ReLU 활성화 함수를 구현하므로, 시간 지연 및 하드웨어적인 측면에서 유리한 장점이 있다.

- [0082] 도 7은 본 발명의 일 실시예에 따른 멀티 레이어 연산 회로의 활성화 함수로 동작하는 아날로그 버퍼를 예시한 도면이다.

- [0083] ReLU 활성화 함수는 수학식 1과 같이 표현된다.

### 수학식 1

$$ReLU(\sum WX) = \begin{cases} \sum WX (\sum WX > 0) \\ 0 (\sum WX < 0) \end{cases}$$

[0084]

- [0085] 아날로그 버퍼는 아날로그 버퍼에 입력된 신호가 0보다 작으면 0을 출력하고, 아날로그 버퍼에 입력된 신호가 0 보다 크면 상기 아날로그 버퍼에 입력된 신호를 그대로 출력한다.

- [0086] 아날로그 버퍼의 등가 회로는 연산 증폭기의 출력 단자와 연산 증폭기의 반전 입력 단자가 연결된 피드백을 갖고, 아날로그 버퍼는 학습 네트워크의 활성화 함수로 동작한다.

- [0087] 아날로그 버퍼의 등가 회로는 연산 증폭기의 최소 출력 전압 결정하는 전원 단자를 0 V로 설정한다. 예컨대, 전원 단자 Vdd와 Vss 중에서 Vss를 0 V로 설정한다.

- [0088] 아날로그 버퍼로 단위 이득 버퍼(Unity Gain Buffer)를 사용하여 Vin,2가 Vo,1과 같은 값을 갖도록 한다. Vo,1=∑WX>0이면 Vin,2 = Vo,1이다. 예컨대, Vo,1=0.8 V이면 Vin,2=0.8 V이다. 아날로그 버퍼의 Vss=0으로 설정한다. Vin,2는 마이너스 전압을 출력할 수 없기 때문에 Vo,1<0 이면 0 V로 출력된다. V₀,1=-0.8이면 Vin,2=0이다. 즉 아날로그 도메인에서 ReLU 함수를 구현할 수 있다.

- [0089] 연산 메모리의 연산 영역의 출력이 전류가 아닌 전압으로 나오는 구조이며, 연산 영역의 출력이 아날로그 버퍼를 거쳐 워드 라인 전압이 아닌 비트 라인 전압으로 들어간다. 레이어의 출력 전압을 다음 레이어의 입력 전압으로 전달한다.

- [0090] 멀티 레이어 연산 회로는 아날로그 도메인에서 온칩 활성화 함수로 ReLU 함수를 구현하고, 단위 이득 버퍼를 사용한다.

- [0091] 아날로그 버퍼는 연산 메모리의 BL/BLB를 구동한다. 이때 BL/BLB에 달린 cell의 개수만큼 BL/BLB를 구동할 수 있도록 설계된다. 예를 들어 BL/BLB의 10T cell의 rows가 150개라면 cell 150개가 달린 BL/BLB를 구동할 수 있도록 설계되고, 10T cell의 rows가 256개라면 cell 256개가 달린 BL/BLB를 구동할 수 있도록 설계된다.

- [0092] 아날로그 버퍼는 복수의 트랜지스터를 포함하고, 복수의 트랜지스터에 보상 캐패시터가 연결될 수 있다. 아날로 그 버퍼는 피드백을 사용하는 단위 이득 버퍼이므로, 피드백을 사용하는 연산 증폭기가 발진(Oscillation)하지 않도록 보상 캐패시터의 사이즈가 설정될 수 있다.

- [0093] 아날로그 버퍼는 복수의 트랜지스터를 포함하고, 아날로그 버퍼가 기 설정된 안정화 시간(Settling Time)에서 동작하도록 복수의 트랜지스터의 사이즈와 바이어스 전압이 설정될 수 있다. 예컨대, 20 ns이하의 안정화 시간을 갖도록 트랜지스터의 사이즈와 바이어스 전압이 설정될 수 있다. 아날로그 버퍼의 이득이 포화되는 값을 검출하는 방식으로, 트랜지스터의 사이즈와 바이어스 전압을 산출한다.

- [0094] 도 8 및 도 9는 본 발명의 일 실시예에 따른 멀티 레이어 연산 회로의 아날로그 버퍼의 출력을 예시한 도면이다. 도 10 및 도 11은 본 발명의 일 실시예에 따른 멀티 레이어 연산 회로의 아날로그 버퍼의 안정화 시간을 예시한 도면이다.

- [0095] 성글 코너(Single Corner)에서 DC Sweep에 관한 시뮬레이션을 진행한다. 65 nm 기술이 적용되고, VDD = 2.5 V이고, VSS = 0 V이다. Vo,1는 제1 레이어의 MAC 연산 결과 전압으로 -1V ~ +1V이다. 제2 레이어 연산 메모리의

row 수는 256이다. 아날로그 버퍼를 이용하여 10T cell 256 rows를 갖는 제2 레이어의 비트 라인으로 Vo,1을 전달하는 상황을 가정한다.

- [0096] Vo,1을 -1V에서 1V까지 스윕(sweep)하여 아날로그 버퍼의 입력으로 넣는다. 도 8 및 도 9를 참조하면, 제2 레이어의 입력으로 ReLU(Vo,1)이 잘 전달되는지 확인할 수 있고, Vo,1에 ReLU 함수를 적용한 결과가 제2 레이어의 BL/BLB 전압(Vin,2)으로 잘 전달되는지 확인할 수 있다.

- [0097] 싱글 코너(Single Corner)에서 Transient에 관한 시뮬레이션을 진행한다. Vo,1에 스텝 응답(Step Response) 입력을 주고 제2 레이어의 BL/BLB 전압(Vin,2)이 Vo,1과 동일할 때까지 걸리는 시간을 측정한다. 아날로그 버퍼가 제1 레이어의 MAC 연산 출력 전압을 제2 레이어의 입력으로 전달하는 데 걸리는 시간을 의미한다. 레이어와 레이어 간에 데이터 전송 지연이 기존 구조 대비 얼마나 개선되는지 확인한다.

- [0098] 도 11을 참조하면, Vo,1이 Vin,2로 전달되는 시간은 20 ns 미만이고, 레이어와 레이어 간에 데이터 전송 지연이 20 ns 미만인 것을 확인할 수 있다.

- [0099] 본 실시예에 따른 멀티 레이어 연산 회로는 기존 구조(비특허문헌1)에서 DAC 단계에서 250ps \* 63(6b) = 15.8 ns를 소요하고 ADC 단계에서 4ns(250MHz) \* 63(6b) = 252ns를 소요하여, DAC + ADC = 267.8ns를 소요한 것보다 빠른 속도로 레이어와 레이어 간에 데이터 전송이 가능하다.

- [0100] 멀티 레이어 연산 회로는 디스플레이 또는 전자 장치 등에 적용될 수 있다.

- [0101] 디스플레이는 전기 신호에 따라 시각 정보를 표시하는 화소를 갖는 표시부, 표시부에 연결되어 화소의 동작을 제어하는 제어부, 및 제어부에 연결되어 이미지 데이터를 전송하는 멀티 레이어 연산 회로를 포함한다. 멀티 레이어 연산 회로는 앞서 설명한 실시예들이 적용될 수 있다.

- [0102] 예컨대, 멀티 레이어 연산 회로는 아날로그 입력신호를 입력받고 아날로그 입력신호를 처리하여 아날로그 출력 신호를 출력하는 복수의 연산 영역을 포함하는 연산 메모리, 및 복수의 연산 영역에 연결되어 아날로그 출력신호를 하나의 연산 영역에서 다른 연산 영역으로 전송하는 아날로그 버퍼를 포함한다. 연산 영역은 학습 네트워크의 레이어로 동작한다.

- [0103] 디스플레이는 타이밍 제어기, 데이터 드라이버, 게이트 드라이버, 및 화소 회로를 포함할 수 있다. 화소 회로는 백플레인 및 표시부를 포함할 수 있다.

- [0104] 타이밍 제어기는 수평 동기화 신호, 수직 동기화 신호, 데이터 인에이블 신호, 클럭 신호 및 이미지 데이터를 수신한다. 수직 동기화 신호는 일 프레임의 이미지가 표시되는데 요구되는 시간을 지시한다. 수평 동기화 신호는 이미지의 일 수평 라인, 즉 일 화소 라인을 표시하는데 요구되는 시간을 지시한다. 따라서, 수평 동기화 신호는 일 화소 라인에 포함되는 화소의 숫자와 동일한 숫자의 펄스들을 포함한다. 데이터 인에이블 신호는 유효한 이미지 데이터가 위치하는 구간을 지시한다.

- [0105] 타이밍 제어기는 게이트 제어 신호(Gate Control Signal)를 게이트 드라이버에 제공하고, 데이터 제어 신호 (Data Control Signal)를 데이터 드라이버에 제공한다.

- [0106] 데이터 드라이버는 타이밍 제어기로부터 디지털 이미지 데이터를 수신한다. 데이터 드라이버는 데이터 제어 신호에 응답하여 데이터 전압을 생성한다. 데이터 드라이버는 디스플레이의 데이터 라인으로 데이터 전압을 게이트 드라이버로부터의 게이트 제어 신호와 동기화하여 공급할 수 있다.

- [0107] 게이트 드라이버는 타이밍 제어기로부터의 게이트 제어 신호 입력에 응답하여 화소 회로에서 박막 트랜지스터 어레이의 온/오프를 제어한다. 게이트 드라이버는 데이터 드라이버로부터 인가되는 데이터 전압이 적합한 화소 회로로 제공되도록 한다.

- [0108] 표시부 또는 화소 회로는 AMOLED, OLED(Organic Light Emitting Diode), E-Paper, LCD(Liquid Crystal Display), LED(Light Emitting Diode), 또는 이들의 조합 등으로 구현될 수 있다. 화소 회로를 구현하는 박막 트랜지스터 어레이, 커패시터들의 구성은 디스플레이 컴포넌트의 타입뿐만 아니라 화소를 활성화하는 구동 방법에 따라 다양하게 구현될 수 있다.

- [0109] 전자 장치는 적어도 하나의 전기 신호를 발생시키는 전자 회로, 및 전자 회로에 연결된 멀티 레이어 연산 회로를 포함할 수 있다. 멀티 레이어 연산 회로는 앞서 설명한 실시예들이 적용될 수 있다.

- [0110] 예컨대, 멀티 레이어 연산 회로는 아날로그 입력신호를 입력받고 아날로그 입력신호를 처리하여 아날로그 출력

신호를 출력하는 복수의 연산 영역을 포함하는 연산 메모리, 및 복수의 연산 영역에 연결되어 아날로그 출력신호를 하나의 연산 영역에서 다른 연산 영역으로 전송하는 아날로그 버퍼를 포함한다. 연산 영역은 학습 네트워크의 레이어로 동작한다.

- [0111] 전자 장치에 포함된 구성요소들은 상호 결합되어 적어도 하나의 모듈로 구현될 수 있다. 구성요소들은 장치 내부의 소프트웨어적인 모듈 또는 하드웨어적인 모듈을 연결하는 통신 경로에 연결되어 상호 간에 유기적으로 동작한다. 이러한 구성요소들은 하나 이상의 통신 버스 또는 신호선을 이용하여 통신한다.

- [0112] 전자 장치는 하드웨어, 펌웨어, 소프트웨어 또는 이들의 조합에 의해 로직회로 내에서 구현될 수 있고, 범용 또는 특정 목적 컴퓨터를 이용하여 구현될 수도 있다. 장치는 고정배선형(Hardwired) 기기, 필드 프로그램 가능한 게이트 어레이(Field Programmable Gate Array, FPGA), 주문형 반도체(Application Specific Integrated Circuit, ASIC) 등을 이용하여 구현될 수 있다. 또한, 장치는 하나 이상의 프로세서 및 컨트롤러를 포함한 시스템은칩(System on Chip, SoC)으로 구현될 수 있다.

- [0113] 전자 장치는 하드웨어적 요소가 마련된 컴퓨팅 디바이스에 소프트웨어, 하드웨어, 또는 이들의 조합하는 형태로 탑재될 수 있다. 컴퓨팅 디바이스는 각종 기기 또는 유무선 통신망과 통신을 수행하기 위한 통신 모뎀 등의 통신장치, 프로그램을 실행하기 위한 데이터를 저장하는 메모리, 프로그램을 실행하여 연산 및 명령하기 위한 마이크로프로세서 등을 전부 또는 일부 포함한 다양한 장치를 의미할 수 있다.

- [0114] 본 실시예들은 본 실시예의 기술 사상을 설명하기 위한 것이고, 이러한 실시예에 의하여 본 실시예의 기술 사상의 범위가 한정되는 것은 아니다. 본 실시예의 보호 범위는 아래의 청구범위에 의하여 해석되어야 하며, 그와 동등한 범위 내에 있는 모든 기술 사상은 본 실시예의 권리범위에 포함되는 것으로 해석되어야 할 것이다.

#### 부호의 설명

[0115] 200, 300: 멀티 레이어 연산 회로

210, 310: 연산 메모리

311: 제1 연산 영역

312: 제2 연산 영역

220, 320: 아날로그 버퍼

330: 디지털 아날로그 컨버터

340: 아날로그 디지털 컨버터

멀티 레이어 연산 회로 (200) 연산 메모리 (210) 아날로그 버퍼 (220)

도면4

| V <sub>O,1</sub> (mV) -1000 -800 -600 -400 -200 0 | -1000 | -800 | -600 | -400 | -200 | 0   | 200                            | 200   400   600   800   1000 | 600 | 800 | 1000 |

|---------------------------------------------------|-------|------|------|------|------|-----|--------------------------------|------------------------------|-----|-----|------|

| $V_{\text{in,2}}(\text{mV})$                      | 0     | 0    | 0    | 0    | 0    | 5.6 | 0 5.6 200.3 400.1 600 800 1000 | 400.1                        | 009 | 008 | 1000 |

| V <sub>O,1</sub> (V) |      |      |      |      |      |      |      |      |      |      |

|----------------------|------|------|------|------|------|------|------|------|------|------|

| Delay<br>(ns)        | 14.8 | 12.4 | 11.7 | 11.4 | 11.3 | 11.1 | 11.3 | 11.3 | 11.6 | 11.8 |