# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**H01L 33/00** (2010.01) **H01L 21/285** (2006.01) **H01L 33/36** (2010.01)

(52) CPC특허분류

**H01L 33/0075** (2013.01) **H01L 21/28556** (2013.01)

(21) 출원번호 10-2019-0086510

(22) 출원일자 **2019년07월17일** 심사청구일자 **2019년07월17일**

(56) 선행기술조사문헌 KR1020190071277 A

> KR101785644 B1 US20150279902 A1

(45) 공고일자 2020년09월22일

(11) 등록번호 10-2158510

(24) 등록일자 2020년09월16일

(73) 특허권자

## 연세대학교 산학협력단

서울특별시 서대문구 연세로 50 (신촌동, 연세대 학교)

(72) 발명자

#### 안종현

서울시 서대문구 연세로 50(신촌동)

#### 호앙 안 투안

서울특별시 서대문구 연세로 50(신촌동)

#### 후 루힝

서울특별시 서대문구 연세로 50(신촌동)

(74) 대리인 **김연권**

전체 청구항 수 : 총 7 항

심사관: 배성주

## (54) 발명의 명칭 전이금속 화합물 트랜지스터가 집적된 발광다이오드 및 이의 제조방법

#### (57) 요 약

본 발명은 전이금속 화합물을 금속 유기 화학 증착법(MOCVD)을 통하여 발광소자에 형성시킴으로써, 발광 다이오 드 소자와 트랜지스터를 동시에 제작할 수 있는 모놀리식 집적 구조의 발광 다이오드에 관한 것으로, 전이금속 화합물을 발광 다이오드 소자에 형성시킴으로써, 발광 다이오드 소자의 특성에 영향을 주지 않으면서 트랜지스터가 집적된 발광다이오드를 제공하는 효과가 있다.

## 대 표 도 - 도1

## 100

#### (52) CPC특허분류

H01L 21/28568 (2013.01) H01L 33/36 (2013.01) H01L 2924/01042 (2013.01)

## 이 발명을 지원한 국가연구개발사업

과제고유번호2015R1A3A2066337부처명과학기술정보통신부

과제관리(전문)기관명 한국연구재단

연구사업명 리더연구자지원사업

연구과제명 변형 제어 고성능 전자 소자 연구단(1/3,2단계)(2015.12.1~2024.11.30)

기 여 율 1/1

과제수행기관명연세대학교 산학협력단연구기간2018.10.01 ~ 2019.07.31

## 명 세 서

#### 청구범위

#### 청구항 1

질화갈륨(GaN) 기반의 발광 적층 구조체;

상기 발광 적층 구조체 상부에 형성되는 제1 절연층; 및

상기 제1 절연층 상부에 형성된 전이금속 화합물 트랜지스터를 포함하고,

상기 전이금속 화합물 트랜지스터는

상기 제1 절연층 상부에 형성되는 전이금속 화합물 활성층;

상기 전이금속 화합물 활성층 상에 형성되는 드레인 전극;

상기 전이금속 화합물 활성층 상에 상기 드레인 전극과 이격되어 형성되는 소스 전극;

상기 드레인 전극과 소스 전극을 도포하면서 상기 전이금속 화합물 활성층 상부에 형성되는 제2 절연층; 및

상기 제2 절연층 상부에 형성되는 게이트 전극;

을 포함하는 것을 특징으로 하는 트랜지스터가 집적된 발광 다이오드.

#### 청구항 2

제1항에 있어서,

상기 질화갈륨(GaN) 기반의 발광 적층 구조체는,

기판;

상기 기판 상에 형성되는 제1 GaN 층;

상기 제1 GaN 층 상의 일 영역에 형성되는 제1 전극;

상기 제1 GaN 층 상의 타 영역에 형성되는 발광활성층;

상기 발광활성층 상부에 형성되는 제2 GaN 층; 및

상기 제2 GaN 층 상의 일 영역에 형성되는 제2 전극층을 포함하는 것을 특징으로 하는

트랜지스터가 집적된 발광 다이오드.

#### 청구항 3

제2항에 있어서,

상기 제1 절연층은 상기 제2 GaN 층 상의 상기 제2 전극이 형성되지 않은 영역 상에 형성되는 것을 특징으로 하는 트랜지스터가 집적된 발광 다이오드.

# 청구항 4

제1항에 있어서,

상기 전이금속 화합물 활성층은 이황화 몰리브덴(Molybdenum Disulfide, MoS<sub>2</sub>), 이셀레니드 몰리브덴(Molybdenum Diselenide, MoSe<sub>2</sub>), 이셀레니드 텅스텐(Tungsten Diselenide, WSe<sub>2</sub>), 이텔루리드 몰리브덴

(Molybdenum Ditelluride, MoTe<sub>2</sub>) 및 이셀레니드 주석(Tin Diselenide, SnSe<sub>2</sub>)로 이루어진 군에서 1 이상 선택되는 물질로 구성되는 것을 특징으로 하는 트랜지스터가 집적된 발광 다이오드.

#### 청구항 5

- (a) 기판, 제1 GaN 층, 발광활성층, 제2 GaN 층이 순차적으로 적층된 질화갈륨(GaN) 적층 구조체를 준비하는 단계;

- (b) 상기 제2 GaN 층 상에 제1 절연층을 형성하는 단계;

- (c) 상기 제1 절연층 상에 MOCVD 법을 이용하여 전이금속 화합물 활성층을 형성시킨 반도체 적층 구조체를 제공하는 단계;

- (d) 메사 에칭(mesa-etching)을 이용하여 상기 질화갈륨 적층 구조체의 제1 GaN 층 상부의 일부 영역, 상기 제2 GaN 층 상부의 일부 영역, 상기 제1 절연층 상부의 일부 영역 각각이 외부에 노출되도록 에칭하는 단계;

- (e) 상기 제1 GaN 층의 노출된 영역, 상기 제2 GaN 층의 노출된 영역 상에 각각 제1 전극과 제2 전극을 형성하고, 상기 전이금속 화합물 활성층 상에 드레인 전극과 소스 전극이 이격되도록 형성하는 단계;

- (f) 상기 제1 전극, 상기 제2 전극, 상기 드레인 전극, 상기 소스 전극, 상기 반도체 적층 구조체의 상부 영역을 도포하는 제2 절연층을 형성하는 단계; 및

- (g) 상기 제2 절연층 상에 게이트 전극을 형성하는 단계

를 포함하는 트랜지스터가 집적된 발광 다이오드의 제조방법.

#### 청구항 6

제5항에 있어서,

상기 전이금속 화합물 활성층은 이황화 몰리브덴(Molybdenum Disulfide, MoS<sub>2</sub>), 이셀레니드 몰리브덴 (Molybdenum Diselenide, MoSe<sub>2</sub>), 이셀레니드 텅스텐(Tungsten Diselenide, WSe<sub>2</sub>), 이텔루리드 몰리브덴 (Molybdenum Ditelluride, MoTe<sub>2</sub>) 및 이셀레니드 주석(Tin Diselenide, SnSe<sub>2</sub>)로 이루어진 군에서 1 이상 선택되는 물질로 구성되는 것을 특징으로 하는 트랜지스터가 집적된 발광 다이오드의 제조방법.

## 청구항 7

제5항에 있어서,

상기 전이금속 화합물 활성층의 형성은 700 ℃ 이하에서 수행하는 것을 특징으로 하는 트랜지스터가 집적된 발 광 다이오드의 제조방법.

#### 발명의 설명

#### 기술분야

[0001] 본 발명은 전이금속 화합물 기반의 트랜지스터를 발광소자와 함께 집적시킴으로써, 발광 다이오드 소자와 트랜지스터를 동시에 제작할 수 있는 모놀리식 집적 구조(monolithic intergration)의 발광 다이오드에 관한 것이다.

## 배경기술

[0003] 일반적인 마이크로 LED 디스플레이의 경우 사파이어(sapphire) 혹은 실리콘(Si) 웨이퍼(wafer) 상에서 발광 다이오드 소자를 제작하는 공정과 트랜지스터를 별도의 웨이퍼 상에서 제작한 뒤 백플레인(backplane)에 이송 (transfer)하거나 백플레인 상에서 트랜지스터를 제작하는 공정이 별도로 분리되어 있다.

- [0004] 이로 인하여, 공정비용이 증가할 뿐만 아니라 마이크로 LED 픽셀(pixel)이 작아질수록 대량 이송 시에 트랜지스 터와 발광 다이오드의 정렬(align)이 어려워지는 문제가 있다.

- [0005] 또한, 이를 개선하기 위해 트랜지스터를 발광 다이오드에 집적화시키기 위해 질화갈륨 HEMT(GaN High Electron Mobility Transistors) 소자(2Volume 35, Issue 3, March 2014, Article number 6730671, Pages 330-332)나 LTPS(Low Temperature Poly Silicon) 트랜지스터 소자를 발광 다이오드 내에 집적화시키는 연구들이 있었다.

- [0006] 그러나, 질화갈륨 HEMT 소자의 경우 별도의 복잡한 에피택셜(epitaxial) 성장을 거쳐야하므로 공정 비용의 증가로 Si를 사용할 수 없는 고 전력(high power) 반도체 등 일부에 적용되고 있으며, 디스플레이 구동을 위한 저전력(low power) 트랜지스터에 적합하지 않다.

- [0007] LTPS 트랜지스터를 발광 다이오드 소자 위에 집적하기 위해서는 별도의 ELA(Excimer Laser Annealing) 공정을 거쳐야 하므로 공정 비용이 증가하고 발광 다이오드 층의 특성이 영향받기 쉬운 단점이 존재한다.

#### 발명의 내용

### 해결하려는 과제

[0009] 본 발명은 공정비용을 감소시키고, 발광 다이오드 층의 특성에 영향을 주지 않는 트랜지스터가 집적된 발광 다이오드 및 이의 제조방법을 제공하는 것에 본 발명의 목적이 있다.

### 과제의 해결 수단

- [0011] 해결하고자 하는 과제의 달성을 위하여, 본 발명의 트랜지스터가 집적된 발광 다이오드는 질화갈륨(GaN) 기반의 발광 적층 구조체; 상기 발광 적층 구조체 상부에 형성되는 제1 절연층; 및 상기 제1 절연층 상부에 형성된 전이금속 화합물 트랜지스터를 포함한다.

- [0012] 상기 전이금속 화합물 트랜지스터는 상기 제1 절연층 상부에 형성되는 전이금속 화합물 활성층; 상기 전이금속 화합물 활성층 상에 형성되는 드레인 전극; 상기 상기 전이금속 화합물 활성층 상에 상기 드레인 전극과 이격되어 형성되는 소스 전극; 상기 드레인 전극과 소스 전극을 도포하면서 상기 전이금속 화합물 활성층 상부에 형성되는 제2 절연층; 및 상기 제2 절연층 상부에 형성되는 게이트 전극을 포함한다.

- [0014] 상기 질화갈륨(GaN) 기반의 발광 적층 구조체는, 기판; 상기 기판 상에 형성되는 제1 GaN 층; 상기 제1 GaN 층 상의 일 영역에 형성되는 제1 전극; 상기 제1 GaN 층 상의 타 영역에 형성되는 발광활성층; 상기 발광활성층 상부에 형성되는 제2 GaN 층; 상기 제2 GaN 층 상의 일 영역에 형성되는 제2 전극층을 포함할 수 있다.

- [0015] 상기 전이금속 화합물 활성층은 이황화 몰리브덴(Molybdenum Disulfide, MoS<sub>2</sub>), 이셀레니드 몰리브덴 (Molybdenum Diselenide, MoSe<sub>2</sub>), 이셀레니드 텅스텐(Tungsten Diselenide, WSe<sub>2</sub>), 이텔루리드 몰리브덴 (Molybdenum Ditelluride, MoTe<sub>2</sub>) 및 이셀레니드 주석(Tin Diselenide, SnSe<sub>2</sub>)로 이루어진 군에서 1 이상 선택되는 물질로 구성될 수 있다.

- [0016] 또한, 본 발명의 트랜지스터가 집적된 발광 다이오드의 제조방법은 (a) 기판, 제1 GaN 층, 발광활성층, 제2 GaN 층이 순차적으로 적층된 질화갈륨(GaN) 적층 구조체를 준비하는 단계; (b) 상기 제2 GaN 층 상에 제1 절연 층을 형성하는 단계; (c) 상기 제1 절연층 상에 MOCVD 법을 이용하여 전이금속 화합물 활성층을 형성시킨 반도체 적층 구조체를 제공하는 단계; (d) 메사 에칭(mesa-etching)을 이용하여 상기 질화갈륨 구조체의 제1 GaN 층 상부의 일부 영역, 상기 제2 GaN 층 상부의 일부 영역 각각이 외부에 노출되도록 에칭하는 단계; (e) 상기 제1 GaN 층의 노출된 영역, 상기 제2 GaN 층의 노출된 영역 상에 각각 제1 전 극과 제2 전극을 형성하고, 상기 전이금속 화합물 활성층 상에 드레인 전극과 소스 전극이 이격되도록 형성하는 단계; (f) 상기 제1 전극, 상기 제2 전극, 상기 드레인 전극, 상기 소스 전극, 상기 반도체 적층 구조체의 상부 영역을 도포하는 제2 절연층을 형성하는 단계; 및 (g) 상기 제2 절연층 상에 게이트 전극을 형성하는 단계를 포함한다.

- [0017] 상기 전이금속 화합물 활성층은 이황화 몰리브덴(Molybdenum Disulfide, MoS<sub>2</sub>), 이셀레니드 몰리브덴 (Molybdenum Diselenide, MoSe<sub>2</sub>), 이셀레니드 텅스텐(Tungsten Diselenide, WSe<sub>2</sub>), 이텔루리드 몰리브덴 (Molybdenum Ditelluride, MoTe<sub>2</sub>) 및 이셀레니드 주석(Tin Diselenide, SnSe<sub>2</sub>)로 이루어진 군에서 1 이상 선택

되는 물질로 구성될 수 있다.

[0018] 상기 전이금속 화합물 활성층의 형성은 700 ℃ 이하에서 수행할 수 있다.

# 발명의 효과

- [0020] 본 발명의 일 형태에 따르면, 전이금속 화합물을 발광 다이오드 소자에 형성시킴으로써, 발광 다이오드 소자의 특성에 영향을 주지 않으면서 트랜지스터가 집적된 발광다이오드를 제공하는 효과가 있다.

- [0021] 또한, 트랜지스터를 발광 다이오드 소자에 집적화함으로써, 트랜지스터와 발광 다이오드를 한번에 트랜스퍼 (tranfer)할 수 있으며, 이로 인하여 공정비용의 감소 및 정렬(align)을 용이하게 하는 효과가 있다.

- [0022] 또한, 발광 다이오드 소자 상부에 수직하게 집적화합으로써, 트랜지스터가 차지하는 면적을 감소시킴과 동시에 높은 ppi(pixels per inch)를 구현할 수 있으며, 발광 다이오드 소자와 트랜지스터 와이어 연결 시 발생하는 기 생저항(parasitic resistance) 및 기생 커패시턴스(parasitic capacitance)를 감소시킬 수 있는 효과가 있다.

- [0023] 또한, 본 발명에 따른 전이금속 화합물은 유연하고 투명한 특성을 가지고 있으므로, 발광 다이오드 층과 함께 기판으로부터 박리하여 마이크로 LED 플렉서블 디스플레이로의 응용이 가능한 효과가 있다.

#### 도면의 간단한 설명

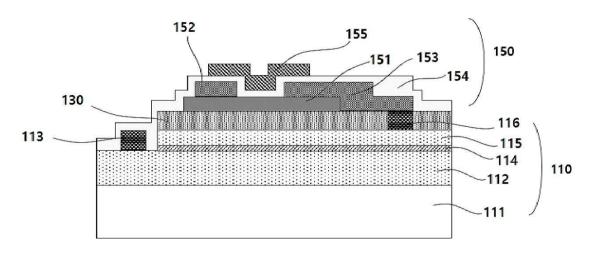

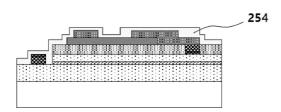

[0025] 도 1은 본 발명의 일 실시예에 따른 발광 다이오드의 구성도를 도시한 것이다.

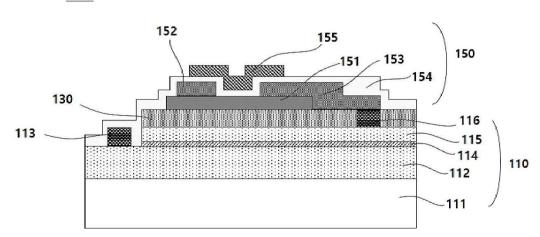

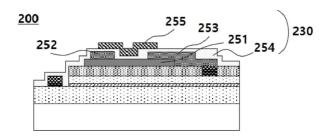

도 2는 본 발명의 일 실시예에 따른 발광 다이오드의 제조방법 순서도를 도시한 것이다.

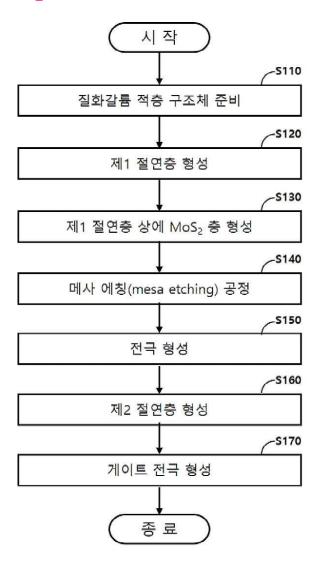

도 3a 내지 도 3g는 본 발명의 일 실시예에 따른 발광 다이오드 제조공정을 도식화한 것이다.

도 4는 본 발명의 일 실시예에 따른 발광 다이오드의 제조방법 공정도를 도시한 것이다.

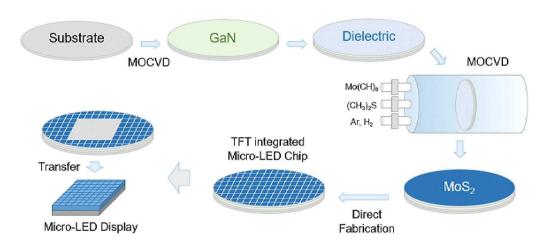

도 5는 본 발명의 일 실시예에 따른 발광 다이오드의 OM(optical microscopy) 이미지를 도시한 것이다.

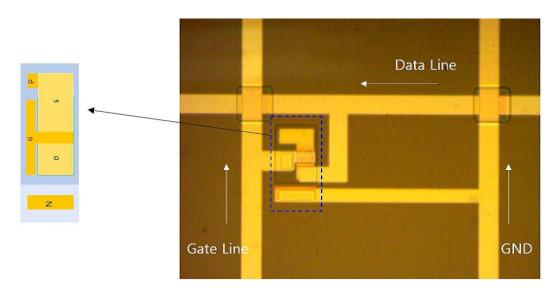

도 6은 본 발명의 일 실시예에 따른 발광 다이오드의 연속적인 구동 이미지를 도시한 것이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0026] 이하 첨부 도면들 및 첨부 도면들에 기재된 내용들을 참조하여 본 발명의 실시예를 상세하게 설명하지만, 본 발명이 실시예에 의해 제한되거나 한정되는 것은 아니다.

- [0027] 본 명세서에서 사용된 용어는 실시예들을 설명하기 위한 것이며 본 발명을 제한하고자 하는 것은 아니다. 본 명세서에서, 단수형은 문구에서 특별히 언급하지 않는 한 복수형도 포함한다. 명세서에서 사용되는 "포함한다 (comprises)" 및/또는 "포함하는(comprising)"은 언급된 구성요소, 단계, 동작 및/또는 소자는 하나 이상의 다른 구성요소, 단계, 동작 및/또는 소자의 존재 또는 추가를 배제하지 않는다.

- [0028] 본 명세서에서 사용되는 "실시예", "예", "측면", "예시" 등은 기술된 임의의 양상(aspect) 또는 설계가 다른 양상 또는 설계들보다 양호하다거나, 이점이 있는 것으로 해석되어야 하는 것은 아니다.

- [0029] 아래 설명에서 사용되는 용어는, 연관되는 기술 분야에서 일반적이고 보편적인 것으로 선택되었으나, 기술의 발달 및/또는 변화, 관례, 기술자의 선호 등에 따라 다른 용어가 있을 수 있다. 따라서, 아래 설명에서 사용되는 용어는 기술적 사상을 한정하는 것으로 이해되어서는 안 되며, 실시예들을 설명하기 위한 예시적 용어로 이해되어야 한다.

- [0030] 또한, 특정한 경우는 출원인이 임의로 선정한 용어도 있으며, 이 경우 해당되는 설명 부분에서 상세한 그 의미를 기재할 것이다. 따라서 아래 설명에서 사용되는 용어는 단순한 용어의 명칭이 아닌 그 용어가 가지는 의미와 명세서 전반에 걸친 내용을 토대로 이해되어야 한다.

- [0031] 한편, 제1, 제2 등의 용어는 다양한 구성 요소들을 설명하는데 사용될 수 있지만, 구성 요소들은 용어들에 의하여 한정되지 않는다. 용어들은 하나의 구성 요소를 다른 구성 요소로부터 구별하는 목적으로만 사용된다.

- [0032] 또한, 막, 층, 영역, 구성 요청 등의 부분이 다른 부분 "위에" 또는 "상에" 있다고 할 때, 다른 부분의 바로 위에 있는 경우뿐 만 아니라, 그 중간에 다른 막, 층, 영역, 구성 요소 등이 개재되어 있는 경우도 포함한다.

- [0033] 다른 정의가 없다면, 본 명세서에서 사용되는 모든 용어(기술 및 과학적 용어를 포함)는 본 발명이 속하는 기술

분야에서 통상의 지식을 가진 자에게 공통적으로 이해될 수 있는 의미로 사용될 수 있을 것이다. 또 일반적으로 사용되는 사전에 정의되어 있는 용어들은 명백하게 특별히 정의되어 있지 않는 한 이상적으로 또는 과도하게 해석되지 않는다.

- [0034] 한편, 본 발명을 설명함에 있어서, 관련된 공지 기능 또는 구성에 대한 구체적인 설명이 본 발명의 요지를 불필요하게 호릴 수 있다고 판단되는 경우에는, 그 상세한 설명을 생략할 것이다. 그리고, 본 명세서에서 사용되는용어(terminology)들은 본 발명의 실시예를 적절히 표현하기 위해 사용된 용어들로서, 이는 사용자, 운용자의의도 또는 본 발명이 속하는 분야의 관례 등에 따라 달라질 수 있다. 따라서, 본 용어들에 대한 정의는 본 명세서 전반에 걸친 내용을 토대로 내려져야 할 것이다.

- [0036] 이하, 본 발명의 실시예를 첨부된 도면을 참조하여 상세하게 설명한다.

- [0037] 도 1을 참조하면, 본 발명의 트랜지스터가 집적된 발광 다이오드(100)는 질화갈륨(GaN) 기반 발광 적층 구조체 (110), 질화갈륨(GaN) 기반 발광 적층 구조체(110) 상부에 형성되는 제1 절연층(130) 및 제1 절연층(130) 상부에 형성되는 전이금속 화합물 트랜지스터(150)를 포함한다.

- [0039] 질화갈륨(GaN) 기반의 발광 적층 구조체(110)는, 기판(111), 기판(111) 상에 형성되는 제1 GaN 층(112), 제1 GaN 층(112) 상의 일 영역에 형성되는 제1 전극(113), 제1 GaN 층(112) 상의 타 영역에 형성되는 발광활성층 (114), 발광활성층(114) 상부에 형성되는 제2 GaN 층(115) 및 제2 GaN 층(115) 상의 일 영역에 형성되는 제2 전극(116)을 포함한다.

- [0041] 기판(111)은 발광 다이오드 분야에서 통상적으로 사용되는 재질의 기판을 사용할 수 있고, 사파이어(sapphire), 질화갈륨(GaN; gallium nitride), 갈륨 비소(GaAs; gallium arsenide), 스피넬(spinel), 실리콘(Si; silicon), 인화 인듐(InP; indium phosphide) 및 실리콘 카바이드(SiC; silicon carbide) 중 적어도 어느 하나일 수 있으며, 바람직하게는 실리콘(Si) 혹은 사파이어(Al<sub>2</sub>O<sub>3</sub>) 기판일 수 있다.

- [0043] 제1 GaN 충(112)는 n형 GaN 반도체 충일 수 있으며, 제1 전극(113)은 n형 전극일 수 있다. 제1 전극(113)은 제 1 GaN 충(112) 상에 오믹 콘택(ohmit contact)할 수 있다. 제1 전극(113)은 각각 Cr(5 nm)/Au(400 nm)전극일 수 있다

- [0044] 질화갈륨은 우수한 물리적, 화학적 특성으로 인해 다양한 광소자의 핵심 소재로 사용되고 있다. 질화갈륨은 사파이어, 실리콘 카바이드 또는 실리콘 같은 성장 기판 상에 성장시켜 사용된다.

- [0045] 또한, n형 반도체층으로 사용되는 질화갈륨의 각 갈륨 원자는 네 개의 질소 원자들에 사면체적으로 배위되고, 방향에 따라 Ga-극성 n-type 반도체층 특성 및 N-극성 n-type 반도체층 특성을 가질 수 있다.

- [0046] 질화갈륨을 성장시키기 위해서는 결정 품질에 유의하여야 한다. 특히, 결정 품질은 에피택셜 측면 오버그로스 (ELOG; epitaxial lateral overgrowth)를 활용함으로써 개선될 수도 있다.

- [0047] 에피택셜 측면 오버그로스(ELOG; epitaxial lateral overgrowth)는 기판으로부터 수직 방향으로 질화갈륨이 성 장될뿐만 아니라 마스킹 패턴 위로도 측면 방향으로 성장될 수 있다.

- [0048] 실시예에 따라서는 제1 GaN 층은 질화갈륨(GaN)이 아닌 알루미늄 갈륨 질화물(AlGaN; aluminium gallium nitride), 인듐 갈륨 질화물(InGaN; indium gallium nitride) 및 알루미늄 인듐 갈륨 질화물(AlInGaN; aluminum indium gallium nitride) 중 적어도 어느 하나를 포함하는 층일 수 있다.

- [0049] 기판(111)과 제1 GaN 층(112)의 사이에 버퍼층(buffer layer)이 형성될 수 있으며, 상기 버퍼층은 기판(111)과 제1 GaN 층(112) 사이의 격자부정합을 완화할 수 있으며, 상기 버퍼층은 상면에 반도체 층은 제1 GaN 층(112)이 용이하게 성장될 수 있도록 할 수 있다. 상기 버퍼층은 기판(111)과 제1 GaN 층(112) 사이의 격자상수 차이를 완화시켜 줄 수 있는 물질로 이루어질 수 있다.

- [0050] 상기 버퍼층은 산화아연(ZnO), 질화알루미늄(AlN), 질화인듐(InN), 질화탄탈륨(TaN), 질화티타늄(TiN), 질화하 프늄(HfN), 티탄하프늄(HfTi), 질화갈륨(GaN), 알루미늄 질화갈륨(AlGaN), 알루미늄 질화인듐(AlInN), 인듐알루미늄 질화갈륨(InAlGaN) 중의 어느 하나 이상의 물질로 형성될 수 있으며, 기판(111)과 제1 GaN 층(112) 사이의 격자상수 차이를 완화시켜 줄 수 있는 물질이라면 이에 한정되지 않는다.

- [0052] 발광활성층(114)은 에너지 밴드 갭이 작은 물질을 사용하는 양자우물(quantum well) 및 에너지 밴드 갭이 큰 물질을 사용하는 양자 배리어(quantum barrier)이 적어도 1회 교대로 적층된 구조를 가질 수 있다. 양자우물은 단

- 일 양자우물(single quantum well) 구조 또는 다중 양자우물(MQW; multi-quantum well) 구조를 가질 수 있다.

- [0053] 또한, 상기 양자우물로는 인듐 갈륨 질화물(InGaN)이 사용될 수 있고, 양자 배리어로는 질화갈륨(GaN)이 사용될 수 있으나, 이에 한정되는 것은 아니다.

- [0054] 실시예에 따라서는 발광활성층(114)은 인듐 갈륨 질화물(InGaN; indium gallium nitride), 알루미늄 갈륨 질화물(AlGaN; aluminium gallium nitride), 질화갈륨(GaN; gallium nitride) 및 알루미늄 인듐 갈륨 질화물(AlInGaN; aluminum indium gallium nitride) 중 적어도 어느 하나를 포함할 수 있다.

- [0056] 제2 GaN 층(115)는 p형 GaN 반도체 층일 수 있으며, 제2 전극(116)은 p형 전극일 수 있다. 제2 전극(116)은 제 2 GaN 층(115) 상에 오믹 콘택(ohmit contact)할 수 있다. 제2 전극(116) 각각 Cr(5 nm)/Au(40 nm)전극일 수 있다

- [0057] 실시예에 따라서는 제2 GaN 층(115)은 질화갈륨(GaN)이 아닌 알루미늄 갈륨 질화물(AlGaN; aluminium gallium nitride), 인듐 갈륨 질화물(InGaN; indium gallium nitride) 및 알루미늄 인듐 갈륨 질화물(AlInGaN; aluminum indium gallium nitride) 중 적어도 어느 하나를 포함하는 층일 수 있다.

- [0059] 제1 절연층(130)은 제2 GaN 층(115) 상에서 제2 전극(116)이 형성되지 않는 영역에 형성될 수 있으며, 제1 절연 층(130)의 두께는 제2 전극(116)의 두께와 동일할 수 있다.

- [0060] 실시예에 따라 제1 절연충(130)은 실리콘 산화막(SiO<sub>2</sub>), 실리콘 질화막(SiNx), 알루미늄 산화막(Al<sub>2</sub>O<sub>3</sub>), 하프늄 산화막(HfO<sub>2</sub>), 마그네슘 산화막(MgO), 티타늄 산화막(TiO<sub>2</sub>), 탄탈륨 산화막(Ta<sub>2</sub>O<sub>5</sub>), 갈륨 산화막(Ga<sub>2</sub>O<sub>3</sub>) 및 지르 코늄 산화막(ZrO<sub>2</sub>)으로 이루어진 군에서 1 이상 선택되는 것일 수 있다.

- [0062] 전이금속 화합물 트랜지스터(150)는 제1 절연충(130) 상부에 형성되는 활성충(151), 전이금속 화합물 활성충 (151) 상에 형성되는 드레인 전극(152), 활성충(151) 상에 드레인 전극(152)과 이격되어 형성되는 소스 전극 (153), 드레인 전극(152)과 소스 전극(153)을 도포하면서 전이금속 화합물 활성충(151) 상부에 형성되는 제2 절연충(154) 및 제2 절연충(154) 상부에 형성되는 게이트 전극(155)을 포함한다.

- [0063] 전이금속 화합물 활성층(151)은 전이금속 칼코겐 화합물(Transition Metal Dichalcogenides)로 형성될 수 있고, 전이금속 칼코겐 화합물은 단층 또는 다층일 수 있다.

- [0064] 이차원 물질은 일차원 물질과 비교했을 때 복잡한 구조를 제조하기가 상대적으로 쉬워 차세대 나노전자소자의 물질로 이용하기에 적합하다. 이러한 2차원 물질 중 2차원 전이금속 칼코겐화합물(2D Transition Metal Dichalcogenides)은 이황화 몰리브덴(Molybdenum Disulfide, MoS<sub>2</sub>), 이셀레니드 몰리브덴(Molybdenum Diselenide, MoSe<sub>2</sub>), 이셀레니드 팅스텐(Tungsten Diselenide, WSe<sub>2</sub>), 이텔루리드 몰리브덴(Molybdenum Ditelluride, MoTe<sub>2</sub>), 및 이셀레니드 주석(Tin Diselenide, SnSe<sub>2</sub>) 중 적어도 어느 하나일 수 있다.

- [0066] 드레인 전극(152)과 소스 전극(153)은 활성층(151) 상에 오믹 콘택(ohmit contact)할 수 있으며, 소스 전극 (153)은 제2 전극(116)과 전기적으로 접속될 수 있다.

- [0067] 드레인 전극(152) 및 소스 전극(153)은 금속 및 투명 전도성 물질 중 어느 하나의 물질로 이루어질 수 있고, 상기 금속은 Au, Ti, Al, 및 Pd 중 어느 하나의 물질일 수 있으나, 이에 한정되지 않고, 본 발명이 속한 기술분야에서 사용가능한 금속 물질이면 바람직하다. 또한, 상기 투명 전도성 물질은 비정질 산화물, 결정질 산화물, 그래핀(grapheme) 및 고분자 유기물 중 적어도 하나 이상의 물질일 수 있다. 실시예에 따라서는 소스 전극(153) 및 드레인 전극(152)은 투명 전도성 물질로 이루어질 수 있고, 상기 투명 전도성 물질은 IZO(indium zinc oxide), ITO(indium thin oxide), 그래핀(graphene)일 수 있으며, 또한, 드레인 전극(152) 및 소스 전극(153)은 Cr(5 nm)/Au(40 nm)으로 형성될 수 있다.

- [0068] 드레인 전극(152) 및 소스 전극(153)은 전이금속 화합물 활성충(151)에 형성되어, 트렌치(trench) 형 구조를 형성할 수 있다.

- [0070] 제2 절연층(154)은 게이트 절연막으로서, 제1 전극(113) 및 제1 전극(113)이 형성된 제1 GaN 층(112) 영역, 제2 전극(116), 전이금속 화합물 활성층(151)이 형성되지 않은 제1 절연층(130)의 영역을 모두 도포하도록 형성될 수 있으며, 후술할 게이트 전극이 안착될 수 있는 게이트 전극 영역을 제공할 수 있다. 또한, 실시예에 따라 제 2 절연층(154)의 두께는 30 nm일 수 있다. 또한, 드레인 전극(152)과 소스 전극(153) 사이의 전이금속 화합물

활성층(151)의 상기 트렌치(trench) 형 구조에 대응되도록 형성될 수 있다.

- [0071] 제2 절연층(154)은 실리콘 산화막(SiO<sub>2</sub>), 실리콘 질화막(SiNx), 알루미늄 산화막(Al<sub>2</sub>O<sub>3</sub>), 하프늄 산화막(HfO<sub>2</sub>), 마그네슘 산화막(MgO), 티타늄 산화막(TiO<sub>2</sub>), 탄탈륨 산화막(Ta<sub>2</sub>O<sub>5</sub>), 갈륨 산화막(Ga<sub>2</sub>O<sub>3</sub>) 및 지르코늄 산화막(ZrO<sub>2</sub>)으로 이루어진 군에서 1 이상 선택되는 것일 수 있다.

- [0072] 게이트 전극(155)은 드레인 전극(152)과 소스 전극(153)의 이격된 사이의 전이금속 화합물 활성층(151)과 접하고, 제2 절연층(154)을 전이금속 화합물 활성층(151)과 사이에 두고 형성되며, 보다 상세하게는 상기 트렌치 형구조에 안착되도록 형성될 수 있다. 게이트 전극(155)을 형성함으로써, 질화기반 발광 적층 구조체(110) 상에 형성된 전이금속 화합물 트랜지스터(150)를 제조한다.

- [0073] 게이트 전극(155)은 Cr(5 nm)/Au(40 nm)으로 형성될 수 있다.

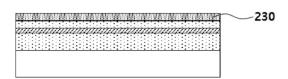

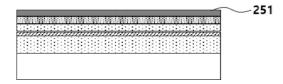

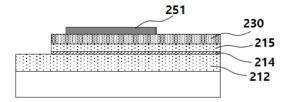

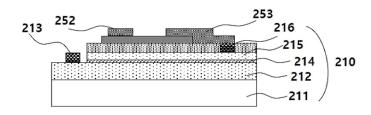

- [0075] 도 2, 도 3a 내지 도 3g를 참조하면, 본 발명의 트랜지스터가 집적된 발광 다이오드(200)의 제조방법은 기관 (211), 제1 GaN 층(212), 발광활성층(214), 제2 GaN 층(215)이 순차적으로 적층된 질화갈륨 구조체를 준비하는 단계(S110), 제2 GaN 층(215) 상에 제1 절연층(230)을 형성하는 단계(S120), 제1 절연층(230) 상에 MOCVD(metal-organic chemical vapor deposition) 법을 이용하여 전이금속 화합물 활성층(251)을 형성시킨 반도체 적층 구조체를 제공하는 단계(S130), 메사 에칭(mesa-etching)을 이용하여 상기 질화갈륨 구조체의 제1 GaN 층(212) 상부의 일부 영역, 제2 GaN 층(215) 상부의 일부 영역, 제1 절연층(230) 상부의 일부 영역 각각이 외부에 노출되도록 에칭하는 단계(S140), 제1 GaN 층(212)의 노출된 영역, 제2 GaN 층(215)의 노출된 영역 상에 각각 제1 전극(213)과 제2 전극(216)을 형성하고, 전이금속 화합물 활성층(251) 상에 드레인 전극(252)과 소스 전극(253)을 이격되도록 형성하는 단계(S150), 제1 전극(213), 제2 전극(216), 드레인 전극(252), 소스 전극(252), 상기 반도체 적층 구조체의 상부 영역을 도포하는 제2 절연층(254)을 형성하는 단계(S160), 및 제2 절연층(254) 상에 게이트 전극(255)을 형성하는 단계(S170)를 포함한다.

- [0076] 도 3a를 참조하면, 단계 S110는 기판(211) 상에 제1 GaN 층(212)을 증착하는 단계(S111), 제1 GaN 층(212) 상에 발광활성층(214)을 증착하는 단계(S113), 발광활성층(214) 상에 제2 GaN 층(215)을 증착하는 단계(S115)를 포함할 수 있다.

- [0077] 단계 S110는, MOCVD 법에 의하여 수행될 수 있으며, 1000 ℃ 이상에서 수행되는 것이 바람직하다.

- [0078] 기판(211)은 발광 다이오드 분야에서 통상적으로 사용되는 재질의 기판을 사용할 수 있고, 사파이어(sapphire), 질화갈륨(GaN; gallium nitride), 갈륨 비소(GaAs; gallium arsenide), 스피넬(spinel), 실리콘(Si; silicon), 인화 인듐(InP; indium phosphide) 및 실리콘 카바이드(SiC; silicon carbide) 중 적어도 어느 하나일 수 있으며, 바람직하게는 실리콘(Si) 혹은 사파이어(Al<sub>2</sub>O<sub>3</sub>) 기판일 수 있다.

- [0079] 제1 GaN 층(212)은 n형 반도체 층일 수 있으며, 질화 갈륨은 우수한 물리적, 화학적 특성으로 인해 다양한 광소자의 핵심 소재로 사용되고 있다. 질화 갈륨은 사파이어, 실리콘 카바이드 또는 실리콘 같은 성장 기판 상에 이종 에피텍시얼에 의해 성장시켜 사용된다.

- [0080] 또한, n형 반도체 층으로 사용되는 질화 갈륨의 각 갈륨 원자는 네 개의 질소 원자들에 사면체적으로 배위되고, 방향에 따라 Ga-극성 n-type 반도체층 특성 및 N-극성 n-type 반도체층 특성을 가질 수 있다.

- [0081] 질화 갈륨을 성장시키기 위해서는 결정 품질에 유의하여야 한다. 특히, 결정 품질은 에피택셜 측면 오버그로스 (ELOG; epitaxial lateral overgrowth)를 활용함으로써 개선될 수도 있다.

- [0082] 에피택셜 측면 오버그로스(ELOG; epitaxial lateral overgrowth)는 기판으로부터 수직 방향으로 질화 갈륨이 성 장될뿐만 아니라 마스킹 패턴 위로도 측면 방향으로 성장될 수 있다.

- [0083] 실시예에 따라서는 제1 GaN 층은 질화갈륨(GaN)이 아닌 알루미늄 갈륨 질화물(AlGaN; aluminium gallium nitride), 인듐 갈륨 질화물(InGaN; indium gallium nitride) 및 알루미늄 인듐 갈륨 질화물(AlInGaN; aluminum indium gallium nitride) 중 적어도 어느 하나를 포함하는 층일 수 있다.

- [0085] 발광활성층(214)은 에너지 밴드 갭이 작은 물질을 사용하는 양자우물(quantum well) 및 에너지 밴드 갭이 큰 물질을 사용하는 양자 배리어(quantum barrier)가 적어도 1회 교대로 적충된 구조를 가질 수 있다. 양자우물은 단일 양자우물(single quantum well) 구조 또는 다중 양자우물(MQW; multi-quantum well) 구조를 가질 수 있다.

- [0086] 또한, 상기 양자우물로는 인듐 갈륨 질화물(InGaN)이 사용될 수 있고, 양자 배리어로는 질화 갈륨(GaN)이 사용

될 수 있으나, 이에 한정되는 것은 아니다.

- [0087] 실시예에 따라서는 발광활성층(214)은 인듐 갈륨 질화물(InGaN; indium gallium nitride), 알루미늄 갈륨 질화물(AlGaN; aluminium gallium nitride), 질화 갈륨(GaN; gallium nitride) 및 알루미늄 인듐 갈륨 질화물(AlInGaN; aluminum indium gallium nitride) 중 적어도 어느 하나를 포함할 수 있다.

- [0088] 제2 GaN 충(215)는 p형 GaN 반도체 충일 수 있으며, 실시예에 따라서는 제2 GaN 충은 질화갈륨(GaN)이 아닌 알루미늄 갈륨 질화물(AlGaN; aluminium gallium nitride), 인듐 갈륨 질화물(InGaN; indium gallium nitride) 및 알루미늄 인듐 갈륨 질화물(AlInGaN; aluminum indium gallium nitride) 중 적어도 어느 하나를 포함하는 충일 수 있다.

- [0090] 도 3b를 참조하면, 단계 S120에서, 제1 절연층(230)은 실리콘 산화막(SiO<sub>2</sub>), 실리콘 질화막(SiNx), 알루미늄 산화막(Al<sub>2</sub>O<sub>3</sub>), 하프늄 산화막(HfO<sub>2</sub>), 마그네슘 산화막(MgO), 티타늄 산화막(TiO<sub>2</sub>), 탄탈륨 산화막(Ta<sub>2</sub>O<sub>5</sub>), 갈륨 산화막(Ga<sub>2</sub>O<sub>3</sub>) 및 지르코늄 산화막(ZrO<sub>2</sub>)으로 이루어진 군에서 1 이상 선택될 수 있다.

- [0091] 도 3c를 참조하면, 단계 S130에서, 전이금속 화합물 활성층(251)의 형성은 질화갈륨 기반의 구조체에 영향을 주지 않는 조건에서 수행하는 것이 바람직하며, 전이금속 화합물 활성층(251)의 형성은 700 ℃이하에서 수행할 수 있으며, 바람직하게는 600 ℃이하에서 수행하는 것일 수 있다. MOCVD를 이용하여 전이금속 화합물을 원자층 두께 형성할 수 있으며, 상기 700 ℃는 질화갈륨 기반의 구조체에 영향을 주지 않으면서 수 nm 이내의 얇은 두께를 가지도록 활성층을 형성할 수 있다.

- [0092] 전이금속 화합물 활성층(251)은 전이금속 칼코겐 화합물(Transition Metal Dichalcogenides)로 형성될 수 있고, 전이금속 칼코겐 화합물은 단층 또는 다층일 수 있다.

- [0093] 이차원 물질은 일차원 물질과 비교했을 때 복잡한 구조를 제조하기가 상대적으로 쉬어 차세대 나노전자소자의 물질로 이용하기에 적합하다. 이러한 2차원 물질 중 2차원 전이금속 칼코겐화합물(2D Transition Metal Dichalcogenides)은 이황화 몰리브덴(Molybdenum Disulfide, MoS<sub>2</sub>), 이셀레니드 몰리브덴(Molybdenum Diselenide, MoSe<sub>2</sub>), 이셀레니드 팅스텐(Tungsten Diselenide, WSe<sub>2</sub>), 이텔루리드 몰리브덴(Molybdenum Ditelluride, MoTe<sub>2</sub>), 및 이셀레니드 주석(Tin Diselenide, SnSe<sub>2</sub>) 중 적어도 어느 하나일 수 있다.

- [0095] 도 3d를 참조하면, 단계 S140에서, 메사 에칭을 통하여 전이금속 화합물 활성층(251), 제1 절연층(230), 제2 GaN 층(215), 발광활성층(214)을 식각하여 제1 GaN 층(212)의 일부 영역이 노출시킨다.

- [0096] 이후, 전이금속 화합물 활성층(251)과 제1 절연층(230)을 식각하여 제2 GaN 층(215)의 일부 영역을 노출시킨다.

- [0097] 메사 에칭의 순서는 변경될 수 있으며, 메사 에칭을 통하여 노출된 각각의 영역에 후출할 제1 전극, 제2 전극을 형성시킬 수 있으며, 상기 제1 전극 및 상기 제2 전극이 형성된 이외의 노출된 영역을 후술할 제2 절연층에 의 해 도포될 수 있다.

- [0099] 도 3e를 참조하면, 단계 S150에서, 제1 전극(213)은 n형 전극, 제2 전극(216)은 p형 전극일 수 있으며, 제1 전극(213)과 제2 전극(216)은 각각 Cr(5 nm)/Au(40 nm)전극일 수 있다.

- [0100] 제1 전극(213)과 제2 전극(216)을 형성함으로써, 질화갈륨(GaN) 기반 발광 적층 구조체(210)가 형성되며 발광 다이오드 소자로서 수행한다.

- [0101] 단계 S150에서. 드레인 전극(252) 및 소스 전극(253)은 금속 및 투명 전도성 물질 중 어느 하나의 물질로 이루어질 수 있고, 상기 금속은 Au, Ti, Al, 및 Pd 중 어느 하나의 물질일 수 있으나, 이에 한정되지 않고, 본 발명이 속한 기술분야에서 사용가능한 금속 물질이면 바람직하다. 또한, 상기 투명 전도성 물질은 비정질 산화물, 결정질 산화물, 그래핀(grapheme) 및 고분자 유기물 중 적어도 하나 이상의 물질일 수 있다. 실시예에 따라서는 드레인 전극(252) 및 소스 전극(253)은 투명 전도성 물질로 이루어질 수 있고, 상기 투명 전도성 물질은 IZO(indium zinc oxide), ITO(indium thin oxide), 그래핀(graphene)일 수 있으며, 또한, 바람직하게, 드레인 전극(252) 및 소스 전극(253)은 Cr(5 nm)/Au(40 nm)으로 형성될 수 있다.

- [0102] 드레인 전극(252) 및 소스 전극(253)은 전이금속 화합물 활성층(251)에 형성되어, 트렌치(trench) 형 구조를 형성할 수 있다.

- [0103] 제1 전극(213), 제2 전극(214), 드레인 전극(252) 및 소스 전극(253)는 증착방식(Evaporation)에 의하여 각각

형성될 수 있으며, 열 증착(Thermal Evaporation) 또는 전자빔 증착(E-beam Evaporation)에 의하여 형성할 수 있다.

- [0105] 도 3f를 참조하면, 단계 S160에서, 제2 절연층(254)은 (d) 단계(S140)에서, 메사 에칭으로 인하여, 제1 GaN 층 (212)의 노출된 영역, 제1 절연층(230)의 노출된 영역을 모두 도포하도록 형성되는 것이 바람직하며, 드레인 전 극(252)과 소스 전극(253) 사이의 전이금속 화합물 활성층(251)에는 단계 S160에서의 상기 트렌치(trench) 형 구조에 대응되도록 형성될 수 있으며, 제2 절연층(254)은 게이트 절연막으로서, 후술할 게이트 전극이 안착될 수 있는 게이트 전극 영역을 제공할 수 있다.

- [0106] 단계 S160에서, 제2 절연층(254)은 실리콘 산화막(SiO<sub>2</sub>), 실리콘 질화막(SiNx), 알루미늄 산화막(Al<sub>2</sub>O<sub>3</sub>), 하프늄 산화막(HfO<sub>2</sub>), 마그네슘 산화막(MgO), 티타늄 산화막(TiO<sub>2</sub>), 탄탈륨 산화막(Ta<sub>2</sub>O<sub>5</sub>), 갈륨 산화막(Ga<sub>2</sub>O<sub>3</sub>) 및 지르 코늄 산화막(ZrO<sub>2</sub>)으로 이루어진 군에서 1 이상 선택될 수 있으며, 제2 절연층(254)의 두께는 30 nm로 형성될 수 있다.

- [0108] 도 3g를 참조하면, 단계 S170에서, 게이트 전극(255)은 드레인 전극(252)과 소스 전극(253)의 이격된 사이의 전이금속 화합물 활성층(251)과 접하고, 제2 절연층(254)을 전이금속 화합물 활성층(251)과 사이에 두고 형성되며, 보다 상세하게는 상기 트렌치 형 구조에 안착되도록 형성될 수 있다. 게이트 전극(255)을 형성함으로 써, 질화기반 발광 적층 구조체(210) 상에 형성된 전이금속 화합물 트랜지스터(250)를 제조한다.

- [0109] 게이트 전극(255)은 Cr(5 nm)/Au(40 nm)로 형성될 수 있다.

- [0111] 이하, 실시예를 통하여 본 발명을 보다 상세히 설명하고자 한다. 이들 실시예는 본 발명을 보다 구체적으로 설명하기 위한 것으로, 본 발명의 범위가 이들 실시예에 의해 한정되는 것은 아니다.

- [0113] 실시예, 전이금속 화합물 트랜지스터를 포함하는 모놀로식 집적구조의 발광다이오드(LED)

- [0114] 도 4를 참조하면, 기판으로 실리콘(Si) 웨이퍼(wafer)를 준비하고, 실리콘 웨이퍼 상에 1000 ℃ 이상의 온도에 MOCVD(금속 유기 화학 증착법, metalorganic chemical vapor deposition)을 통하여 n-GaN 층, MQW(InGaN/GaN) 층, p-GaN 층 순서로 층착시켜 발광다이오드 반도체 층을 형성한다.

- [0115] 이후, p-GaN 층 상부에 절연체로서 Al<sub>2</sub>O<sub>3</sub>를 도포한 후, Al<sub>2</sub>O<sub>3</sub> 상에 Mo(CH)<sub>6</sub> 및 (CH<sub>3</sub>)<sub>2</sub>S를 원료물질로 공급하여, MoS<sub>2</sub>를 600 ℃ 이하의 온도, Ar과 H<sub>2</sub> 분위기 하에서 MOCVD을 통하여 증착시켜, 트랜지스터 반도체 활성층을 형성하여, 반도체 적층 구조체를 제작한다.

- [0116] 이후, 메사 에칭(mesa etching)에 의하여 MoS<sub>2</sub> 층을 에칭하여 Al<sub>2</sub>O<sub>3</sub> 절연층의 일부 영역을 노출시킨 후, Al<sub>2</sub>O<sub>3</sub> 층, p형 GaN 층 및 MQW 층을 동시에 에칭하여 n형 GaN층의 일부 영역을 노출시킨다.

- [0117] n형 GaN 층의 노출된 영역에 n형 전극(Cr 5nm/Au 40nm)을 형성시키고 p-GaN 층에 p-type 전극(Cr 5nm/Au 40nm)을 형성시켜 LED를 제작하고, MoS<sub>2</sub> 층에서 소정거리로 이격된 드레인(Drain) 전극(Cr 5nm/Au 40nm)과 소스 (Source) 전극(Cr 5nm/Au 40nm)을 형성시킨다.

- [0118] 이후, 각각의 전극이 형성된 반도체 적층 구조체의 상부를 전 영역에 게이트 절연막으로 Al<sub>2</sub>O<sub>3</sub> 층을 30 nm의 두 께로 도포 한 후, MoS<sub>2</sub> 층, 드레인 전극 및 소스 전극을 도포하고 있는 게이트 트렌치(trench) 구조의 Al<sub>2</sub>O<sub>3</sub> 층 영역상에 게이트 전극(Cr 5nm/Au 40nm)을 형성시켜 박막 트랜지스터가 집적된 마이크로 발광다이오드 칩(TFT integrated Micro-LED Chip)을 제조한 후, 이로부터 마이크로 LED 디스플레이를 제조한다.

- [0120] 도 5는 상기의 실시예에 따라 제조된 발광 다이오드의 광학현미경(Optical Microscopy) 이미지로서, 도 5에서 점선으로 표시된 부분를 확대한 모식도(도 5 왼쪽 이미지)을 참조하면, n형 전극(N), p형 전극(P), 드레인 전극(D), 소스 전극(S) 및 게이트 전극(G)이 증착된 것을 확인할 수 있다.

- [0121] 도 6은 상기 실시예에 따라 제조된 발광 다이오드를 16 x 16 Active Matrix array로 구현한 구동 이미지를 연속 적으로 도시한 것이며, 도 6의 좌측부터 우측으로 'Y', 'O'. 'N', 'S', 'E', 'I'가 선명하게 관찰되는 것을 확인할 수 있다.

- [0123] 한편, 본 명세서와 도면에 개시된 본 발명의 실시 예들은 이해를 돕기 위해 특정 예를 제시한 것에 지나지 않으며, 본 발명의 범위를 한정하고자 하는 것은 아니다. 여기에 개시된 실시 예들 이외에도 본 발명의 기술적 사상

에 바탕을 둔 다른 변형 예들이 실시 가능하다는 것은, 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에게 자명한 것이다.

# 부호의 설명

[0124] 100, 200: 트랜지스터가 집적된 발광다이오드

110, 210: 질화갈륨(GaN) 기반 발광 적층 구조체

130, 230: 제1 절연층

150, 250: 전이금속 화합물 트랜지스터

# 도면

# 도면1

100

# 도면2

## 도면3a

# 도면3b

# 도면3c

## 도면3d

# *도면3e*

# 도면3f

# 도면3g

## 도면4

## 도면5

# 도면6

【심사관 직권보정사항】

【직권보정 1】

【보정항목】청구범위

【보정세부항목】청구항 5

#### 【변경전】

- (a) 기판, 제1 GaN 층, 발광활성층, 제2 GaN 층이 순차적으로 적층된 질화갈륨(GaN) 적층 구조체를 준비하는 단계;

- (b) 상기 제2 GaN 층 상에 제1 절연층을 형성하는 단계;

- (c) 상기 제1 절연층 상에 MOCVD 법을 이용하여 전이금속 화합물 활성층을 형성시킨 반도체 적층 구조체를 제공하는 단계;

- (d) 메사 에칭(mesa-etching)을 이용하여 상기 질화갈륨 구조체의 제1 GaN 층 상부의 일부 영역, 상기 제2 GaN 층 상부의 일부 영역, 상기 제1 절연층 상부의 일부 영역 각각이 외부에 노출되도록 에칭하는 단계;

- (e) 상기 제1 GaN 층의 노출된 영역, 상기 제2 GaN 층의 노출된 영역 상에 각각 제1 전극과 제2 전극을 형성하고, 상기 전이금속 화합물 활성층 상에 드레인 전극과 소스 전극이 이격되도록 형성하는 단계;

- (f) 상기 제1 전극, 상기 제2 전극, 상기 드레인 전극, 상기 소스 전극, 상기 반도체 적층 구조체의 상부 영역을 도포하는 제2 절연층을 형성하는 단계; 및

- (g) 상기 제2 절연층 상에 게이트 전극을 형성하는 단계

- 를 포함하는 트랜지스터가 집적된 발광 다이오드의 제조방법.

#### 【변경후】

- (a) 기판, 제1 GaN 층, 발광활성층, 제2 GaN 층이 순차적으로 적층된 질화갈륨(GaN) 적층 구조체를 준비하는 단계;

- (b) 상기 제2 GaN 층 상에 제1 절연층을 형성하는 단계;

- (c) 상기 제1 절연층 상에 MOCVD 법을 이용하여 전이금속 화합물 활성층을 형성시킨 반도체 적층 구조체를 제공하는 단계;

- (d) 메사 에칭(mesa-etching)을 이용하여 상기 질화갈륨 적충 구조체의 제1 GaN 충 상부의 일부 영역, 상기 제2 GaN 충 상부의 일부 영역, 상기 제1 절연충 상부의 일부 영역 각각이 외부에 노출되도록 에칭하는 단계;

- (e) 상기 제1 GaN 층의 노출된 영역, 상기 제2 GaN 층의 노출된 영역 상에 각각 제1 전극과 제2 전극을 형성하고, 상기 전이금속 화합물 활성층 상에 드레인 전극과 소스 전극이 이격되도록 형성하는 단계;

- (f) 상기 제1 전극, 상기 제2 전극, 상기 드레인 전극, 상기 소스 전극, 상기 반도체 적층 구조체의 상부 영역을 도포하는 제2 절연층을 형성하는 단계; 및

- (g) 상기 제2 절연층 상에 게이트 전극을 형성하는 단계

- 를 포함하는 트랜지스터가 집적된 발광 다이오드의 제조방법.