### (19) 대한민국특허청(KR)

### (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

G11C 29/00 (2006.01) G11C 29/24 (2006.01)

(52) CPC특허분류

*G11C 29/808* (2013.01) *G11C 29/24* (2013.01)

(21) 출원번호 10-2020-0172033

(22) 출원일자 **2020년12월10일** 심사청구일자 **2020년12월10일**

(56) 선행기술조사문헌

H. Lee 외, "Fast Built-In Redundancy Analysis Based on Sequential Spare Line Allocation," IEEE Transactions on Reliability, vol. 67, no. 1, 2018. 03.\*

KR101836748 B1

KR1020170079439 A

KR1020170079451 A

\*는 심사관에 의하여 인용된 문헌

(45) 공고일자 2022년05월19일

(11) 등록번호 10-2400631

(24) 등록일자 2022년05월17일

(73) 특허권자

#### 연세대학교 산학협력단

서울특별시 서대문구 연세로 50 (신촌동, 연세대 학교)

(72) 발명자

#### 강성호

서울특별시 마포구 양화로 45, 101동 2102호 (서교동, 메세나폴리스)

#### 김호경

경기도 용인시 수지구 성복1로 91, 105동 1101호 (성복동, 버들치마을 성복 힐스테이트 1차)

(74) 대리인

특허법인(유한)아이시스

전체 청구항 수 : 총 18 항

심사관 : 신우열

#### (54) 발명의 명칭 리던던시 분석 방법 및 리던던시 분석 장치

#### (57) 요 약

본 실시예는 행 방향으로 배치된 복수의 메모리 뱅크들과 복수의 메모리 뱅크들의 동일한 행을 대치하는 글로벌스페어(global spare)를 포함하는 메모리 칩에 대한 리던던시 분석 방법으로, 리던던시 분석 방법은: 복수의 메모리 뱅크 들의 고장 정보를 제공받고, 피봇 고장 및 차일드 고장 중 어느 하나로 분류하는 고장 분류 단계와, 글로벌 스페어 할당 우선 순위를 결정하여 글로벌 스페어를 할당하는 단계 및 남아있는 스페어로 고장이 발생한 행 및 열 중 어느 하나 이상을 대체하는 단계를 포함한다.

#### 대 표 도 - 도1

#### (52) CPC특허분류

*G11C 29/72* (2013.01) *G11C 29/76* (2013.01)

이 발명을 지원한 국가연구개발사업

과제고유번호 1711110267

과제번호2019R1A2C3011079부처명과학기술정보통신부

과제관리(전문)기관명 한국연구재단

연구사업명 중견연구자지원사업

연구과제명 인-메모리 컴퓨팅의 로버스트니스 향상을 위한 반도체 설계 기술

기 여 율 1/1

과제수행기관명 연세대학교

연구기간 2020.03.01 ~ 2021.02.28

공지예외적용 : 있음

### 명 세 서

#### 청구범위

#### 청구항 1

행 방향으로 배치된 복수의 메모리 뱅크들과 복수의 메모리 뱅크들의 글로벌 행을 대치하는 글로벌 스페어 (global spare)를 포함하는 메모리 칩에 대한 리던던시 분석 방법으로, 상기 리던던시 분석 방법은:

상기 복수의 메모리 뱅크 들의 고장 정보를 제공받고, 피봇 고장 및 차일드 고장 중 어느 하나로 분류하는 고장 분류 단계와,

상기 글로벌 스페어 할당 우선 순위를 결정하여 상기 글로벌 스페어를 할당하는 단계 및

남아있는 스페어로 상기 고장이 발생한 행 및 열 중 어느 하나 이상을 대체하는 단계를 포함하고,

상기 메모리 칩은 상기 메모리 뱅크의 어느 한 행을 대치하는 행 스페어, 상기 메모리 뱅크의 어느 한 열을 대 치하는 열 스페어, 상기 메모리 뱅크들 사이에 위치하여 인접한 메모리 뱅크들 중 어느 하나의 어느 한 열을 대 치하는 공통 열 스페어를 더 포함하고,

상기 대체하는 단계는

고장 해결을 위해 사용 가능한 상기 공통 열 스페어를 포함하는 영역의 수가 작은 상기 메모리 뱅크에 대하여 1 순위로 고장 수리를 수행하는 리던던시 분석 방법.

#### 청구항 2

제1항에 있어서,

상기 피봇 고장은, 상기 메모리 뱅크 내에서 최초로 검색된 고장, 상기 메모리 뱅크 내에서 이미 검색된 상기 피봇 고장의 행 주소 및 열 주소 모두가 상이한 고장 중 어느 하나이고,

상기 차일드 고장은 상기 메모리 뱅크 내에서 상기 피봇 고장과 상기 행 주소 및 상기 열 주소 중 어느 하나가 동일한 고장인 리던던시 분석 방법.

#### 청구항 3

제2항에 있어서,

상기 메모리 칩은.

상기 메모리 뱅크의 어느 한 행을 대치하는 행 스페어를 더 포함하고,

상기 글로벌 스페어는,

각각의 상기 메모리 뱅크의 글로벌 행 주소에서 단일한 상기 행 스페어로 대치되어야 하는 고장이 두 개 이상인 행들 중 더 많은 행에 대하여 상기 글로벌 스페어를 1 순위로 할당하는 리던던시 분석 방법.

#### 청구항 4

제3항에 있어서,

상기 글로벌 스페어는,

모든 상기 메모리 뱅크의 행 주소에서 가장 많은 상기 피봇 고장을 가질때, 상기 글로벌 스페어를 2 순위로 할 당하는 리던던시 분석 방법.

#### 청구항 5

제4항에 있어서,

상기 글로벌 스페어는,

모든 상기 메모리 뱅크의 행 주소에서 가장 많은 상기 차일드 고장을 가질때, 상기 글로벌 스페어를 3 순위로 할당하는 리던던시 분석 방법.

#### 청구항 6

삭제

#### 청구항 7

제1항에 있어서,

상기 대체하는 단계는,

가장자리에 위치한 상기 메모리 뱅크를 2 순위로 고장 수리하는 리던던시 분석 방법.

#### 청구항 8

제7항에 있어서,

상기 대체하는 단계는,

상기 남아있는 고장이 많은 메모리 뱅크를 3 순위로 고장 수리하는 리던던시 분석 방법.

#### 청구항 9

제1항에 있어서,

상기 리던던시 분석 방법은

상기 스페어를 사용하여 고칠 수 없는 상기 고장이 존재하는 경우,

상기 리던던시 분석 방법을 조기 종료하는 리던던시 분석 방법.

#### 청구항 10

제1항에 있어서,

상기 고장 정보는,

상기 고장이 발생한 메모리 뱅크 정보, 상기 고장의 행 주소, 상기 고장의 열 주소를 포함하는 리던던시 분석 방법.

#### 청구항 11

메모리의 결함 부분을 적어도 하나의 스페어로 대치하기 위한 리던던시 분석 장치로, 상기 분석 장치는:

적어도 하나 이상의 프로세서; 및

상기 프로세서에 의해 실행되는 하나 이상의 프로그램을 저장하는 메모리를 포함하며, 상기 프로그램들은 하나 이상의 프로세서에 의해 실행될 때, 상기 하나 이상의 프로세서들에서,

행 방향으로 배치된 복수의 메모리 뱅크들과 복수의 메모리 뱅크들의 동일한 행을 대치하는 글로벌 스페어 (global spare)를 포함하는 메모리 칩에 대한 리던던시 분석 방법이 수행되며, 상기 리던던시 분석 방법은:

상기 복수의 메모리 뱅크 들의 고장 정보를 제공받고, 피봇 고장 및 차일드 고장 중 어느 하나로 분류하는 고장 분류 단계와,

상기 글로벌 스페어 할당 우선 순위를 결정하여 상기 글로벌 스페어를 할당하는 단계 및

남아있는 스페어로 상기 고장이 발생한 행 및 열 중 어느 하나 이상을 대체하는 단계를 포함하고,

상기 메모리 칩은 상기 메모리 뱅크의 어느 한 행을 대치하는 행 스페어, 상기 메모리 뱅크의 어느 한 열을 대 치하는 열 스페어, 상기 메모리 뱅크들 사이에 위치하여 인접한 메모리 뱅크들 중 어느 하나의 어느 한 열을 대 치하는 공통 열 스페어를 더 포함하고,

상기 대체하는 단계는

고장 해결을 위해 사용 가능한 상기 공통 열 스페어를 포함하는 영역의 수가 작은 상기 메모리 뱅크에 대하여 1 순위로 고장 수리를 수행하는 리던던시 분석 방법이 수행되는 리던던시 분석 장치.

#### 청구항 12

제11항에 있어서,

상기 피봇 고장은, 상기 메모리 뱅크 내에서 최초로 검색된 고장, 상기 메모리 뱅크 내에서 이미 검색된 상기 피봇 고장의 행 주소 및 열 주소 모두가 상이한 고장 중 어느 하나이고,

상기 차일드 고장은 상기 메모리 뱅크 내에서 상기 피봇 고장과 상기 행 주소 및 상기 열 주소 중 어느 하나가 동일한 고장인 리던던시 분석 장치.

#### 청구항 13

제12항에 있어서,

상기 메모리 칩은,

상기 메모리 뱅크의 어느 한 행을 대치하는 행 스페어를 더 포함하고,

상기 글로벌 스페어는,

각각의 상기 메모리 뱅크의 글로벌 행 주소에서 단일한 상기 행 스페어로 대치되어야 하는 고장이 두 개 이상인 행들 중 더 많은 행에 대하여 상기 글로벌 스페어를 1 순위로 할당하는 리던던시 분석 장치.

#### 청구항 14

제13항에 있어서,

상기 글로벌 스페어는,

모든 상기 메모리 뱅크의 행 주소에서 가장 많은 상기 피봇 고장을 가질때, 상기 글로벌 스페어를 2 순위로 할당하는 리던던시 분석 장치.

#### 청구항 15

제14항에 있어서,

상기 글로벌 스페어는,

모든 상기 메모리 뱅크의 행 주소에서 가장 많은 상기 차일드 고장을 가질때, 상기 글로벌 스페어를 3 순위로 할당하는 리던던시 분석 장치.

#### 청구항 16

삭제

#### 청구항 17

제11항에 있어서,

상기 대체하는 단계는,

가장자리에 위치한 상기 메모리 뱅크를 2 순위로 고장 수리하는 리던던시 분석 장치.

#### 청구항 18

제17항에 있어서,

상기 대체하는 단계는,

상기 남아있는 고장이 많은 메모리 뱅크를 3 순위로 고장 수리하는 리던던시 분석 장치.

#### 청구항 19

제11항에 있어서,

상기 리던던시 분석 방법은

상기 스페어를 사용하여 고칠 수 없는 상기 고장이 존재하는 경우,

상기 리던던시 분석 방법을 조기 종료하는 리던던시 분석 장치.

#### 청구항 20

제11항에 있어서,

상기 고장 정보는,

상기 고장이 발생한 메모리 뱅크 정보, 상기 고장의 행 주소, 상기 고장의 열 주소를 포함하는 리던던시 분석 장치.

#### 발명의 설명

#### 기술분야

[0001] 본 기술은 리던던시 분석 방법 및 리던던시 분석 장치와 관련된다.

#### 배경기술

- [0002] 메모리 밀도와 용량이 향상되면서 메모리 오류 발생 가능성이 높아졌다. 이 문제를 해결하기 위해 메모리 내의 리던던시 메모리 셀을 이용하여 결함이 있는 셀을 대체하는 방법인 리던던시 분석(redundancy analysis)이 널리 사용된다.

- [0003] 다양한 리던던시 분석 방식이 제안되었지만 여전히 긴 리던던시 분석 대기 시간 또는 낮은 수리 속도와 같은 단점이 있다. 기존의 리던던시 분석에서는 하나의 상품 메모리에 대해 리던던시 분석을 수행하는 데 필요한 시간이 1 초 미만 이나 수백만 개 이상의 모든 생성된 메모리를 테스트하고 수리해야하므로 단일 메모리에 대해 1초 미만인 리던던시 분석 지연 시간도 전체 메모리 생산 시간에 영향을 미친다. 따라서, 최적의 복구 속도를 얻지 못하면 복구 가능한 메모리가 폐기되어 메모리 생산 수율이 감소할 수 있다.

#### 발명의 내용

#### 해결하려는 과제

[0004] 본 기술로 해결하고자 하는 과제 중 하나는 상기한 종래 기술의 난점을 해소하기 위한 것이다. 메모리에 발생한 고장들을 빠른 시간 내에 검출하여 생산성을 향상시키는 것이 본 기술로 해결하고자 하는 과제 중 하나이다.

#### 과제의 해결 수단

- [0005] 본 실시예는 행 방향으로 배치된 복수의 메모리 뱅크들과 복수의 메모리 뱅크들의 글로벌 행을 대치하는 글로벌 스페어(global spare)를 포함하는 메모리 칩에 대한 리던던시 분석 방법으로, 리던던시 분석 방법은: 복수의 메모리 뱅크 들의 고장 정보를 제공받고, 피봇 고장 및 차일드 고장 중 어느 하나로 분류하는 고장 분류 단계와, 글로벌 스페어 할당 우선 순위를 결정하여 글로벌 스페어를 할당하는 단계 및 남아있는 스페어로 고장이 발생한 행 및 열 중 어느 하나 이상을 대체하는 단계를 포함한다.

- [0006] 본 실시예의 일 태양에 있어서, 피봇 고장은, 메모리 뱅크 내에서 최초로 검색된 고장, 메모리 뱅크 내에서 이 미 검색된 피봇 고장의 행 주소 및 열 주소 모두가 상이한 고장 중 어느 하나이고, 차일드 고장은 메모리 뱅크 내에서 피봇 고장과 행 주소 및 열 주소 중 어느 하나가 동일한 고장이다.

- [0007] 본 실시예의 일 태양에 있어서, 메모리 칩은, 메모리 뱅크의 어느 한 행을 대치하는 행 스페어를 더 포함하고, 글로벌 스페어는, 각각의 메모리 뱅크의 글로벌 행 주소에서 단일한 행 스페어로 대치되어야 하는 고장이 두 개

- 이상인 행들 중 더 많은 행에 대하여 글로벌 스페어를 1 순위로 할당한다.

- [0008] 본 실시예의 일 태양에 있어서, 글로벌 스페어는, 모든 메모리 뱅크의 행 주소에서 가장 많은 피봇 고장을 가질 때, 글로벌 스페어를 2 순위로 할당한다.

- [0009] 본 실시예의 일 태양에 있어서, 글로벌 스페어는, 모든 메모리 뱅크의 행 주소에서 가장 많은 차일드 고장을 가질때, 글로벌 스페어를 3 순위로 할당한다.

- [0010] 본 실시예의 일 태양에 있어서, 메모리 칩은 메모리 뱅크의 어느 한 행을 대치하는 행 스페어, 메모리 뱅크의 어느 한 열을 대치하는 열 스페어, 메모리 뱅크들 사이에 위치하여 인접한 메모리 뱅크들 중 어느 하나의 어느 한 열을 대치하는 공통 열 스페어를 더 포함하고, 대체하는 단계는

- [0011] 고장 해결을 위해 사용 가능한 공통 열 스페어를 포함하는 영역의 수가 작은 메모리 뱅크에 대하여 1순위로 고장 수리를 수행한다.

- [0012] 본 실시예의 일 태양에 있어서, 대체하는 단계는, 가장자리에 위치한 메모리 뱅크를 2 순위로 고장 수리한다.

- [0013] 본 실시예의 일 태양에 있어서, 대체하는 단계는, 남아있는 고장이 많은 메모리 뱅크를 3 순위로 고장수리한다.

- [0014] 본 실시예의 일 태양에 있어서, 리던던시 분석 방법은 스페어를 사용하여 고칠 수 없는 고장이 존재하는 경우, 리던던시 분석 방법을 조기 종료한다.

- [0015] 본 실시예의 일 태양에 있어서, 고장 정보는, 고장이 발생한 메모리 뱅크 정보, 고장의 행 주소, 고장의 열 주소를 포함한다.

- [0016] 본 실시예는 메모리의 결함 부분을 적어도 하나의 스페어로 대치하기 위한 리던던시 분석 장치로, 분석 장치는: 적어도 하나 이상의 프로세서; 및 프로세서에 의해 실행되는 하나 이상의 프로그램을 저장하는 메모리를 포함하며, 프로그램들은 하나 이상의 프로세서에 의해 실행될 때, 하나 이상의 프로세서들에서, 행 방향으로 배치된 복수의 메모리 뱅크들과 복수의 메모리 뱅크들의 동일한 행을 대치하는 글로벌 스페어(global spare)를 포함하는 메모리 칩에 대한 리던던시 분석 방법이 수행되며, 리던던시 분석 방법은:

- [0017] 복수의 메모리 뱅크 들의 고장 정보를 제공받고, 피봇 고장 및 차일드 고장 중 어느 하나로 분류하는 고장 분류 단계와, 글로벌 스페어 할당 우선 순위를 결정하여 글로벌 스페어를 할당하는 단계 및 남아있는 스페어로 고장 이 발생한 행 및 열 중 어느 하나 이상을 대체하는 단계를 포함하는 리던던시 분석 방법이 수행된다.

- [0018] 본 실시예의 일 태양에 있어서, 피봇 고장은, 메모리 뱅크 내에서 최초로 검색된 고장, 메모리 뱅크 내에서 이 미 검색된 피봇 고장의 행 주소 및 열 주소 모두가 상이한 고장 중 어느 하나이고, 차일드 고장은 메모리 뱅크 내에서 피봇 고장과 행 주소 및 열 주소 중 어느 하나가 동일한 고장이다.

- [0019] 본 실시예의 일 태양에 있어서,메모리 칩은, 메모리 뱅크의 어느 한 행을 대치하는 행 스페어를 더 포함하고, 글로벌 스페어는, 각각의 메모리 뱅크의 글로벌 행 주소에서 단일한 행 스페어로 대치되어야 하는 고장이 두 개 이상인 행들 중 더 많은 행에 대하여 글로벌 스페어를 1 순위로 할당한다.

- [0020] 본 실시예의 일 태양에 있어서,글로벌 스페어는, 모든 메모리 뱅크의 행 주소에서 가장 많은 피봇 고장을 가질 때, 글로벌 스페어를 2 순위로 할당한다.

- [0021] 본 실시예의 일 태양에 있어서,글로벌 스페어는, 모든 메모리 뱅크의 행 주소에서 가장 많은 차일드 고장을 가질때, 글로벌 스페어를 3 순위로 할당한다.

- [0022] 본 실시예의 일 태양에 있어서,메모리 칩은 메모리 뱅크의 어느 한 행을 대치하는 행 스페어, 메모리 뱅크의 어느 한 열을 대치하는 열 스페어, 메모리 뱅크들 사이에 위치하여 인접한 메모리 뱅크들 중 어느 하나의 어느 한 열을 대치하는 공통 열 스페어를 더 포함하고,

- [0023] 대체하는 단계는 고장 해결을 위해 사용 가능한 공통 열 스페어를 포함하는 영역의 수가 작은 메모리 뱅크에 대하여 1순위로 고장 수리를 수행한다.

- [0024] 본 실시예의 일 태양에 있어서,대체하는 단계는, 가장자리에 위치한 메모리 뱅크를 2 순위로 고장 수리한다.

- [0025] 본 실시예의 일 태양에 있어서,대체하는 단계는, 남아있는 고장이 많은 메모리 뱅크를 3 순위로 고장 수리한다.

- [0026] 본 실시예의 일 태양에 있어서,리던던시 분석 방법은 스페어를 사용하여 고칠 수 없는 고장이 존재하는 경우,

리던던시 분석 방법을 조기 종료한다.

[0027] 본 실시예의 일 태양에 있어서,고장 정보는, 고장이 발생한 메모리 뱅크 정보, 고장의 행 주소, 고장의 열 주소 를 포함한다.

#### 발명의 효과

[0029]

[0028] 본 실시예에 의하면, 고장 정보 획득 중 고장 분류와 고장 수리를 진행하므로 빠른 속도로 고장을 수리할 수 있다는 장점이 제공된다.

#### 도면의 간단한 설명

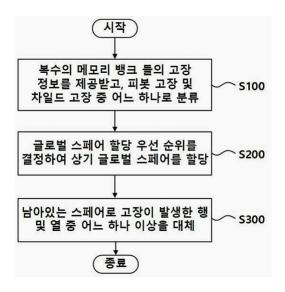

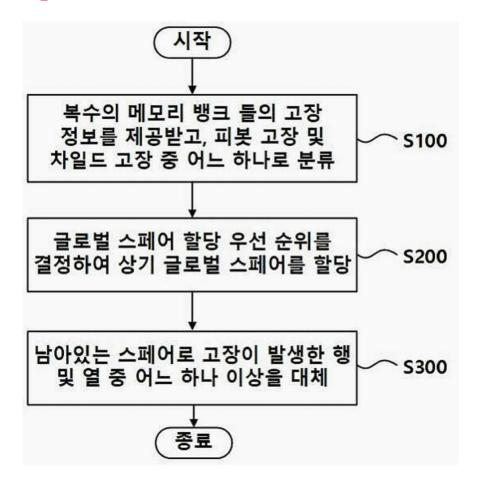

도 1은 본 실시예에 의한 리던던시 분석 방법의 개요를 나타낸 순서도이다.

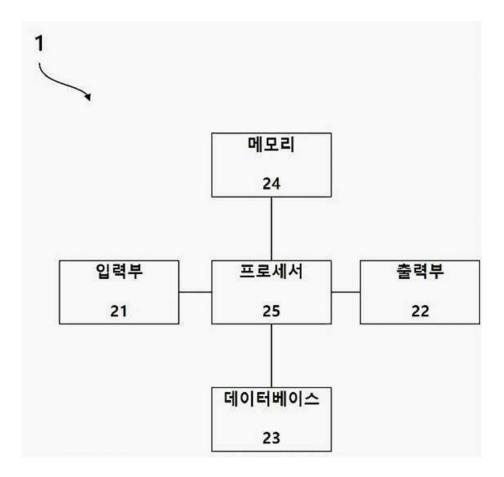

도 2는 본 실시예에 의한 리던던시 분석 장치(1)의 개요를 나타낸 블록도이다.

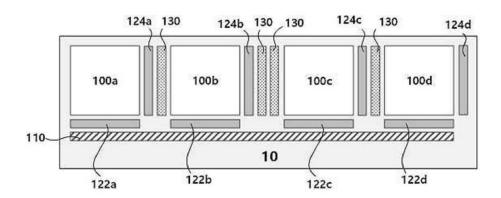

도 3은 본 실시예를 설명하기 위한 예시적인 메모리 칩의 개요도이다.

도 4(a)는 본 실시예의 설명을 위하여 ATE 장비가 테스트 대상 메모리를 테스트하여 검출한 고장을 예시적으로 표시한 도면이고, 도 4(b)는 도 4(a)로 예시된 고장들의 정보를 저장한 고장 스토리지를 예시한 도면이며, 도 4(c)는 도 4(a)로 예시된 고장들에서 피봇 고장들이 저장된 피봇 스토리지를 예시한 도면이며, 도 4(d)는 도 4(a)로 예시된 고장들에서 차일드 고장들이 저장된 차일드 스토리를 예시한 도면이다.

도 5(a)는 글로벌 8행이 글로벌 스페어(110)로 대치되어 수리되고, MC 고장을 글로벌 행스페어(110)와 로컬 열 스페어 및 공통 열 스페어()로 수리한 상태를 예시한 도면이다.

도 6(a)는 고장의 개수가 더 많은 제3 메모리 뱅크의 고장 들을 공통 스페어, 제3 열 스페어 및 제3 행 스페어 를 이용하여 수리한 상태를 도시한 도면이고, 도 6(b)는 제2 행 스페어(122b)를 이용하여 제2 메모리 뱅크 (100b)의 고장을 수리한 상태를 도시한 도면이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0030] 이하에서는 첨부된 도면들을 참조하여 본 실시예들을 설명한다. 도 1은 본 실시예에 의한 리던던시 분석 방법의 개요를 나타낸 순서도이다. 도 1을 참조하면, 본 실시예는 행 방향으로 배치된 복수의 메모리 뱅크들과 복수의 메모리 뱅크들의 동일한 행을 대치하는 글로벌 스페어(global spare)를 포함하는 메모리 칩에 대한 리던던시 분석 방법으로, 리던던시 분석 방법은: 복수의 메모리 뱅크 들의 고장 정보를 제공받고, 피봇 고장 및 차일드 고장 중 어느 하나로 분류하는 고장 분류 단계(S100)와, 글로벌 스페어 할당 우선 순위를 결정하여 글로벌 스페어를 할당하는 단계(S200) 및 남아있는 스페어로 고장이 발생한 행 및 열 중 어느 하나 이상을 대체하는 단계 (S300)를 포함한다.

- [0031] 도 2는 본 실시예에 의한 리던던시 분석 장치(1)의 개요를 나타낸 블록도이다. 도 2를 참조하면, 도 2는 본 실시예에 의한 리던던시 분석 장치(1)의 개요를 도시한 블록도이다. 도 2를 참조하면, 본 실시예에 따른 리던던시 분석 장치(20)는 입력부(110), 출력부(22), 프로세서(25), 메모리(24) 및 데이터베이스(23)을 포함한다. 도 2의 리던던시 분석 장치(20)는 일 실시예에 따른 것으로서, 도 2에 도시된 모든 블록이 필수 구성요소는 아니며, 다른 실시예에서 리던던시 분석 장치(1)에 포함된 일부 블록이 추가, 변경 또는 삭제될 수 있다. 한편, 리던던시 분석 장치(1)는 리던던시 분석을 수행하는 컴퓨팅 장치로 구현될 수 있으며, 리던던시 분석 장치(1)에 포함된 각 구성 요소들은 각각 별도의 소프트웨어 장치로 구현되거나, 소프트웨어가 결합된 별도의 하드웨어 장치로 구현될 수 있다.

- [0032] 리던던시 분석 장치(1)는 고장 분류 단계(S100, 도 1 참조)와, 글로벌 스페어 할당 단계(S200, 도 1 참조) 및 남아있는 스페어로 대체하는 단계(S300, 도 1 참조)를 수행한다.

- [0033] 입력부(21)는 고장 정보에 상응하는 신호 또는 데이터를 입력받는 수단을 의미한다. 입력부(21)는 ATE 장치 (automatic test equipment, 미도시)로부터 테스트 대상 메모리의 고장 정보를 제공받을 수 있다. 또한, 입력부 (21는 프로세서(25)과 연동하여 다양한 형태의 신호 또는 데이터를 입력하거나, 외부 장치와 연동하여 직접 데이터를 획득하여 프로세서(25)로 전달할 수도 있다. 입력부(21)는 실패 로그정보(fail log), 다양한 조건정보 또는 제어신호 등을 입력하거나 입력 받기 위한 장치 또는 서버 일수 있으나 반드시 이에 한정되는 것은 아니다.

- [0034] 출력부(22)는 프로세서(25)과 연동하여 리던던시 분석 결과, 실패 로그정보, 배열된 스페어의 정보 등을 표시할 수 있다. 출력부(22)는 소정의 정보를 출력하기 위하여 리던던시 분석 장치(1)에 구비된 디스플레이(미도시), 스피커 등을 통해 다양한 정보를 표시하는 것이 바람직하나 반드시 이에 한정되는 것은 아니다.

- [0035] 프로세서(25)은 메모리(24)에 포함된 적어도 하나의 명령어 또는 프로그램을 수행한다. 본 실시예에 따른 프로 세서(25)는 입력부(21) 또는 데이터베이스(23)로부터 획득한 데이터를 기반으로 각 단계를 수행하기 위한 데이터를 연산하고, 리던던시 분석한다.

- [0036] 메모리(24)는 프로세서(25)에 의해 실행 가능한 적어도 하나의 명령어 또는 프로그램을 포함한다. 메모리(24)는 관심 영역을 추출, 클래스 결정 등의 처리를 수행하기 위한 명령어 또는 프로그램을 포함할 수 있다. 메모리(24)는 각 단계에서 수행된 결과, 중간값 등의 연관된 값들을 저장할 수 있다.

- [0037] 데이터베이스(23)은 데이터베이스 관리 프로그램(DBMS)을 이용하여 컴퓨터 시스템의 저장공간(하드디스크 또는 메모리)에 구현된 일반적인 데이터구조를 의미하는 것으로, 데이터의 검색(추출), 삭제, 편집, 추가 등을 자유롭게 행할 수 있는 데이터 저장형태를 뜻하는 것으로, 오라클(Oracle), 인포믹스(Infomix), 사이베이스 (Sybase), DB2와 같은 관계형 데이타베이스 관리 시스템(RDBMS)이나, 겜스톤(Gemston), 오리온(Orion), 02 등과 같은 객체 지향 데이타베이스 관리 시스템(OODBMS) 및 엑셀론(Excelon), 타미노(Tamino), 세카이주 (Sekaiju) 등의 XML 전용 데이터베이스(XML Native Database)를 이용하여 본 발명의 일 실시예의 목적에 맞게 구현될 수 있고, 자신의 기능을 달성하기 위하여 적당한 필드(Field) 또는 엘리먼트들을 가지고 있다.

- [0038] 본 실시예에 따른 데이터베이스(23)은 로그정보, 배치된 스페어들의 정보, 조건 정보, 고장 진단 결과정보 등을 저장하고, 저장된 데이터를 제공할 수 있다. 한편, 데이터베이스(24)는 리던던시 분석 장치(1) 내에 구현되는 것으로 기재하고 있으나 반드시 이에 한정되는 것은 아니며, 별도의 데이터 저장장치로 구현될 수도 있다.

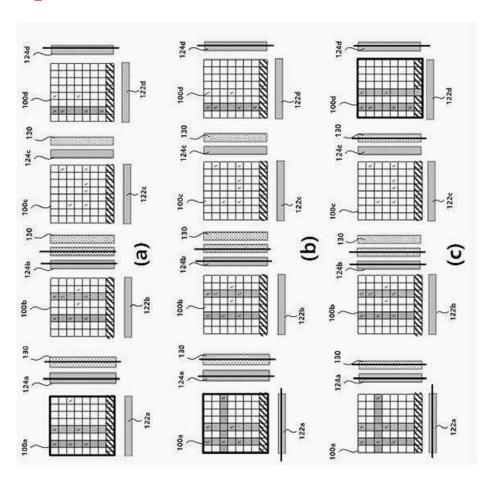

- [0039] 도 3은 본 실시예를 설명하기 위한 예시적인 메모리 칩(1)의 개요도이다. 메모리 칩(1)은 데이터를 저장하는 소자가 행과 열에 따라 배치된 제1 내지 제4 메모리 뱅크(100a, 100b, 100c, 100d)와, 각 메모리 뱅크의 행을 대치하여 메모리 뱅크에 발생한 고장을 수리하는 제1 내지 제4 로컬 행 스페어(local row spare, 122a, 122b, 122c, 122d)와, 메모리 뱅크의 열을 대치하여 메모리 뱅크에 발생한 고장을 수리하는 제1 내지 제4 로컬 열 스페어(local column spare, 124a, 124b, 124c, 124d)를 포함한다.

- [0040] 일 예로, 제1 로컬 행 스페어(122a)는 제1 메모리 뱅크(100a)의 행을 대치하고. 제2 로컬 행 스페어(122b)는 제 2 메모리 뱅크(100b)의 행을 대치하고. 제3 로컬 행 스페어(122c)는 제3 메모리 뱅크(100c)의 행을 대치하고. 제4 로컬 행 스페어(122c)는 제4메모리 뱅크(100c)의 행을 대치하여 각 메모리 뱅크에 발생한 고장을 수리한다.

- [0041] 또한, 제1 로컬 열 스페어(124a)는 제 메모리 뱅크(100a)의 열을 대치하고. 제2 로컬 열 스페어(124b)는 제2 메모리 뱅크(100b)의 열을 대치하고. 제3 로컬 열 스페어(124c)는 제3 메모리 뱅크(100c)의 열을 대치하고. 제4 로컬 열 스페어(124c)는 제4 메모리 뱅크(100c)의 열을 대치하여 각 메모리 뱅크에 발생한 고장을 수리한다.

- [0042] 공통 열 스페어(common column spare, 130)는 메모리 뱅크 들의 사이에 위치한다. 로컬 행 스페어(122a, 122b, 122c, 122d) 및/또는 로컬 열 스페어(124a, 124b, 124c, 124d)가 모두 사용되어 메모리 뱅크에 발생한 고장을 고칠 수 없을 때, 공통 열 스페어(130)를 이용하여 고장을 고칠 수 있다.

- [0043] 일 예로, 제1 메모리 뱅크(100a)에 발생한 고장이 서로 다른 두 개의 열 주소를 가지고, 제2 메모리 뱅크(100b)에 발생한 고장이 하나의 열 주소를 가지는 경우가 있을 수 있다. 제2 메모리 뱅크(100b)에 발생한 고장은 제2 로컬 열 스페어(124b)로 해당 열을 대체하여 고칠 수 있고, 제1 로컬 열 스페어(124a)와 공통 열 스페어(130)로 제1 메모리 뱅크(100a)의 서로 다른 두 열을 대체하여 고장을 고칠 수 있다. 글로벌 스페어(110)는 제1 내지 제4 메모리 뱅크들(100a, 100b, 100c, 100d)에서 동일한 행 주소(글로벌 행 주소)를 대체하여 각각의 메모리 뱅크들에서 동일한 행 주소에 발생한 고장을 고칠 수 있다.

- [0044] 종래 기술은 복수개의 글로벌 열 스페어, 글로벌 행 스페어, 공통 행 스페어, 공통 열 스페어를 배치하고, 이들을 고장이 발생한 메모리 뱅크의 행 또는 열을 대체하도록 하여 고장을 수리하였다. 이러한 예비 자원들의 조합 방법에 대한 경우의 수가 많아 이들을 조합하여 처리하는 과정에 많은 시간이 소모되었다.

- [0045] 그러나 메모리에서 셀을 선택하는 과정에서 행 방향의 워드 라인을 선택한 후 셀을 선택하기 때문에 행 방향에 존재하는 메모리 뱅크에서 고장 군집이 발생할 확률이 높으며, 기존에 제안된 다양한 메모리 예비 자원 구조에 서 적용되는 공통 스페어가 행 방향과 열 방향으로 모두 존재하기 때문에 수리 방법 탐색 시 분석시간이 많이 소요된다. 그러나, 상기한 구성을 가지는 본 실시예는 후술할 리던던시 분석 방법이 적용됨에 따라 고장의 분포

에 따라 예비자원을 효율적으로 사용할 수 있어 수리에 효과적이라는 장점이 제공된다.

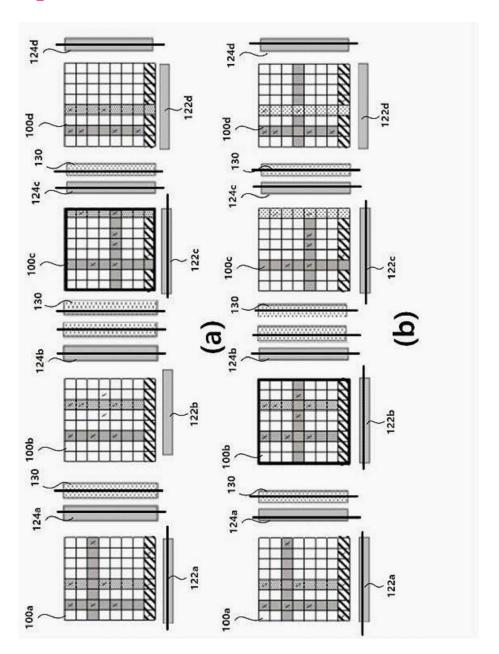

- [0046] 도 4(a)는 본 실시예의 설명을 위하여 ATE 장비가 테스트 대상 메모리를 테스트하여 검출한 고장을 예시적으로 표시한 도면이고, 도 4(b)는 도 4(a)로 예시된 고장들의 정보를 저장한 고장 스토리지를 예시한 도면이며, 도 4(c)는 도 4(a)로 예시된 고장들에서 피봇 고장들이 저장된 피봇 스토리지를 예시한 도면이며, 도 4(d)는 도 4(a)로 예시된 고장들에서 차일드 고장들이 저장된 차일드 스토리를 예시한 도면이다.

- [0047] 도 1 내지 도 4를 참조하면, 간단하고 명료한 설명을 위하여 각 메모리 뱅크는 8 \* 8의 셀들을 포함하는 것을 예시한다. ATE(미도시)로부터 메모리의 고장 정보를 제공받는다. 고장이 있는 셀은 도 4(a)에서 X로 도시되었다. 고장 정보는 ATE가 테스트 대상 메모리 칩을 조사하면서 획득된다. 획득된 고장 정보는 메모리 뱅크 정보, 고장이 발생한 행, 열의 순서와 무관하게 제공될 수 있다. 일 예로, 고장 정보는 고장이 위치하는 메모리 뱅크, 고장의 행 주소, 열 주소를 포함할 수 있다.

- [0048] 고장 정보가 제공됨에 따라 도 4(b)로 예시된 것과 같이 고장 스토리지에 고장 정보가 기록된다. 일 예로, 고장 번호는 ATE에서 검출하여 제공된 순서에 따라 정해질 수 있다. 고장이 속한 그룹과 수리 상태가 저장된다. 고장 이 속한 그룹은 고장이 속한 행과 열의 고장 정보에 따라 정해지는데 이전에 검출되었던 고장 중에서 같은 행과 열을 가진 고장이 있다면 해당 고장이 존재하는 그룹에 속하고, 중복되는 행 주소와 열 주소를 가지는 고장이 없다면 새로운 그룹에 속한다. 고장이 검출되는 순서에 따라 다르게 나타날 수 있으나 결과적으로 고장 검출 순서에 상관없이 각 그룹에 속한 고장들의 행과 열 방향 주소가 동일하다

- [0049] 제공된 고장 정보에 따라 고장을 분류한다(S100). 일 예로, 해당 메모리 뱅크에서 최초로 검출한 고장은 피봇 고장이다. 또한, 메모리 뱅크에서 이미 검출된 피봇 고장과 열 주소 및 행 주소가 서로 상이한 고장은 피봇 고장이다. 피봇 고장은 도 4(a)에서 적색 사각형으로 예시되었으며, 도 4(c)로 예시된 것과 같이 피봇 스토리지에 저장된다. 피봇 스토리지에 저장하는 고장 정보는 고장이 속한 메모리 뱅크와 이에 대한 연번, 고장 주소, 후술할 MR, MC의 개수 정보를 저장할 수 있다.

- [0050] 피봇 고장과 동일한 행 주소를 가지거나, 동일한 열 주소를 가지는 고장을 차일드 고장(child)고장이다. 차일드 고장은 도 4(e)로 예시된 것과 같이 차일드 스토리지에 저장된다. 차일드 스토리지에 저장된 고장 정보는 고장이 속한 메모리 뱅크와 이에 대한 연번, 고장 주소를 저장한다.

- [0051] 도 4(a)와 도 4(c)를 참조하면, 단일한 고장은 해당 고장의 행을 행 스페어로 대체하거나 해당 고장의 열을 열 스페어로 대체하여 고칠 수 있다. 그러나, 일 예로, 동일한 행 주소를 가지는 고장의 개수가 열 스페어의 개수보다 많을 때, 이러한 고장들은 행 스페어로만 고칠 수 있는 고장이다(MR, must repair in row spare). 또한, 동일한 열 주소를 가지는 고장의 개수가 행 스페어의 개수보다 많을 때, 이러한 고장들은 열 스페어로만 고칠 수 있는 고장이다(MC, must repair in column spare).

- [0052] 수집된 고장 정보는 도 4(b)로 도시된 고장 스토리지와 도 4(d)로 도시된 글로벌 스페어 후보 스토리지에 저장된다. 행방향 메모리 라인을 기준으로 각 뱅크의 피봇 고장, 차일드 고장, MR, MC의 개수를 저장한다. 일 실시예로, 도 4(a)로 도시된 것과 같이 뱅크 1의 1행 2열, 3행 2열 및 5행 2열과 같이 동일한 열 주소를 가지며, 행스페어 개수 이상의 고장인 MC 고장이 발생할 수 있다. 예시된 실시예에서, ATE로부터 고장 정보가 제공되어 고장을 분류하는 과정에서, MC 고장들은 열 스페어를 활용하여 고칠 수 있다. 따라서, 해당 MC의 피봇 고장을 저장하는 고장 스토리지에서는 피봇 고장 정보와 함께 상태 정보(Status)는 수리 해법이 도출되었음을 나타내는 1이 저장된다.

- [0053] 수리 상태 도출된 고장들의 차일드 고장들은 도 4(c)로 예시된 차일드 스토리와 도 4(d)로 예시된 글로벌 스페어 후보 스토리지에서 삭제된다. 용이한 이해를 위하여 도 4(a)에서 피봇 고장은 적색 사각형으로, 수리 방법이 도출되어 삭제된 차일드 고장은 파란색 실선으로 도시되었다. 따라서, 도 4(b)로 예시된 피봇 스토리지에는 도 4(a)에서 적색의 사각형으로 도시된 피봇 고장의 정보와 수리 상태가 도출되었는지 여부를 의미하는 상태 (Status) 정보가 저장된다. 또한 도 4(c)로 예시된 차일드 스토리지에는 도 4(a)에서 청색의 실선으로 예시된 차일드 고장의 정보는 삭제되고, 적색의 사각형으로 도시된 피봇 고장의 정보와 MC 해당 여부를 나타내는 정보가 저장된다.

- [0054] 예시된 바와 같이 고장 정보 수집, 피봇 고장, 차일드 고장의 분류 및 MR 고장과 MC 고장의 분류는 ATE로부터 고장 정보를 획득하면서 수행된다. 종래기술에서는 모든 고장 정보를 획득한 이후, 수리 솔루션을 도출하였으나, 본 실시예에 의하면 고장 정보를 획득하는 과정에서 고장 솔루션을 도출하므로 고장 수리를 솔루션을 도출하는 시간을 감소시킬 수 있다는 장점이 제공된다.

- [0055] 이어서 글로벌 스페어 할당 우선 순위를 결정하고, 글로벌 행 스페어를 할당한다(S200). 도 3으로 예시된 것과 같이 글로벌 행 스페어(110)는 제1 내지 제4 메모리 뱅크들(100a, 100b, 100c, 100d)의 공통 행(이하, 글로벌 행)을 대체하여 메모리 뱅크의 고장을 수리할 수 있다. 글로벌 행 스페어(110)는 상술한 바와 같이 제1 내지 제4 메모리 뱅크들(100a, 100b, 100c, 100d)의 공통 행을 대체하므로, 복수의 메모리 뱅크들(100a, 100b, 100c, 100d)의 각 행별로 우선 순위를 파악한다.

- [0056] 우선, 어떠한 글로벌 행에 더 많은 MR이 있는지 파악한다. 일 예로 글로벌 행들 중에서 두 개 이상의 MR 이 있으면, 이들 중 더 많은 MR을 포함하는 글로벌 행을 글로벌 행 스페어(110)로 대체하여 수리한다. 도 4로 예시된 실시예에서, MR 고장은 없다.

- [0057] 이어서, 글로벌 행 중에서 더 많은 피봇 고장을 가진 글로벌 행을 글로벌 행 스페어(110)로 대체하여 수리한다. 도 4로 예시된 실시예에서, 글로벌 3 행, 4행 및 8행은 모두 피봇 고장 세개를 포함하여 동일하다.

- [0058] 글로벌 행에 포함된 피봇 고장의 개수가 모두 동일하면 글로벌 행에 포함된 차일드 고장의 개수가 많은 글로벌 행을 글로벌 행 스페어(110)로 대체하여 수리한다. 도 4로 예시된 실시예에서, 글로벌 3 행, 4행 및 8행은 모두 피봇 고장 세개를 포함하나, 글로벌 4행 및 8행은 각각 하나 씩의 차일드 고장을 더 포함한다. 따라서, 글로벌 4행 및 8행이 글로벌 4행에 비하여 우선 순위가 높다.

- [0059] 동일한 우선 순위가 존재하는 경우에는 MC에 해당하지 않고, 먼저 검출된 행에 대하여 우선 순위를 두어 글로벌 행 스페어(110)로 대체한다. 이것은 MC에 해당하면 컬럼 스페어로 대체되어 수리될 수 있기 때문이다. 도 4로 예시된 실시예에서, 글로벌 4행에서, 뱅크 1의 4행 4열의 고장은 도시된 바와 같이 MC 고장이므로, 글로벌 8행의 우선 순위가 높다. 따라서, 글로벌 8 행이 글로벌 스페어(110)로 대체된다.

- [0060] 이어서, 도 5(a) 내지 도 6(b)를 참조하여 남아있는 스페어로 고장이 발생한 행 및 열 중 어느 하나 이상을 대체하는 과정을 설명한다(S300). 도 5(a)는 글로벌 8행이 글로벌 스페어(110)로 대치되어 수리되고, MC 고장을 글로벌 행스페어(110)와 로컬 열 스페어(124a, 124b) 및 공통 열 스페어(130)로 수리한 상태를 예시한다. 사용된 스페어들은 용이한 이해을 위하여 검정색 실선으로 표시하였다.

- [0061] 남아 있는 로컬 행 스페어, 로컬 열 스페어 및 공통 열 스페어를 이용하여 수리를 진행한다. 다양한 스페어의 사용으로 발생할 수 있는 경우의 수를 감소시키기 위하여 사용할 수 있는 공통 스페어를 포함하는 영역의 수가 적은 메모리 뱅크를 우선적으로 수리한다. 일 예로, 제1 메모리 뱅크(100a)가 사용할 수 있는 공통 열 스페어는 없다. 따라서, 제1 메모리 뱅크(100)a가 사용할 수 있는 공통 열 스페어를 포함하는 영역의 개수는 0이다. 제2 메모리 뱅크(100b)가 사용할 수 있는 공통 열 스페어는 제2 메모리 뱅크(100b)가 사용할 수 있는 공통 열 스페어는 제2 메모리 뱅크(100b)가 사용할 수 있는 공통 스페어를 포함하는 영역 개수는 1이다. 이에 반하여 제3 메모리 뱅크(100c)가 사용할 수 있는 공통 스페어를 포함하는 영역은 제3 메모리 뱅크(100c)의 좌측 하나와 우측의 하나이므로, 제3 메모리 뱅크(100c)가 사용할 수 있는 공통 스페어를 포함하는 영역의 개수는 2이다. 도 5(a)로 예시된 것과 같이 제1 메모리 뱅크(100a)는 사용할 수 있는 공통 스페어를 포함하는 영역의 개수가 0이므로 우선적으로 수리된다. 따라서, 도 5(b)로 도시된 것과 같이 제1 로컬 행 스페어(122a)로 고장이 수리된다.

- [0062] 고장이 많을수록 수리 가능성이 낮을 수 있으므로, 수리 불가능 시에 수리 시간을 줄이기 위하여 메모리 뱅크 내에 수리되지 않은 고장이 더 많은 메모리 뱅크를 우선적으로 수리할 수 있다. 동일한 순위가 있을 때에는 가장 자리의 메모리 뱅크를 우선순위로 하여 수리한다. 가장자리에 위치한 메모리 뱅크는 사용할 수 있는 공통 스페어의 개수가 적을 수 있기 때문이다. 도 5(b)로 예시된 실시예에서, 제2 메모리 뱅크(100b)가 고장 수리에 사용할 수 있는 열 스페어를 포함하는 영역의 개수는 우측의 하나이다. 반면에 제3 메모리 뱅크(100c)가 고장 수리에 사용할 수 있는 열 스페어의 개수는 좌측의 하나와 우측의 하나이므로, 영역의 개수는 2이다. 반면에 제4 메모리 뱅크는 좌측의 하나의 공통 열 스페어를 사용할 수 있으므로, 영역의 개수는 1이다.

- [0063] 제4 메모리 뱅크(100d)와 제2 메모리 뱅크(100b)는 모두 사용할 수 있는 공통 열 스페어를 포함하는 영역의 개수는 1로 동일하고, 남아있는 고장의 개수도 동일하다. 이러한 경우에는 도 5(c)로 예시된 것과 같이 공통 스페어(130)를 이용하여 가장 자리의 제4 메모리 뱅크(100d)의 고장을 수리한다.

- [0064] 남아있는 제2 메모리 뱅크(100b)는 우측 하나의 공통 열 스페어를 사용할 수 있고, 제3 메모리 뱅크(100c)는 좌 측 하나의 공통 열 스페어를 사용할 수 있어 사용할 수 있는 공통 스페어의 영역 수는 동일하다. 상술한 바와 같이 고장의 개수가 더 많은 제3 메모리 뱅크(100c)의 고장 들을 공통 스페어(130), 제3 열 스페어(124c) 및 제3 행 스페어(122c)를 이용하여 우선적으로 수리한다. 수리된 상태는 도 6(a)로 예시된 것과 같다. 이어서, 도 6(b)로 도시된 것과 같이 남은 제2 행 스페어(122b)를 이용하여 메모리 뱅크 2(100b)의 고장을 수리할 수 있다.

[0065] 상기한 실시예를 통하여 복수의 메모리 뱅크들에 발생한 고장들을 수리하는 과정을 예시하였으나, 스페어들을 이용하여 수리하여도 발생한 고장들을 모두 수리할 수 없는 경우도 있을 수 있으며, 이러한 경우에는 수리 과정을 조기 종료하여 수리 시간을 단축할 수 있다.

#### [0067] 모의 실험 결과

[0068] 본 실시예와 종래 기술의 RA 알고리즘의 수리율과 솔루션 탐색 시간을 비교하였다. 비교 대상인 종래 기술의 알고리즘으로 기존의 단순한 메모리 예비자원 구조와의 알고리즘 성능 비교를 위해 100% 정규화된 수리율을 달성하는 VERA 알고리즘을 이용하였다. VERA 알고리즘은 전처리과정이 필요없는 RA 알고리즘 중 가장 적은 분석시간을 필요로 하는 알고리즘이다. 각각의 실험에서 4개의 1024 \* 1024 메모리 뱅크를 동일하게 사용하였고, 현실적인 고장분포에 가깝다고 알려진 polya-eggenberger 고장 분포를 사용하여 10000번의 실험을 통해 평균값을 구해 결과값의 공정성을 높였다. 또한 각각의 알고리즘마다 수리를 위해 사용하는 예비 자원의 크기를 local spare의 크기를 기준으로 동일하게 맞추어 알고리즘의 성능을 비교하였다. 공통 스페어는 로컬 스페어와 동일한 크기이므로 동일한 개수의 로컬 스페어로 환산하였고, 글로벌 스페어는 도 3과 같이 local spare 4개의 크기에 해당되므로 4개의 local spare로 환산하였다. 실험결과 표 1,2는 단순한 메모리 예비자원 적용 시 메모리 뱅크마다 행과 열 방향으로 각각 4개의 local spare 크기의 예비자원이 존재할 때 결과를 나타낸다.

#### [0069] [ 표 1]

| # of faults | 9    | 10   | 11   | 12   | 13   | 14   | 15   | 16   |  |

|-------------|------|------|------|------|------|------|------|------|--|

| VERA        | 0.99 | 0.99 | 0.99 | 0.96 | 0.90 | 0.81 | 0.67 | 0.53 |  |

| 본 실시예       | 0.99 | 0.99 | 0.98 | 0.96 | 0.92 | 0.88 | 0.85 | 0.82 |  |

#### [0070]

####

| # of faults  | 9    | 10   | 11   | 12   | 13   | 14   | 15   | 16   |

|--------------|------|------|------|------|------|------|------|------|

| VERA (s)     | 0.55 | 0.64 | 0.75 | 0.88 | 0.99 | 1.19 | 1.22 | 1.36 |

| 본 실시예<br>(s) | 0.44 | 0.52 | 0.61 | 0.73 | 0.83 | 0.93 | 1.13 | 1.12 |

### [0073]

- [0075] 표 1은 본 실시예와 종래 기술과의 수리율을 비교한 표이다. 표 1로 예시된 바와 같이 본 실시예에의한 RA 알고리즘이 100% normalized 수리율을 달성하는 알고리즘에 비하여 대체적으로 더 높은 수리율을 보이며, 고장이 많을수록 기존의 알고리즘보다 수리율이 더 증가함을 확인할 수 있다. 표 2는 본 실시예에 의한 알고리즘과 종래기술과의 솔루션 탐색시간을 비교한 표로, 다른 알고리즘에 비하여 해당 알고리즘의 솔루션 탐색시간이 적은 것을 확인할 수 있다.

- [0076] 이를 통하여 본 실시예에 의하면 다양한 메모리 예비자원 구조의 효율적인 예비자원 사용을 통해 이전의 단순한 메모리 예비자원 구조로 달성했던 수리율보다 더 높은 수리율을 달성할 수 있으며, 솔루션 탐색시간 또한 이전보다 단축할 수 있음을 확인할 수 있다.

- [0078] 본 발명에 대한 이해를 돕기 위하여 도면에 도시된 실시예를 참고로 설명되었으나, 이는 실시를 위한 실시예로, 예시적인 것에 불과하며, 당해 분야에서 통상적 지식을 가진 자라면 이로부터 다양한 변형 및 균등한 타 실시 예가 가능하다는 점을 이해할 것이다. 따라서, 본 발명의 진정한 기술적 보호범위는 첨부된 특허청구범위에 의해 정해져야 할 것이다.

#### 부호의 설명

[0079] S100~S300: 본 실시예에 의한 리던던시 분석 방법의 개요적 각 단계

1: 리던던시 분석 장치

21:입력부

22: 출력부

25: 프로세서

24: 메모리

23: 데이터베이스

10: 메모리 칩

110: 글로벌 행 스페어

130: 공통 스페어

100a, 100b, 100c,100d: 제1 내지 제4 메모리 뱅크 122a, 122b, 122c, 122d: 제1 내지 제4 행 스페어

124a, 124b, 124c, 124d: 제1 내지 제4 열 스페어

#### 도면

| X           | X           |             | $\Box$       | X            | X     |     |     | I             |             |             | X           | X         |          |

|-------------|-------------|-------------|--------------|--------------|-------|-----|-----|---------------|-------------|-------------|-------------|-----------|----------|

| -           | -           |             | v  -         | V            | X     | H   | X   | +             |             | X           | *           |           | 1        |

| *           | X           |             | X            | X            | X     | X   | A   | +             | $\vdash$    | $H \vdash$  | +++         | X         | +        |

| X           | Î           | H           | 1 H          | 1            | 1     |     | X   | X             | X           | X           | *           |           | +        |

|             |             |             |              |              |       | ЩГ  |     |               |             |             |             |           |          |

|             | -           | V           | +H           |              | Н     | H   | 3   | +             | 1           | $H \vdash$  | *           | X         | $\vdash$ |

|             | X           | X           |              |              | ш     | ш   |     | _             | Ш.          |             | ш           | A         |          |

|             |             |             |              |              |       | (a) |     |               |             |             |             |           |          |

| ault<br>No. | Bank<br>No. | Row<br>Add. | Col<br>Add.  | Group<br>No. | Statu | ıs  | Fau |               | Bank<br>No. | Row<br>Add. | Col<br>Add. | MR        | M        |

| 1           | 1           | 1           | 2            | 1            | 1     |     | 1   |               | 1           | 1           | 2           | 0         | 1        |

| 1           | 3           | 3           | 3            | 1            | 0     |     | 1   | 1 3           |             | 3           | 3           | 0         | 0        |

| 1           | 2           | 3           | 3            | 1            | 0     |     | 1   | 1 2           |             | 3           | 3           | 0         | 1        |

| 2           | 1           | 3           | 2            | 1            | 1     |     | 1   | 1 4           |             | 1           | 2           | 0         | 1        |

| 1           | 4           | 1           | 2            | 1            | 0     | -   | 2   | $\rightarrow$ | 1 8         |             | 1           | 0         | 0        |

| 2           | 1           | 5           | 2            | 1            | 1     |     | 2   | 9             | 3           | 8           | 4           | 0         | 0        |

|             |             |             |              |              |       |     |     |               |             |             |             |           |          |

| 9           | 1           | 8           | 7            | 1            | 1     |     | 4   |               | 1           | 3           | 8           | 0         | 0        |

| 8           | 2           | 4           | 7            | 2            | 0     |     | 4   |               | 3           | 5           | 5           | 1         | 0        |

|             |             | (           | b)           |              |       |     |     |               |             | (           | c)          |           |          |

| Row         |             | of<br>ivot  | #of<br>Child | # c          |       | RO  |     |               | ult<br>lo.  | Bank<br>No. |             | ow<br>dd. | Col      |

| 1           |             |             |              |              |       | 4   |     | 7             | 1           | 3           |             | 5         | 3        |

| 3           |             | 3 0         |              | -            | 0 4   |     | Ī   | 2             |             | 3           |             | 5         | 8        |

|             | -           | -           | ****         | •            | -     |     | Ī   | 1             |             | 1 4         | 1           | 1         | 4        |

| 8           | -           | 3           | 1            | 0            |       | 1   |     | 3             |             | 3           | 5           |           | 6        |

| 2           |             | 1           | 0            | 0            |       | 6   |     | 1             |             | 1           | 1           | 8         | 7        |

| 5           |             | 1           | 3 0          |              |       | 5   |     |               | 1           | *****       |             | 4         | 7        |

| 4           |             | 3           | 1            | 0            |       | 2   | L   | _             |             | _           |             |           |          |

|             | - 1         | 100         | (d)          | 747-         |       | 10  |     |               |             |             | (e)         |           |          |