# (19)대한민국특허청(KR) (12) 공개특허공보(A)

(51) 。Int. Cl. *G06F 11/26* (2006.01)

(11) 공개번호

10-2006-0066233

(43) 공개일자

2006년06월16일

(21) 출원번호10-2004-0104761(22) 출원일자2004년12월13일

(71) 출원인 학교법인연세대학교

서울 서대문구 신촌동 134번지

(72) 발명자 강성호

서울시 서대문구 신촌동 134번지 연세대학교 공과대학 전기.전자공학과

C631 송동섭

서울시 서대문구 신촌동 134번지 연세대학교 공과대학 전기.전자공학과

C631

(74) 대리인 리앤목특허법인

심사청구: 있음

# (54) 내장형 자체테스트 패턴 생성시의 하드웨어 오버헤드축소방법 및 장치

#### 요약

본 발명은 결정패턴 생성 전에도 두 하드웨어가 많은 역할을 수행하도록 하여, 기존의 의사무작위 패턴 생성에 필요한 하드웨어를 줄이면서도, 전혀 테스트 시간이 증가되지 않도록 하는 방법을 제공함을 목적으로 한다. 스캔체인을 이용하여 CUT를 테스트하는 내장형 자체테스트 방법으로서, LFSR을, N비트의 패턴카운터 및 비트카운터의 N비트중 한 비트를 제외한 (N-1)비트중 한 비트만 스캔체인으로 보내도록 구성하는 것을 특징으로 한다.

# 대표도

도 2

#### 색인어

BIST, LFSR, 테스트패턴

#### 명세서

#### 도면의 간단한 설명

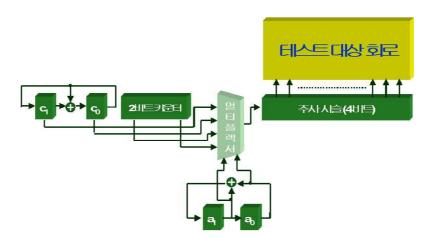

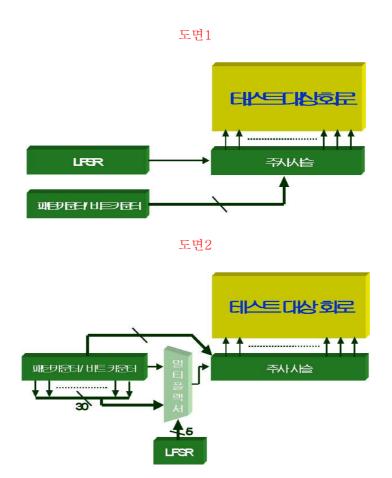

도1은 종래의 의사무작위 패턴의 생성을 나타내는 원리도.

도2는 본 발명에 따른 의사무작위 패턴의 생성을 나타내는 원리도.

도3은 본 발명의 원리를 간단하게 구현한 일실시예도.

#### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 BIST에 있어서의 의사무작위 패턴 생성시의 하드웨어 오버헤드를 최소화하는 방법에 관한 것이다. 본 발명은 대한민국 정보통신부 대학 IT 연구센터의 육성 및 지원사업의 결과로서 수행된 것이다.

내장형 자체 테스트 기법(BIST: Built-In Self Test)은 의사무작위 패턴 생성방법(pseudo-random pattern generation) 과 결정패턴 생성방법(deterministic pattern generation)의 두 가지 테스트 시퀀스로 구분할 수 있다.

의사무작위 패턴 생성 방법은 LFSR이라는 구조를 가장 널리 사용하는데, 이런 패턴의 생성을 위해 최적화된 LFSR 구조이외에 별도의 하드웨어가 거의 필요없다는 장점이 있는 반면, 고장 검출율(fault coverage)을 원하는 만큼 끌어올릴지 보장할 수 없다는 단점이 있다. 대다수의 큰 회로는 의사무작위 패턴 생성으로 100%의 고장 검출율을 얻지 못하는데, 의사무작위 패턴으로 검출하지 못하는 고장을 검출난해 고장(hard-to-detect fault)이라 한다. 기존의 의사무작위 패턴 생성 방법은 단일 스캔체인을 사용한다고 가정할 경우, LFSR로 패턴을 생성해서 그 중 하나의 값을 계속해서 스캔체인으로 보내는 형태이다. 따라서, LFSR의 stage 수가 n이라 할 때, 스캔체인의 길이에 상관없이  $2^n-1$ 개 만큼의 패턴을 생성할 수 있다.

이를 위한 부가적인 하드웨어로는 일단, 도1에 나타낸 것과 같이 비트카운터(bit counter)를 들 수 있다. 이것은 스캔체인의 길이에 의해 결정되는데, 그 길이가 m이라 하면,  $\log_2 m$  만큼의 길이를 갖는 비트카운터를 사용한다. 비트카운터는 스캔별 테스트(test per scan)의 경우 스캔체인에 시프트 과정이 끝나고 테스트 대상 회로에 패턴을 가하는 시점을 알려주는역할을 한다. 따라서, 필수적인 구성요소이며, LFSR과 함께 스캔별 테스트 방법에서 의사무작위 패턴 생성을 위한 기본 요소라고 할 수 있다.

이외에 사용되는 구성요소로서, 의사무작위 테스트가 끝나는 시점을 알려주고 결정패턴 생성시 컨트롤을 위해 필요한 것이 패턴카운터(pattern counter)인데, 비트카운터에 비하면 인덱스의 역할을 한다고 할 수 있다. 즉, 스캔체인(주사사슬)에 한번 값이 다 채워져서 테스트 대상 회로에 패턴이 가해질 때마다 값이 하나씩 커지는 형태의 카우터이다.

상술한 바와 같이, 비트카운터와 패턴카운터는 내장형 자체 테스트를 실시함에 있어 필수적인 구성요소라 할 수 있다. 여기서, 의사무작위 패턴 생성시 스캔체인의 컨트롤만 하는 비트카운터와 결정패턴 테스트에서의 비트 플립핑을 위한 컨트롤 정도의 역할만 하는 패턴카운터는 그 크기에 비해 의사무작위 패턴 생성시 별 역할을 하지 못하므로, 이를 의사무작위 테스트에서도 충분히 활용하여 그 효율성을 높일 필요가 있다.

#### 발명이 이루고자 하는 기술적 과제

최근 들어, 경쟁적으로 개발되고 있는 시스템온칩은 초고집적 회로 제작 기술을 이용하여, 최소의 비용을 들여 희망하는 스펙을 최단 시간안에 높은 신뢰도를 갖는 VLSI 칩으로 구현하는 것을 목표로 한다. 그런데, 테스트단계는 전체 칩 제조 프로세스에서 비용의 문제, 제작 시간의 문제, 그리고 신뢰도의 문제에서 병목 현상으로 작용하고 있다. 때문에 효과적인 테스트 기술의 개발은 경제적, 상업적으로 매우 중요하다. 테스트 기술의 성능을 평가하는 기준으로서는 고장 검출율, 테스트 시간, 하드웨어 오버헤드 등을 들 수 있다. 본 발명의 기술은 기존의 테스트 기술에 비해 적은 테스트 시간동안, 최소의 하드웨어 오버헤드만으로 동등한 고장 검출율을 얻을 수 있을 것으로 기대되기 때문에, 반도체 생산 비용을 효과적으로 감축할 수 있다.

따라서 본 발명의 목적은 결정패턴 생성 전에도 두 하드웨어가 많은 역할을 수행하도록 하여, 기존의 의사무작위 패턴 생성에 필요한 하드웨어를 줄이면서도, 전혀 테스트 시간이 증가되지 않도록 하는 방법을 제공함을 목적으로 한다.

#### 발명의 구성 및 작용

도2에서 보이는 구조에서는, 5비트의 LFSR이 32비트 패턴카운터/비트카운터의 총 32비트중 한 비트를 제외한 31비트중 한 비트만 스캔체인(주사사슬)으로 보낼 수 있도록 패턴을 생성한다. 32비트 모두가 아닌 31비트만이 멀티플렉서로 들어 가는 이유는 5비트의 LFSR이 생성할 수 있는 패턴의 가지 수가 모두 0인 패턴(혹은 모두 1인 패턴)을 제외한  $(2^5-1)$  가지 이기 때문이다.

도2에서 패턴카운터와 비트카운터는 각각 일반카운터 혹은 LFSR 형태로 구성할 수 있는데, 여기서 비트카운터는 일반카운터의 형태를 유지하기로 한다. 패턴카운터의 경우는 비트카운터와 함께 일반카운터를 쓰는 경우 LFSR의 형태로 쓰는 경우보다 의사무작위 테스트에서 고장검출율이 조금 낮아서 LFSR의 형태로 사용했고, XOR 게이트가 각 단의 외부에 있는 타입의 LFSR이 아닌 XOR 게이트가 내부에 있는 타입의 LFSR의 형태를 사용하였다. 5비트의 LFSR에서 패턴카운터와 비트카운터의 값을 선택할 때, 0 또는 1의 값중 한 쪽의 값이 너무 많고 적을 경우, LFSR에서 선택하는 값이 0 또는 1쪽으로 몰릴 것이고, 그러한 패턴의 특성이 전체 고장 검출율을 빠른 시간 안에 올리는데 제한이 될 것이기 때문에, 한 클릭 주기에 0 또는 1의 수가 하나씩만 달라지는 타입의 LFSR을 쓰기보다는 그 수가 여러개씩 바뀔 수 있는 타입의 LFSR을 사용하는 것이다.

이 구조가 기존의 구조보다 보다 적은 수의 비트를 사용하고도 같은 수준 혹은 그 이상의 고장 검출율을 유지할 수 있는 것은 결정패턴 테스트 이전에 의사무작위 패턴 테스트를 하는 동안의 패턴카운터와 비트카운터의 역할을 증대시켰기 때문이다.

패턴카운터에 패턴 생성의 역할을 맡겼지만, 패턴카운터는 결정패턴 테스트를 할 때, 컨트롤러의 역할도 수행할 수 있어야하기 때문에, 결정패턴을 생성할 때, 패턴카운터의 값을 직접 바꾸는 방법은 사용하지 않는 것이 좋고, 이러한 것은 기존의 구조도 마찬가지 이므로, 새로운 구조에서 별다른 제한이 가해지는 것도 아니라고 할 수 있다.

도1과 도2에서 패턴카운터와 비트카운터의 총 비트 수를 같게 놓으면 도2의 LFSR 길이가 더 짧다. 도2에서의 LFSR 길이를 L이라 하면, 도1에 보이는 기존의 구조는 LFSR이  $2^L$ 의 길이를 가지므로  $2^L$ =m이라 하면,  $2^m$ -1의 패턴 생성 길이를 갖고, 도2에 보이는 구조는  $(m-1)\times(2^m-1)$ 의 패턴 생성 길이를 갖는다. 따라서, 이론적으로도 도2의 구조가 도1보다 의사무 작위 패턴 테스트에서 고장 검출율이 낮지 않게 나오는 것을 보여준다.

이를 위한 간단한 예는 다음의 도3과 같다. 도3과 표1에서 보이는 패턴 생성기는 간단한 예로서, 외부 XOR 타입의 2비트 LFSR, 패턴카운터로서 내부 XOR 타입의 2비트 LFSR, 비트카운터로서 2비트의카운터를 이용하고, 스캔체인의 길이가 4인 경우이다. 실제의 경우에는 스캔체인의 길이를 h라 했을 때, 비트카운터가  $\log_2 h$  비트만큼의 길이로서 스캔체인보다는 훨씬 짧은 길이가 되는데, 여기서의 간단한 예는, 패턴카운터와 비트카운터의 총 비트 수와 스캔체인의 길이가 같게 구성되어서, 실제처럼 스캔체인에서 다양한 패턴이 생성되지 않을 수도 있다. 표1에서 보여주는 패턴의 생성 주기는 시작 벡터  $(a_1a_0c_1c_0[2비트카운터])=011100로부터 그것이 다시 반복되는 간격인 <math>(4-1)(2^4-1)=45$ 이다.

[丑1]

| a <sub>1</sub> |   | a <sub>0</sub> |   | c <sub>1</sub> |   | $c_0$ |   |   |   |

|----------------|---|----------------|---|----------------|---|-------|---|---|---|

| 0              | 1 | 1              | 1 | 0              | 0 | Х     | Х | Х | Х |

| 1              | 0 | 1              | 0 | 0              | 1 | 1     | Х | Х | Х |

| 1              | 1 | 0              | 1 | 1              | 0 | 0     | 1 | Х | X |

| 0              | 1 | 1              | 1 | 1              | 1 | 0     | 0 | 1 | X |

| 1              | 0 | 1              | 0 | 0              | 0 | 1     | 0 | 0 | 1 |

| 1              | 1 | 0              | 1 | 0              | 1 | 0     | 1 | 0 | 0 |

| 0              | 1 | 1              | 1 | 1              | 0 | 1     | 0 | 1 | 0 |

| 1              | 0 | 1              | 0 | 1              | 1 | 1     | 1 | 0 | 1 |

| 1              | 1 | 0              | 1 | 0              | 0 | 1     | 1 | 1 | 0 |

| 0              | 1 | 1              | 1 | 0              | 1 | 0     | 1 | 1 | 1 |

| 1              | 0 | 1              | 0 | 1              | 0 | 1     | 0 | 1 | 1 |

|                | • |                |   | •              | • | •     | • | • |   |

|                |   |                |   | •              |   |       | • | • |   |

|                |   |                |   |                |   |       |   |   |   |

|  | • | • | • | • |  |  |

|--|---|---|---|---|--|--|

|  |   |   |   |   |  |  |

|  |   |   |   |   |  |  |

|  |   |   |   |   |  |  |

이하의 설명은, 몇 개의 벤치마크 회로를 이용하여 본 발명에서 제안하는 패턴 생성 방법을 검증하기 위해 실험한 결과에 관한 것이다.

아래의 표2를 보면 4개의 섹션으로 나뉘어 있는데, 첫 번째와 두 번째 섹션은 대조구로서, 첫 번째 섹션은 기존의 32비트 LFSR을 사용한 결과이고, 두 번째 섹션은 세 번째, 네 번째와 동일한 하드웨어를 소모하는 크기의 패턴 생성기를 사용한 결과이다. 세 번째 섹션은 비트카운터를 LFSR 형태로 구현한 것이고, 네 번째 섹션은 비트카운터를카운터 형태로 구현한 것이며, 세 번째 네 번째 모두 5비트 LFSR을 사용한 결과이다.

#### [丑2]

| 32비트 LFSR (기존) 12비트 LFSR (기존) 5비트 LFSR (LFSR) 5비트LFSR(카운터) |      |          |                |        |      |        |              |        |  |

|------------------------------------------------------------|------|----------|----------------|--------|------|--------|--------------|--------|--|

| l                                                          |      | FSR (기존) | 12비트 LFSR (기존) |        |      | ,      | 5비트LFSR(카운터) |        |  |

| 회로                                                         | 남은   | 고장       | 남은             | 고장     | 남은   | 고장     | 남은           | 고장     |  |

|                                                            | 고장수  | 검출율      | 고장수            | 검출율    | 고장수  | 검출율    | 고장수          | 검출율    |  |

| s208                                                       | 5    | 97.67    | 5              | 97.67  | 4    | 98.14  | 3            | 98.60  |  |

| s344                                                       | 0    | 100.00   | 0              | 100.00 | 0    | 100.00 | 0            | 100.00 |  |

| s349                                                       | 2    | 99.43    | 2              | 99.43  | 2    | 99.43  | 2            | 99.43  |  |

| s382                                                       | 0    | 100.00   | 0              | 100.00 | 0    | 100.00 | 0            | 100.00 |  |

| s386                                                       | 1    | 99.74    | 36             | 90.62  | 2    | 99.48  | 12           | 96.88  |  |

| s400                                                       | 6    | 98.58    | 6              | 98.58  | 6    | 98.58  | 6            | 98.58  |  |

| s420                                                       | 44   | 89.77    | 67             | 84.42  | 33   | 92.33  | 35           | 91.86  |  |

| s444                                                       | 14   | 97.05    | 14             | 97.05  | 14   | 97.05  | 14           | 97.05  |  |

| s510                                                       | 0    | 100.00   | 0              | 100.00 | 0    | 100.00 | 0            | 100.00 |  |

| s526                                                       | 16   | 97.12    | 13             | 97.66  | 15   | 97.30  | 18           | 96.76  |  |

| s641                                                       | 12   | 97.43    | 19             | 95.93  | 22   | 95.29  | 20           | 95.72  |  |

| s1196                                                      | 57   | 95.41    | 52             | 95.81  | 72   | 94.20  | 51           | 95.89  |  |

| s1238                                                      | 134  | 90.11    | 126            | 90.70  | 132  | 90.26  | 129          | 90.48  |  |

| s1423                                                      | 50   | 96.70    | 162            | 89.31  | 26   | 98.28  | 26           | 98.28  |  |

| s1488                                                      | 14   | 99.06    | 28             | 98.12  | 27   | 98.18  | 24           | 98.38  |  |

| s1494                                                      | 26   | 98.27    | 41             | 97.28  | 33   | 97.81  | 36           | 97.61  |  |

| s5378                                                      | 158  | 96.57    | 146            | 96.83  | 131  | 97.15  | 134          | 97.09  |  |

| s13207                                                     | 857  | 91.27    | 2562           | 73.90  | 444  | 95.48  | 602          | 93.87  |  |

| s15850                                                     | 1025 | 91.26    | 1958           | 83.30  | 1034 | 91.18  | 1121         | 90.44  |  |

| s38417                                                     | 2156 | 93.09    | 4526           | 85.48  | 2424 | 92.23  | 2043         | 93.45  |  |

| s38584                                                     | 2028 | 94.41    | 2613           | 92.80  | 1946 | 94.64  | 1922         | 94.71  |  |

각각의 섹션은 검출고장수와 고장 검출율로 이루어져 있는데, 이는 각각 모든 고장 중 검출된 고장의 수와 의사무작위 테스트의 고장 검출율을 나타낸다. 표2에서도 알 수 있듯이, 5비트의 LFSR을 사용한 것이 고장검출율이 평균적으로 비슷하거나 약간 우위에 있는 것을 알 수 있다. 또한, 12비트 LFSR을 사용한 기존 방법의 경우, 큰 회로에 대해서는 고장 검출율이 현저하게 떨어지는 것을 볼 수 있다. 따라서, 5비트의 LFSR을 사용한 새로운 구조는 훨씬 큰 하드웨어를 사용하는 기존의 방법에 비해 하드웨어를 덜 쓰면서도, 의사무작위 패턴 테스트에서 비슷하거나 더 높은 고장 검출율을 보인다는 것을 알 수 있다. 의사무작위 테스트라는 것은 이론적으로는 이미 성능면에서 최적화되어 있는 LFSR을 사용하는 것이 좋지만, 이를 위한 부가적인 하드웨어가 있으므로, 그 하드웨어도 패턴 생성에 이용함으로써 더 작은 하드웨어를 사용하고도 같은 성능의 패턴 생성을 할 수 있게 되었다.

[班3]

|        | 32   | 2비트 LFSR | (기존)     | 5    | 5비트 LFSR ( | LFSR)    | 5비트LFSR(카운터) |        |          |  |

|--------|------|----------|----------|------|------------|----------|--------------|--------|----------|--|

| 회로     | 남은   | 고장       | 총패턴수     | 암    | 고장         | 총패턴수     | 암            | 고장     | 총패턴수     |  |

|        | 고장수  | 검출율      |          | 고장수  | 검출율        |          | 고장수          | 검출율    |          |  |

| s208   | 5    | 97.67    | 24320    | 4    | 98.14      | 29792    | 3            | 98.60  | 21888    |  |

| s344   | 0    | 100.00   | 6144     | 0    | 100.00     | 8448     | 0            | 100.00 | 3072     |  |

| s349   | 2    | 99.43    | 26112    | 2    | 99.43      | 26880    | 2            | 99.43  | 26880    |  |

| s382   | 0    | 100.00   | 10752    | 0    | 100.00     | 10752    | 0            | 100.00 | 10752    |  |

| s386   | 1    | 99.74    | 42848    | 2    | 99.48      | 20384    | 12           | 96.88  | 20800    |  |

| s400   | 6    | 98.58    | 30720    | 6    | 98.58      | 28416    | 6            | 98.58  | 26880    |  |

| s420   | 44   | 89.77    | 77280    | 33   | 92.33      | 43680    | 35           | 91.86  | 84000    |  |

| s444   | 14   | 97.05    | 37632    | 14   | 97.05      | 33024    | 14           | 97.05  | 28416    |  |

| s510   | 0    | 100.00   | 16800    | 0    | 100.00     | 19200    | 0            | 100.00 | 17600    |  |

| s526   | 16   | 97.12    | 39936    | 15   | 97.30      | 36864    | 18           | 96.76  | 34560    |  |

| s641   | 12   | 97.43    | 86400    | 22   | 95.29      | 74304    | 20           | 95.72  | 69120    |  |

| s1196  | 57   | 95.41    | 98304    | 72   | 94.20      | 89088    | 51           | 95.89  | 94208    |  |

| s1238  | 134  | 90.11    | 98304    | 132  | 90.26      | 125952   | 129          | 90.48  | 97280    |  |

| s1423  | 50   | 96.70    | 131040   | 26   | 98.28      | 224224   | 26           | 98.28  | 206752   |  |

| s1488  | 14   | 99.06    | 30016    | 27   | 98.18      | 26880    | 24           | 98.38  | 26432    |  |

| s1494  | 26   | 98.27    | 30016    | 33   | 97.81      | 27776    | 36           | 97.61  | 26432    |  |

| s5378  | 158  | 96.57    | 540992   | 131  | 97.15      | 979264   | 134          | 97.09  | 862848   |  |

| s13207 | 857  | 91.27    | 6496000  | 444  | 95.48      | 10841600 | 602          | 93.87  | 8220800  |  |

| s15850 | 1025 | 91.26    | 5474560  | 1034 | 91.18      | 3284736  | 1121         | 90.44  | 2502656  |  |

| s38417 | 2156 | 93.09    | 19701760 | 2424 | 92.23      | 28434432 | 2043         | 93.45  | 21512192 |  |

| s38584 | 2028 | 94.41    | 13773312 | 1946 | 94.64      | 18270720 | 1922         | 94.71  | 14241792 |  |

표3은 작은 크기의 LFSR로 테스트하는데 걸린 CPU time을 나타낸 것이다. 표3은 고장 검출율 외에 또 다른 성능평가 항목인 테스트 시간을 검증한 것으로 기존의 방법에 비해 더 많은 패턴이 필요하지 않음을 알 수 있으므로, 새로운 구조의 효율성을 입증하고 있다. 표3에서는 표2에 있는 기존의 방법의 12비트 LFSR을 제외하였는데, 이는 이미 표2에서 본 발명의 방법이 기존의 12비트 LFSR을 사용한 방법보다 우수함을 보였으므로, 표3에서는 그보다 훨씬 큰 하드웨어를 사용하는 기존 방법의 32비트 LFSR과 새로 제안하는 구조의 고장검출율을 구하는데까지의 가한 패턴 수를 비교하여, 본 발명의 방법에서 생성되는 패턴의 무작위성을 보이려 한 것이다.

## 발명의 효과

본 발명에 따르면 기존의 테스트 기술에 비해 적은 테스트 시간동안, 최소의 하드웨어 오버헤드 만으로 동등한 고장 검출율을 획득할 수 있을 것으로 기대되기 때문에, 반도체 생산 비용을 효과적으로 감축할 수 있다.

#### (57) 청구의 범위

# 청구항 1.

스캔체인을 이용하여 CUT를 테스트하는 내장형 자체테스트 방법으로서,

테스트패턴을 생성해서 스캐체인으로 보내는 LFSR과, 스캔체인에 시프트 과정이 끝나고 테스트 대상 회로에 패턴을 가하는 시점을 알려주는 비트카운터와, 패턴을 생성하고 의사무작위 테스트가 끝나는 시점을 알려주는 패턴카운터를 포함하며,

상기 LFSR은 N비트의 패턴카운터 및 비트카운터의 N비트중 한 비트를 제외한 (N-1)비트중 한 비트만 스캔체인으로 보내는 것을 특징으로 하는, 내장형 자체테스트 패턴 생성시의 하드웨어 오버헤드 축소방법.

# 청구항 2.

제1항에 있어서, 상기 LFSR이 N비트의 패턴카운터 및 비트카운터의 N비트중 한 비트를 제외한 (N-1)비트중 한 비트만 스캔체인으로 보내는 것은 멀티플렉서를 이용하여 수행되는 것을 특징으로 하는, 내장형 자체테스트 패턴 생성시의 하드 웨어 오버헤드 축소방법.

#### 청구항 3.

제1항에 있어서, 상기 패턴카운터와 비트카운터는 각각 일반 카운터 형태인 것을 특징으로 하는, 내장형 자체테스트 패턴 생성시의 하드웨어 오버헤드 축소방법.

## 청구항 4.

제1항에 있어서, 상기 패턴카운터와 비트카운터는 각각 LFSR 형태인 것을 특징으로 하는, 내장형 자체테스트 패턴 생성시의 하드웨어 오버헤드 축소방법.

# 청구항 5.

제4항에 있어서, 상기 패턴카운터는 XOR 게이트가 내부에 포함되어 있는 LFSR인 것을 특징으로 하는, 내장형 자체테스트 패턴 생성시의 하드웨어 오버헤드 축소방법.

#### 청구항 6.

스캔체인을 이용하여 CUT를 테스트하는 내장형 자체테스트 방법으로서,

테스트패턴을 생성해서 스캐체인으로 보내는 LFSR과,

스캔체인에 시프트 과정이 끝나고 테스트 대상 회로에 패턴을 가하는 시점을 알려주는 비트카운터와,

패턴을 생성하고 의사무작위 테스트가 끝나는 시점을 알려주는 패턴카운터를 포함하되.

상기 LFSR은 N비트의 패턴카운터 및 비트카운터의 N비트중 한 비트를 제외한 (N-1)비트중 한 비트만 스캔체인으로 보내는 것을 특징으로 하는, 내장형 자체테스트 패턴 생성시의 하드웨어 오버헤드 축소장치.

# 청구항 7.

제6항에 있어서, 상기 LFSR이 N비트의 패턴카운터 및 비트카운터의 N비트중 한 비트를 제외한 (N-1)비트중 한 비트만 스캔체인으로 보내기 위한 멀티플렉서가 추가로 포함되는 것을 특징으로 하는, 내장형 자체테스트 패턴 생성시의 하드웨어 오버헤드 축소장치.

# 청구항 8.

제6항에 있어서, 상기 패턴카운터와 비트카운터는 각각 일반 카운터 형태인 것을 특징으로 하는, 내장형 자체테스트 패턴 생성시의 하드웨어 오버헤드 축소장치.

# 청구항 9.

제6항에 있어서, 상기 패턴카운터와 비트카운터는 각각 LFSR 형태인 것을 특징으로 하는, 내장형 자체테스트 패턴 생성시의 하드웨어 오버헤드 축소장치.

# 청구항 10.

제9항에 있어서, 상기 패턴카운터는 XOR 게이트가 내부에 포함되어 있는 LFSR인 것을 특징으로 하는, 내장형 자체테스트 패턴 생성시의 하드웨어 오버헤드 축소장치.

# 도면

# 도면3