# (19) 대한민국특허청(KR)(12) 공개특허공보(A)

(51) Int. Cl.

**G06F 12/10** (2006.01) **G06F 12/06** (2006.01) **G06F 12/00** (2006.01)

(21) 출원번호 **10-2010-0006976(분할**)

(22) 출원일자 2010년01월26일

심사청구일자 없음

(62) 원출원 특허 10-2008-0046258

원출원일자 2008년05월19일 심사청구일자 2008년05월19일 (11) 공개번호 10-2010-0018017

(43) 공개일자 2010년02월16일

(71) 출원인

연세대학교 산학협력단

서울 서대문구 신촌동 134 연세대학교

(72) 발명자

김신덕

서울시 서초구 반포동 65-1 궁전아파트 1동 604호

박정욱

서울시 강남구 도곡동 래미안아파트 108동 1803호

박승호

서울시 영등포구 여의도동 삼부아파트 2동 85호

(74) 대리인

특허법인무한

전체 청구항 수 : 총 4 항

#### (54) 비휘발성 메모리에 기반한 컴퓨터 시스템

#### (57) 요 약

본 발명은 컴퓨터 시스템에 관한 것으로, 더욱 상세하게는 메모리 또는 저장 장치를 통합하여 운용하는 컴퓨터 시스템에 관한 것이다.

본 발명에 따르면 중앙 처리 장치, 데이터를 저장하는 비휘발성 메모리부를 포함하는 메모리 장치, 외부 데이터를 수신하는 입출력 장치, 제1 메모리 채널, 제2 메모리 채널 및 상기 수신된 외부 데이터를 상기 제2 메모리 채널을 경유하여 상기 메모리 장치에 저장하고, 상기 저장된 외부 데이터를 상기 제1 메모리 채널을 경유하여 상기 중앙 처리 장치로 전송하는 메모리 컨트롤러를 포함하는 것을 특징으로 하는 컴퓨터 시스템이 제공된다.

#### 대 표 도 - 도1

## 이 발명을 지원한 국가연구개발사업

과제고유번호 과C6A1607

부처명한국학술진흥재단연구사업명2단계 BK21 사업

연구과제명 지능형 모바일 서비스를 위한 차세대 단말 소프트웨어사업단

주관기관 연세대학교 산학협력단

연구기간 2007년 03월 01일 ~ 2008년 02월 29일

#### 특허청구의 범위

#### 청구항 1

실행중인 프로세스와 연관된 데이터 및 파일을 식별하는 중앙 처리 장치;상기 데이터 및 파일을 저장하는 메모리 장치;상기 데이터 및 파일의 주소값을 저장하는 가상 메모리 테이블; 및상기 주소값을 참조하여 상기 메모리 장치로부터 상기 데이터 및 파일을 상기 중앙 처리 장치로 전송하는 메모리 컨트롤러를 포함하는 것을 특징으로하는 컴퓨터 시스템

#### 청구항 2

제1항에 있어서,상기 파일은 실행 파일, 라이브러리 파일, 데이터 파일을 포함하는 것을 특징으로 하는 컴퓨터 시스템.

#### 청구항 3

제1항에 있어서,상기 중앙 처리 장치는 상기 데이터 또는 파일에 기반하여 연산 결과를 산출하고, 상기 연산 결과와 관련된 연산 주소값을 생성하고,상기 가상 메모리 테이블은 상기 연산 주소값을 저장하고,상기 메모리 컨트롤러는 상기 연산 주소값을 참조하여 상기 연산 결과를 상기 메모리 장치에 저장하는 것을 특징으로 하는 컴퓨터 시스템.

#### 청구항 4

제1항에 있어서, 상기 가상 메모리 테이블은,상기 파일의 주소값을 저장하는 파일 할당 테이블 및 상기 데이터의 주소를 저장하는 페이지 테이블을 포함하는 것을 특징으로 하는 컴퓨터 시스템.

#### 명세서

#### 기술분야

[0001] 본 발명은 컴퓨터 시스템에 관한 것으로, 더욱 상세하게는 메모리 또는 저장 장치를 통합하여 운용하는 컴퓨터 시스템에 관한 것이다.

#### 배경기술

- [0002] 종래의 컴퓨터 시스템에서는 주 기억장치와 보조 기억장치가 분리된다. 주 기억장치는 DRAM등으로 구성된, 전원 공급이 중단되면 저장된 데이터가 사라지는 휘발성 저장장치이다. 보조 기억장치는 하드디스크 등으로 구성된, 전원공급이 중단되어도 저장된 데이터가 사라지지 않는 비휘발성 저장 장치이다. 종래의 컴퓨터 시스템에서는 하드 디스크 등의 보조 기억장치에 저장된 데이터를 사용하기 위하여 먼저 데이터를 DRAM등으로 구성된 주 기억 장치(Main Memory)에 복사한다. 중앙 처리 장치는 주 기억장치에 복사된 데이터를 읽고, 데이터에 대한 소정의 연산을 수행한다. 중앙 처리 장치의 연산 결과는 다시 주 기억장치에 저장되고, 주 기억장치에 저장된 데이터는 다시 보조 기억장치에 저장된다.

- [0003] 보조 기억장치의 용량은 주 기억장치의 용량보다 매우 큰 것이 일반적이다. 중앙 처리 장치가 보조 기억 장치에 저장된 데이터에 접근하고, 주기억 장치보다 큰 메모리 영역을 이용하기 위하여 가상 메모리(virtual memory) 기법을 사용할 수 있다.

- [0004] 가상 메모리 기법에 따르면 주 기억 장치는 가상 메모리 테이블에 저장된 가상 메모리를 참조하여 필요한 데이터에 대한 가상 메모리 값을 생성한다. 컴퓨터 시스템은 페이지 스와핑(page swapping) 과정을 통하여 가상 메모리 값을 실제 물리 주소 값으로 변환한다. 컴퓨터 시스템은 실제 물리 주소 값에 기반하여 주 기억장치에 복사된 데이터를 읽을 수 있다.

- [0005] 종래 기술에 따르면 보조 기억 장치의 저장 공간은 파일 시스템을 이용하여 관리되고, 파일 할당 테이블과 페이지 테이블은 서로 다른 영역에서 관리된다. 가상 메모리를 위한 스왑 공간은 파일 시스템 내의 파일의 형태로 존재한다. 따라서 중앙 처리 장치가 보조 기억 장치의 메모리 페이지에 접근하기 위해서는 먼저 페이지 테이블을 참조한 후 다시 파일 할당 테이블을 참조하여야만 했다.

#### 발명의 내용

#### 해결하려는 과제

- [0006] 본 발명의 목적은 컴퓨터 시스템의 동작 속도를 향상시키는 것이다.

- [0007] 본 발명의 목적은 컴퓨터 시스템의 저장 계층 구조를 통합하는 것이다.

#### 과제의 해결 수단

- [0008] 상기의 목적을 이루고 종래기술의 문제점을 해결하기 위하여, 본 발명은 중앙 처리 장치, 데이터를 저장하는 비휘발성 메모리부를 포함하는 메모리 장치, 외부 데이터를 수신하는 입출력 장치, 제1 메모리 채널, 제2 메모리 채널 및 상기 수신된 외부 데이터를 상기 제2 메모리 채널을 경유하여 상기 메모리 장치에 저장하고, 상기 저장된 외부 데이터를 상기 제1 메모리 채널을 경유하여 상기 중앙 처리 장치로 전송하는 메모리 컨트롤러를 포함하는 것을 특징으로 하는 컴퓨터 시스템을 제공한다.

- [0009] 본 발명의 일측에 따르면 프로세스를 수행하는 중앙 처리 장치, 비휘발성 메모리부를 포함하는 메모리 장치, 메모리 채널 및 상기 메모리 채널을 경유하여 상기 메모리 장치에 저장된 데이터를 상기 중앙 처리 장치로 전송하는 메모리 컨트롤러를 포함하고, 상기 메모리 컨트롤러는 상기 프로세스의 수행 레지스터의 값을 상기 비휘발성 메모리부에 저장하고, 상기 중앙 처리 장치는 상기 프로세스의 수행을 중지하는 것을 특징으로 하는 컴퓨터 시스템이 제공된다.

- [0010] 본 발명의 또 다른 일측에 따르면, 가상 메모리 테이블을 포함하는 중앙 처리 장치, 데이터를 저장하는 적어도 하나 이상의 파일 및 상기 파일들의 주소값을 저장하는 파일 주소 테이블을 저장하는 메모리 장치 및 상기 저장된 데이터를 상기 중앙 처리 장치로 전송하는 메모리 컨트롤러를 포함하는 것을 특징으로 하는 컴퓨터 시스템이 제공된다.

#### 발명의 효과

- [0011] 본 발명에 따르면 컴퓨터 시스템의 동작 속도를 향상시킬 수 있다.

- [0012] 본 발명에 따르면 메모리 및 기억장치에 대한 중복 접근을 제거하여 컴퓨터 시스템의 성능을 향상시킬 수 있다.

#### 도면의 간단한 설명

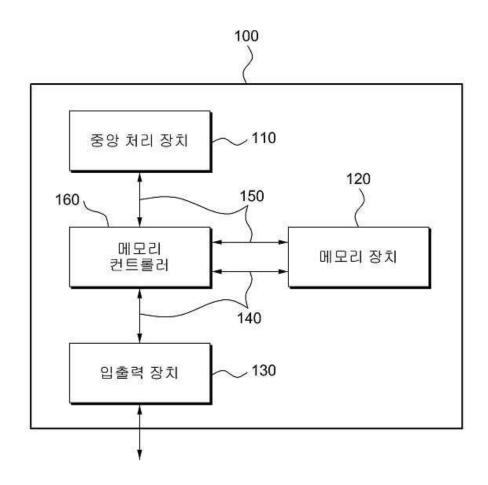

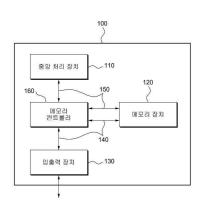

[0013] 도 1은 본 발명의 일 실시예에 따라서 입출력 장치를 경유하여 수신된 데이터를 메모리 장치에 저장하고, 저장 된 데이터를 다시 중앙 처리 장치로 전송하는 컴퓨터 시스템의 구조를 도시한 블록도이다.

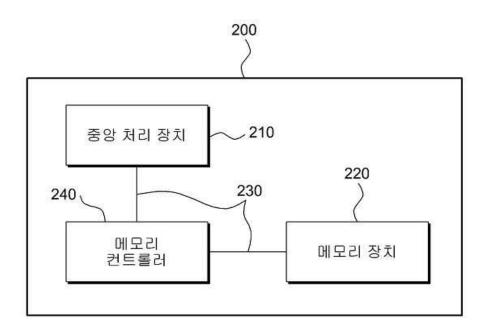

> 도 2는 본 발명의 일 실시예에 따라서 중앙 처리 장치가 수행하는 레지스터의 값을 비 휘발성 메모리 장치에 전 송하는 컴퓨터 시스템의 구조를 도시한 블록도이다.

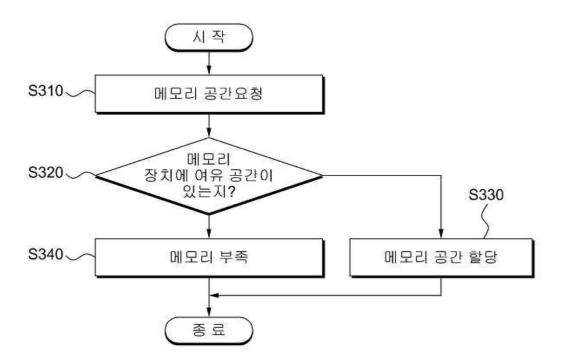

> 도 3은 본 발명의 일 실시예에 따라서 메모리를 할당하는 컴퓨터 시스템의 동작을 단계별로 도시한 순서도이다.

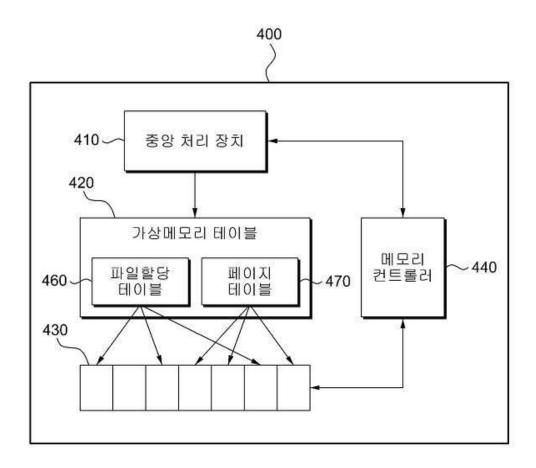

도 4는 본 발명의 일 실시예에 따라서 메모리에 저장된 데이터를 읽는 컴퓨터 시스템의 동작을 단계별로 도시한 순서도이다.

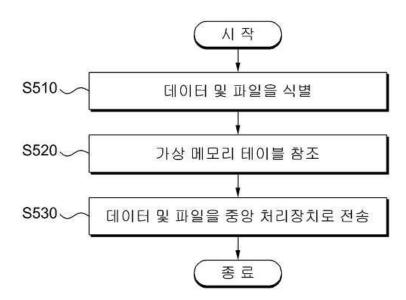

도 5는 본 발명의 일 실시예에 따라서 가상 메모리 테이블을 참조하여 메모리 장치에 저장된 데이터를 읽는 방법을 단계별로 도시한 순서도이다.

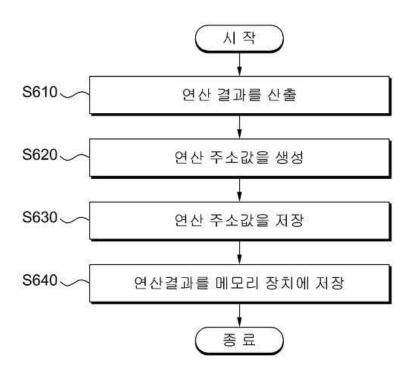

도 6은 본 발명의 일 실시예에 따라서 가상 메모리 테이블을 참조하여 중앙 처리 장치의 연산 결과를 메모리 장치에 저장하는 방법을 단계별로 도시한 순서도이다.

도 7은 본 발명의 일 실시예에 따라서 메모리 장치에 저장된 프로그램 파일을 실행하는 방법을 단계별로 도시한 순서도이다.

도 8은 본 발명의 일 실시예에 따라서 메모리 장치에 저장된 데이터 파일을 사용하는 방법을 단계별로 도시한 순서도이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0014] 이하에서는 첨부된 도면을 참조하여 본 발명의 실시예를 상세히 설명한다.

- [0015] 도 1은 본 발명의 일 실시예에 따라서 입출력 장치를 경유하여 수신된 데이터를 메모리 장치에 저장하고, 저장된 데이터를 다시 중앙 처리 장치로 전송하는 컴퓨터 시스템의 구조를 도시한 블록도이다. 이하 도 1을 참조하여 본 발며에 따른 컴퓨터 시스템의 구조를 상세히 설명하기로 한다. 본 발명에 따른 컴퓨터 시스템(100)은 중앙 처리 장치(110), 메모리 장치(120), 입출력 장치(130), 제1 메모리 채널(150), 제2 메모리 채널(140) 및 메모리 컨트롤러(160)를 포함한다.

- [0016] 중앙 처리 장치(110)는 컴퓨터 시스템(100)에 입력되는 데이터를 처리하거나 입력되는 데이터에 대한 소정의 연산을 수행한다.

- [0017] 메모리 장치(120)는 중앙 처리 장치(110)의 연산 결과를 저장하거나, 입출력 장치(130)를 통하여 수신된 데이터를 저장하다.

- [0018] 입출력 장치(130)는 컴퓨터 시스템(100)의 외부로 데이터를 전송하거나, 외부로부터 데이터를 수신한다. 본 발명의 일 실시예에 따르면 입출력 장치는 IEEE 1394 제어 장치, USB 제어 장치, IDE 제어 장치, SATA 제어 장치 및 영상 출력 장치 중에서 적어도 하나 이상을 포함할 수 있다.

- [0019] 제1 메모리 채널(150)은 메모리 장치(120)와 중앙 처리 장치(110)를 연결한다. 본 발명의 일 실시예에 따르면 메모리 장치(120)에 저장된 데이터는 제1 메모리 채널(150)을 경유하여 중앙 처리 장치(110)로 전송될 수 있다. 본 발명의 다른 실시예에 따르면 중앙 처리 장치(110)의 연산 결과는 제1 메모리 채널(150)을 경유하여 메모리 장치(120)에 저장될 수 있다.

- [0020] 제2 메모리 채널(140)은 입출력 장치(130)와 메모리 장치(120)를 연결한다. 본 발명의 일 실시예에 따르면 메모리 장치(120)에 저장된 데이터는 제2 메모리 채널(140)을 경유하여 입출력 장치(130)로 전송될 수 있다. 입출력 장치(130)로 전송된 데이터는 컴퓨터 시스템(100)의 외부로 전송될 수 있다.

- [0021] 본 발명의 다른 실시예에 따르면 입출력 장치(130)를 경유하여 컴퓨터 시스템(100)의 외부로부터 수신된 데이터는 제2 메모리 채널(140)을 경유하여 메모리 장치(120)로 전송될 수 있다.

- [0022] 메모리 컨트롤러(160)는 입출력 장치(130)가 수신한 외부 데이터를 제2 메모리 채널(140)을 경유하여 메모리 장치(120)에 저장한다. 또한, 메모리 장치(120)에 저장된 데이터를 제1 메모리 채널(150)을 경유하여 중앙 처리 장치(110)로 전송한다.

- [0023] 본 발명의 일 실시예에 따르면 메모리 컨트롤러(160)는 직접 메모리 접근(DMA : Direct Memory Access)방법에 따라서 입출력 장치(130)가 수신한 외부 데이터를 메모리 장치(120)에 저장할 수 있다.

- [0024] 직접 메모리 접근 방법은 컴퓨터 시스템(100)내의 임의의 서브 시스템이 중앙 처리 장치(110)와 독립적으로 메모리에 직접 접근하여 메모리에 저장된 데이터를 직접 읽거나 직접 메모리에 데이터를 저장하는 방법이다. 직접 메모리 접근 방식을 사용하면 데이터가 중앙 처리 장치(110)를 경유하지 않고 메모리 장치(120)에 저장된다. 중앙 처리 장치(110)의 부하가 줄어들고, 컴퓨터 시스템(100)의 성능이 높아진다.

- [0025] 본 발명의 일 실시예에 따르면 메모리 장치(120)는 휘발성 메모리부를 더 포함하고, 메모리 컨트롤러(120)는 메모리 장치(120)에 포함된 휘발성 메모리부에 외부 데이터를 저장할 수 있다. 일반적으로 플래시 메모리와 같은 비휘발성 메모리는 DRAM(Dynamic RAM)과 같은 휘발성 메모리에 비하여 동작 속도가 느리다. 메모리 장치(120)가 휘발성 메모리부를 더 포함하고, 메모리 컨트롤러(120)가 메모리 장치(120)에 포함된 비휘발성 메모리에 데이터를 저장하면, 데이터 저장 속도를 향상시킬 수 있다.

- [0026] 본 발명에 따른 컴퓨터 시스템(100)의 메모리 장치(120)는 비휘발성 메모리부를 포함하므로 주 기억장치와 보조 기억장치를 구별하지 않는다. 따라서 보조 기억 장치에 저장된 데이터에 접근하기 위하여 가상 메모리를 물리 주소로 변환할 필요가 없고, 메모리 장치(120)만큼의 물리 주소 공간이 확보된다. 물리 메모리가 부족하여 발생하는 가상 주소와 물리 주소간의 변환, 즉 페이지 스와핑(page swapping)이 발생하지 않으므로, 본 발명에 따른 컴퓨터 시스템은 메모리 장치(120)에 저장된 데이터를 더욱 빨리 데이터를 읽을 수 있다.

- [0027] 본 발명에 따른 컴퓨터 시스템(100)에서는 주 기억장치와 보조 기억장치간의 구분이 없으므로, 중앙 처리 장치 (110)는 가상 주소와 물리 주소간의 변환없이 메모리 장치(120)에 저장된 모든 데이터에 직접 접근할 수 있다.

- [0028] 도 2는 본 발명의 일 실시예에 따라서 중앙 처리 장치가 수행하는 레지스터의 값을 비 휘발성 메모리 장치에 전송하는 컴퓨터 시스템의 구조를 도시한 블록도이다. 이하 도 2를 참조하여 본 발명에 따른 컴퓨터 시스템의 동

작을 상세히 설명하기로 한다. 본 발명에 따른 컴퓨터 시스템(200)은 중앙 처리 장치(210), 메모리 장치(220), 메모리 채널(230) 및 메모리 컨트롤러(240)를 포함한다.

- [0029] 중앙 처리 장치(210)는 프로세스를 수행한다. 중앙 처리 장치(210)가 수행하는 프로세스는 데이터에 대한 소정의 연산을 포함할 수 있다. 중앙 처리 장치(210)는 데이터에 대한 소정의 연산을 수행하여 연산 결과를 산출할수 있다. 중앙 처리 장치(210)는 소정의 연산을 수행하기 위한 데이터의 주소값, 연산과 관련된 명령어 (instruction)등을 중앙 처리 장치 내부의 레지스터(register)에 저장할 수 있다.

- [0030] 본 발명의 일 실시예에 따르면 중앙 처리 장치(210)가 수행하는 프로세스는 복수의 연산을 포함할 수 있다. 중앙 처리 장치(210)는 제1 연산을 수행하고, 제1 연산 수행 결과에 기반하여 제2 연산을 수행할 수 있다.

- [0031] 중앙 처리 장치(210)는 제1 연산을 수행하기 위한 데이터의 주소값, 연산과 관련된 명령어 등을 중앙 처리 장치 내부의 레지스터에 저장하고, 레지스터에 저장된 값들에 기반하여 제1 연산을 수행할 수 있다.

- [0032] 중앙 처리 장치는 제2 연산을 수행하기 위하여 레지스터에 저장된 제1 연산과 관련된 데이터의 주소값 및 명령어 등을 제거하고, 제2 연산과 관련된 데이터의 주소값 및 명령어를 레지스터에 저장할 수 있다. 중앙 처리 장치(210)가 수행하는 프로세스가 복수의 연산을 포함하는 경우에, 특정 연산과 관련된 레지스터의 값들은 특정 프로세스를 수행하기 위한 중앙 처리 장치(210)의 상태, 과정에 대한 정보를 포함한다.

- [0033] 메모리 장치(220)는 비휘발성 메모리부를 포함한다. 중앙 처리 장치(210)가 수행하는 프로세스와 관련된 데이터는 메모리 장치(220)에 저장된다.

- [0034] 메모리 채널(230)은 메모리 장치(220)와 중앙 처리 장치(210)를 연결한다.

- [0035] 메모리 컨트롤러(240)는 메모리 채널(230)을 경유하여 메모리 장치(220)에 저장된 데이터를 중앙 처리 장치(210)로 전송한다. 전송된 데이터는 중앙 처리 장치(210)의 레지스터에 저장된다.

- [0036] 메모리 컨트롤러(240)는 중앙 처리 장치(210)가 수행하는 프로세스와 관련된 레지스터의 값을 비휘발성 메모리 부에 저장할 수 있다. 또한 중앙 처리 장치는 레지스터의 값이 저장된 프로세스의 수행을 중지할 수 있다.

- [0037] 본 발명의 일 실시예에 따르면 메모리 컨트롤러(240)는 비휘발성 메모리부에 저장된 레지스터의 값을 중앙 처리 장치(210)로 전송할 수 있다. 또한, 중앙 처리 장치(210)는 전송된 레지스터의 값을 참조하여 프로세스를 다시수행할 수 있다.

- [0038] 본 발명의 일 실시예에 따르면 중앙 처리 장치(210)는 비휘발성 메모리부에 저장된 레지스터의 값을 그대로 중앙 처리 장치(210)의 레지스터에 저장할 수 있다. 레지스터의 값은 중앙 처리 장치(210)가 수행하였던 프로세스에 대한 상태, 과정에 대한 정보를 포함한다. 중앙 처리 장치(210)는 전송된 레지스터의 값을 참조하여 수행 중지한 프로세스를 다시 수행할 수 있다.

- [0039] 중앙 처리 장치(210)는 중단된 프로세스를 처음부터 다시 시작하지 않고 프로세스가 중단된 상태부터 다시 시작할 수 있다. 사용자의 의사에 관계없이 프로세스가 중단된 경우에, 본 발명에 따른 컴퓨터 시스템은 프로세스가 중단된 상태부터 다시 시작할 수 있다.

- [0040] 프로그램을 개발하는 경우에, 프로그램을 개발하는 단계에서는 프로그램이 정상적으로 수행되지 않을 수 있다. 많은 경우, 개발중인 프로그램은 매우 불안하며, 종종 수행이 중단된다. 본 발명에 따르면 수행이 중단되기 직전의 중앙 처리 장치(210)의 상태에 대한 정보가 비휘발성 메모리부에 저장된다. 프로그래머는 중앙 처리 장치(210)의 전원이 차단된 이후에도, 비휘발성 메모리부에 저장된 레지스터 값들에 기반하여 개발중인 프로그램에 대한 디버깅(debugging)을 수행할 수 있다.

- [0041] 중앙 처리 장치(210)가 수행하는 프로세스에 대한 정보가 비휘발성 메모리부에 저장되므로, 컴퓨터 시스템(200)은 전원이 다시 공급된 후에도 즉시 전원이 차단되기 전의 상태를 회복할 수 있다. 따라서 본 발명에 따른 컴퓨터 시스템(200)은 시스템 종료 속도 및 부팅(booting) 속도를 향상시킬 수 있다.

- [0042] 도 3은 본 발명의 일 실시예에 따라서 메모리를 할당하는 컴퓨터 시스템의 동작을 단계별로 도시한 순서도이다. 이하 도 3을 참조하여 본 발명에 따라서 메모리를 할당하는 컴퓨터 시스템의 동작을 상세히 설명하기로 한다.

- [0043] 단계(S310)에서 중앙 처리 장치는 메모리 장치에 새롭게 할당할 공간을 메모리 컨트롤러에 요청한다. 본 발명의 일 실시예에 따르면 중앙 처리 장치는 메모리 컨트롤러로 메모리 공간 요청 메시지를 전송할 수 있다.

- [0044] 단계(S320)에서 메모리 컨트롤러는 메모리 장치에 여유 공간이 있는지 여부를 판단한다. 본 발명에 따르면 메모

리 장치는 비휘발성 메모리부를 포함할 수 있으며, 메모리 장치는 비휘발성 메모리부에 여유 공간에 기반하여 메모리 장치에 여유 공간이 있는지 여부를 판단할 수 있다.

- [0045] 만약 단계(S320)에서 메모리 컨트롤러가 메모리 장치에 여유 공간이 있는 것으로 판단한 경우에 단계(S330)에서 메모리 컨트롤러는 메모리 장치에 메모리 공간을 할당할 수 있다. 본 발명의 일 실시예에 따르면 메모리 컨트롤러가 할당하는 메모리 공간은 연속된 주소를 포함하는 1개의 메모리 영역일 수도 있으나, 불연속적인 주소를 포함하는 복수의 메모리 영역일 수도 있다.

- [0046] 만약 단계(S320)에서 메모리 컨트롤러가 메모리 장치에 여유 공간이 없는 것으로 판단한 경우에, 단계(S340)에서 메모리 컨트롤러는 메모리 공간 부족 메시지를 중앙 처리 장치로 전송할 수 있다.

- [0047] 본 발명의 일 실시예에 따르면 중앙 처리 장치는 메모리 공간 부족 메시지를 수신하고, 소정의 시간 동안 대기할 수 있다. 중앙 처리 장치는 소정의 시간 이후에 다시 메모리 공간 요청 메시지를 전송할 수 있다. 중앙 처리 장치가 복수의 프로세스를 수행하는 경우에, 복수의 프로세스는 각각의 할당된 메모리 영역을 이용하여 수행될 수 있다. 각 프로세스가 종료된 이후에는 각 프로세스에 할당된 메모리 영역은 다른 프로세스가 이용할 수 있다.

- [0048] 제1 프로세스를 위하여 메모리 공간을 요청하였으나 제2 프로세스의 메모리 사용으로 인하여 메모리 공간을 할 당할 수 없는 경우에, 소정의 시간 동안 제2 프로세스가 종료되면, 제1 프로세스를 위하여 메모리 공간을 새롭게 할당할 수 있다.

- [0049] 본 발명의 일 실시예에 따르면 단계(S340)에서 중앙 처리 장치는 에러 메시지를 산출할 수 있다.

- [0050] 도 4는 본 발명의 일 실시예에 따라서 파일 할당 테이블과 페이지 테이블을 통합하여 운용하는 컴퓨터 시스템의 구조를 도시한 블록도 이다. 이하 도 4를 참조하여 본 발명에 따른 컴퓨터 시스템의 동작을 상세히 설명하기로 한다. 본 발명에 따른 컴퓨터 시스템(400)은 중앙 처리 장치(410), 가상 메모리 테이블(420), 메모리 장치(430) 및 메모리 컨트롤러(440)를 포함한다.

- [0051] 중앙 처리 장치(410)는 프로세스를 실행하고, 실행중인 프로세스와 연관된 데이터 및 파일을 식별한다. 본 발명에서의 프로세스는 제1 데이터 또는 제1 파일에 기반하여 소정의 연산을 수행하고, 연산 결과를 산출하는 것을 말한다.

- [0052] 본 발명의 일 실시예에 따르면 중앙 처리 장치(410)는 프로세스와 연관된 실행 파일, 라이브러리 파일, 데이터 파일을 이용하여 프로세스를 실행할 수 있다. 실행 파일은 중앙 처리 장치(410)가 수행할 명령어 또는 연산을 포함한다. 라이브러리 파일은 중앙 처리 장치(410)가 실행 파일에 포함된 명령어를 수행하기 위하여 참조하는 함수, 또는 서브 루틴을 포함한다. 데이터 파일은 중앙 처리 장치(410)가 실행 파일에 포함된 명령어를 수행하기 위하여 참조하는 정보를 포함한다.

- [0053] 메모리 장치(430)는 중앙 처리 장치(410)가 수행하는 프로세스와 연관된 데이터 및 파일을 저장한다.

- [0054] 가상 메모리 테이블(420)은 중앙 처리 장치(410)가 수행하는 프로세스와 연관된 데이터 및 파일의 주소값을 저장한다. 본 발명의 일 실시예에 따르면 데이터 및 파일의 주소값은 메모리 장치의 특정 주소에 대한 데이터 및 파일의 상대 주소일 수 있다.

- [0055] 본 발명의 일 실시예에 따르면 가상 메모리 테이블(420)은 파일의 주소값을 저장하는 파일 할당 테이블(460) 및 데이터의 주소값을 저장하는 페이지 테이블(470)을 포함할 수 있다.

- [0056] 메모리 컨트롤러(440)는 가상 메모리 테이블(420)에 저장된 주소값을 참조하여 메모리 장치(430)로부터 데이터 및 파일을 중앙 처리 장치로 전송한다.

- [0057] 본 발명의 일 실시예에 따르면 컴퓨터 시스템(400)은 가상 메모리 테이블(420)에 저장된 데이터 또는 파일의 주소를 참조하여 메모리 장치(430)에 저장된 데이터 또는 파일을 읽을 수 있다.

- [0058] 본 발명의 일 실시예에 따르면 컴퓨터 시스템(400)은 중앙 처리 장치(410)의 연산 결과를 메모리 장치(430)에 저장하고, 저장된 데이터의 주소를 가상 메모리 테이블(420)에 저장할 수 있다.

- [0059] 중앙 처리 장치(410)는 실행중인 프로세스와 연관된 데이터 또는 파일에 기반하여 소정의 연산 결과를 산출한다. 중앙 처리 장치(410)는 연산 결과와 관련된 연산 주소값을 생성한다.

- [0060] 가상 메모리 테이블은 중앙 처리 장치(410)가 생성한 연산 주소값을 저장한다.

- [0061] 메모리 컨트롤러(440)는 중앙 처리 장치(410)가 생성한 연산 주소값을 참조하여 연산 결과를 메모리 장치에 저장한다.

- [0062] 본 발명에 따르면 파일 할당 테이블(460)과 페이지 테이블(470)은 가상 메모리 테이블(420)내의 동일한 영역에 존재한다. 중앙 처리 장치(410)는 가상 메모리 테이블(430)을 참조하여 특정 파일 또는 테이터의 주소를 산출할 수 있다. 특정 파일 또는 데이터를 읽기 위하여 주소를 산출하는 과정이 간단해 지므로 컴퓨터 시스템(400)의 동작이 단순해 지고, 컴퓨터 시스템(400)의 성능을 향상시킬 수 있다.

- [0063] 도 5는 본 발명의 일 실시예에 따라서 가상 메모리 테이블을 참조하여 메모리 장치에 저장된 데이터를 읽는 방법을 단계별로 도시한 순서도이다. 이하 도 5를 참조하여 본 발명에 따른 데이터 읽는 방법을 상세히 설명하기로 한다.

- [0064] 단계(S510)에서 중앙 처리 장치는 프로세스를 실행하고, 실행중인 프로세스와 연관된 데이터 및 파일을 식별한다. 컴퓨터 시스템은 수 많은 데이터 또는 파일을 포함한다. 중앙 처리 장치는 수 많은 데이터 또는 파일 중에서 실행중인 프로세스와 연관된 데이터 및 파일만을 식별할 수 있다.

- [0065] 본 발명의 일 실시예에 따르면 중앙 처리 장치가 식별하는 파일들은 실행중인 프로세스와 연관된 실행 파일, 라이브러리 파일, 데이터 파일을 포함할 수 있다.

- [0066] 단계(S520)에서 메모리 컨트롤러는 가상 메모리 테이블을 참조하여 중앙 처리 장치가 식별한 파일의 주소 또는 데이터의 주소를 산출한다. 본 발명의 일 실시예에 따르면 가상 메모리 테이블은 파일의 주소를 저장하는 파일 할당 테이블 또는 데이터의 주소를 저장하는 페이지 테이블을 포함할 수 있다.

- [0067] 단계(S530)에서 메모리 컨트롤러는 중앙 처리 장치가 식별한 파일의 주소 또는 데이터의 주소를 참조하여 메모리 장치에 저장된 파일 또는 데이터를 중앙 처리 장치로 전송한다.

- [0068] 도 6은 본 발명의 일 실시예에 따라서 가상 메모리 테이블을 참조하여 중앙 처리 장치의 연산 결과를 메모리 장치에 저장하는 방법을 단계별로 도시한 순서도이다. 이하 도 6를 참조하여 본 발명에 따른 데이터 저장 방법을 상세히 설명하기로 한다.

- [0069] 단계(S610)에서 중앙 처리 장치는 메모리 장치에 저장된 데이터 또는 파일에 기반하여 연산 결과를 산출한다. 본 발명의 일 실시예에 따르면 메모리 장치는 비휘발성 메모리부를 포함하고, 데이터 또는 파일은 비휘발성 메 모리에 저장될 수 있다.

- [0070] 본 발명의 일 실시예에 따르면 메모리 장치는 휘발성 메모리부를 포함할 수 있다. 일반적으로 휘발성 메모리는 비휘발성 메모리에 비하여 동작 속도가 더 빠르다. 본 발명의 일 실시예에 따르면 메모리 장치는 비휘발성 메모리부에 저장된 데이터 또는 파일을 휘발성 메모리부에 저장할 수 있다. 중앙 처리 장치는 휘발성 메모리부에 저장된 데이터 또는 파일에 기반하여 연산 결과를 산출할 수 있다. 동작 속도가 더 빠른 휘발성 메모리부에 저장된 파일 또는 데이터에 기반하여 중앙 처리 장치가 연산 결과를 산출하므로 컴퓨터 시스템의 성능이 향상된다.

- [0071] 단계(S620)에서 중앙 처리 장치는 연산 결과와 관련된 연산 주소값을 생성한다. 본 발명의 일 실시예에 따르면 연산 주소값은 메모리 장치 내부에서 연산 결과가 저장된 위치에 대한 정보를 포함할 수 있다.

- [0072] 단계(S630)에서 가상 메모리 테이블은 연산 주소값을 저장한다. 본 발명의 일 실시예에 따르면 가상 메모리 테이블은 파일의 주소값을 저장하는 파일 할당 테이블 및 데이터의 주소값을 저장하는 페이지 테이블을 포함할 수 있다.

- [0073] 단계(S640)에서 메모리 컨트롤러는 연산 주소값을 참조하여 연산 결과를 메모리 장치에 저장한다. 본 발명의 일 실시예에 따르면 메모리 컨트롤러는 가상 메모리 테이블에 저장된 연산 주소값을 참조하고, 메모리 장치의 연산 주소값에 상응하는 위치에 다른 데이터가 저장되었는지 여부를 판단할 수 있다.

- [0074] 본 발명의 일 실시예에 따르면 메모리 장치의 연산 주소값에 상응하는 위치에 다른 데이터가 저장된 경우에, 메모리 컨트롤러는 중앙 처리 장치가 상기 연산 주소값을 다시 생성하도록 제어 신호를 중앙 처리 장치로 전송할수 있다.

- [0075] 도 7은 본 발명의 일 실시예에 따라서 메모리 장치에 저장된 프로그램 파일을 실행하는 방법을 단계별로 도시한 순서도이다. 이하 도 7을 참조하여 본 발명에 따라서 메모리 장치에 저장된 프로그램 파일을 실행하는 방법을 상세히 설명하기로 한다.

- [0076] 단계(S710)에서는 본 발명에 따른 컴퓨터 시스템은 실행 파일의 위치를 검색한다. 본 발명에 따르면 실행 파일은 메모리 장치의 특정 영역에 저장된다. 종래의 기술에 따르면 실행 파일은 컴퓨터 시스템내의 보조 기억 장치에 저장되고, 단계(S710)에서는 보조 기억 장치상의 특정한 영역에 대한 정보를 검색한다. 그러나 본 발명에 따르면 실행 파일이 저장된 메모리 장치는 중앙 처리 장치에 직접 연결된다. 본 발명에 따르면 단계(S710)에서는 실행파일이 저장된 메모리 장치의 특정한 영역의 위치를 검색한다.

- [0077] 단계(S720)에서 본 발명에 따른 컴퓨터 시스템은 실행 파일의 메모리 주소를 반환한다. 본 발명에 따르면 중앙 처리 장치는 실행 파일이 저장된 메모리 장치상의 메모리 주소 값을 획득한다. 본 발명에 따르면 실행 파일이 저장된 메모리 장치는 중앙 처리장치에 직접 연결되고, 실행 파일은 메모리 장치상에서 실행될 수 있다.

- [0078] 종래의 기술에 따르면 단계(S720)에서 실행 파일은 보조 저장 장치로부터 주 기억 장치로 복사된다. 중앙 처리 장치는 주 기억 장치 상의 실행 파일의 메모리 주소 값을 획득한다.

- [0079] 단계(S730)에서 본 발명에 따른 컴퓨터 시스템은 가상 메모리 주소를 부여한다. 가상 메모리 주소는 단계(S72 0)에서 획득한 메모리 주소에 대응된다.

- [0080] 단계(S740)에서 본 발명에 따른 컴퓨터 시스템은 실행 파일의 엔트리 포인트를 반환한다. 본 발명의 일 실시예 에 따르면 엔트리 포인트는 실행 파일에서 프로그램 코드가 시작되는 위치일 수 있다.

- [0081] 단계(S750)에서 본 발명에 따른 컴퓨터 시스템은 엔트리 포인트부터 프로그램을 실행한다.

- [0082] 본 발명에 따르면, 실행 파일이 저장된 메모리 장치는 중앙 처리 장치와 직접 연결된다. 또한 실행 파일은 메모리 장치에 저장된 상태에서 실행될 수 있다. 따라서 주 기억 장치와 보조 기억 장치를 구별할 실익이 없다.

- [0083] 반면, 종래 기술에 따르면 보조 기억 장치에 저장된 실행 파일은 주 기억 장치로 복사된다. 주 기억 장치에 복사된 실행 파일은 실행된다. 따라서 주 기억 장치와 보조 기억 장치는 명확하게 구분된다.

- [0084] 본 발명에 따르면 보조 기억 장치에 저장된 실행 파일을 주 기억 장치로 복사할 필요가 없으므로 프로그램 수행 과정이 간단해진다.

- [0085] 도 8은 본 발명의 일 실시예에 따라서 메모리 장치에 저장된 데이터 파일을 사용하는 방법을 단계별로 도시한 순서도이다. 이하 도 8을 참조하여 본 발명에 따라서 메모리 장치에 저장된 데이터 파일을 사용하는 방법을 상세히 설명하기로 한다. 도 7에서는 본 발명에 따른 컴퓨터 시스템이 메모리 장치에 저장된 실행 파일을 실행하는 실시예가 도시되었으나 도 8에서는 본 발명에 따른 컴퓨터 시스템이 데이터가 저장된 데이터 파일을 로드하는 실시예가 설명된다.

- [0086] 단계(S810)에서 본 발명에 따른 컴퓨터 시스템은 파일내의 데이터를 요청한다. 본 발명에 따르면 데이터 파일은 중앙 처리 장치에 직접 연결된 메모리 장치에 저장될 수 있다. 종래 기술에 따르면 데이터 파일은 보조 기억 장치에 저장 된다.

- [0087] 단계(S820)에서 본 발명에 따른 컴퓨터 시스템은 데이터 파일의 위치를 검색한다. 본 발명에 따르면 컴퓨터 시스템은 단계(S810)에서 요청 받은 데이터 파일의 위치를 메모리 장치에서 검색할 수 있다.

- [0088] 종래의 기술에 따르면 컴퓨터 시스템은 보조 기억 장치에 저장된 데이터 파일의 위치를 검색한다. 종래의 기술에 따르면 컴퓨터 시스템은 보조 기억 장치에 저장된 데이터 파일을 복사하기 위하여 주 기억 장치에 메모리 공간을 확보하는 절차를 추가적으로 수행한다.

- [0089] 단계(S830)에서 본 발명에 따른 컴퓨터 시스템은 메모리 장치상에서 데이터 파일의 메모리 주소를 반환한다. 중 앙 처리 장치는 데이터 파일의 메모리 주소를 획득한다. 본 발명에 따르면 데이터 파일은 메모리 장치에 저장된 상태에서 중앙 처리 장치에 의하여 이용될 수 있다.

- [0090] 종래의 기술에 따르면 보조 기억 장치에 저장된 파일은 데이터 파일은 주 기억 장치로 복사된다. 중앙 처리 장치는 주 기억 장치에서 데이터 파일의 메모리 주소를 획득한다.

- [0091] 단계(S840)에서 본 발명에 따른 중앙 처리 장치는 메모리 장치에서 데이터 파일의 주소에 기반하여 데이터 파일을 이용한다. 종래의 기술에 따르면 중앙 처리 장치는 주 기억 장치에 복사된 데이터 파일의 주소에 기반하여 주 기억 장치에 복사된 데이터 파일을 이용한다.

- [0092] 본 발명에 따르면 메모리 장치에 저장된 데이터 파일을 중앙 처리 장치가 직접 이용한다. 따라서 중앙 처리 장치는 메모리 장치에 저장된 데이터 파일을 수정할 수도 있다. 본 발명의 일 실시예에 따르면 중앙 처리 장치가

복수의 프로세스를 수행하고, 복수의 프로세스 각각은 동일한 데이터 파일을 이용할 수 있다. 본 발명의 일 실 시예에 따르면 복수의 프로세스 각각은 동일한 데이터 파일의 서로 다른 부분을 개별적으로 수정할 수 있다. 또 는 특정 프로세스가 데이터 파일을 수행하면 프로세스 수행전과 수행후의 데이터 파일의 내용은 달라진다.

- [0093] 이러만 문제점을 해결하기 위하여 본 발명에 따른 컴퓨터 시스템은 주소 매팅 기법을 사용할 수 있다. 본 발명의 일 실시예에 따르면 데이터를 기록한 페이지에 새로운 데이터를 기록하기 위해서는 바로 덮어쓸 수 없고, 지우기 동작을 수행한 후에만 가능할 수 있다. 이 동작을 수행하기 위하여 컴퓨터 시스템은 주소 변환 레이어 (Flash Translation Layer)를 이용할 수 있다.

- [0094] 예를 들어 본 발명에 따른 컴퓨터 시스템의 메모리 주소상의 100번지가 메모리 장치의 300번째 번지에 매핑이되어 있는 경우를 가정하자. 중앙 처리 장치가 메모리 주소상의 100번지에 저장된 데이터를 요청하면 주소 변환 레이어는 메모리 주소상의 100번지에 대응하는 메모리 장치의 300번지를 반환한다. 본 발명의 일 실시예에 따르면 주소 변환 레이어는 주소 변환 테이블을 이용하여 메모리 주소와 메모리 장치의 주소를 변환할 수 있다. 중앙 처리 장치는 메모리 장치의 300번지를 획득하고, 메모리 장치의 300번지에 저장된 데이터를 수신한다.

- [0095] 본 발명의 일 실시예에 따르면 중앙 처리 장치가 메모리 주소상의 100번지에 대한 데이터 수정이 필요한 경우에, 주소 변환 레이어는 메모리 장치의 301번지를 메모리 주소상의 100번지에 매칭시킬 수 있다. 중앙 처리 장치는 메모리 장치의 301번지에 수정된 데이터를 저장할 수 있다.

- [0096] 본 발명에 따르면 메모리 장치에 저장된 데이터의 수정이 필요한 경우에 메모리 장치상의 새로운 메모리 공간에 수정된 데이터를 저장한다. 원본 데이터는 삭제되지 않고 메모리 장치상에 여전히 저장된다. 즉, 원본 파일과, 수정된 파일이 모두 메모리 장치에 유지된다.

- [0097] 본 발명의 일 실시예에 따르면 중앙 처리 장치가 데이터 파일을 사용한 후, 원본 파일 자체에 대한 수정이 필요하지 않은 경우에는 주소 변환 레이어는 메모리 주소상의 데이터 번지를 메모리 장치에 저장된 원본 데이터의 주소로 복원할 수 있다.

- [0098] 중앙 처리 장치에 의하여 메모리 장치에 저장된 데이터가 변환되지만, 중앙 처리 장치가 데이터를 사용한 이후에, 실제로 데이터의 변환이 필요한지 판단하고, 판단 결과에 따라서 원본 데이터를 복원할 수 있다. 따라서, 중앙 처리 장치의 데이터 변환에도 불구하고 원본 데이터가 유지될 수 있다.

- [0099] 이상과 같이 본 발명은 비록 한정된 실시예와 도면에 의해 설명되었으나, 본 발명은 상기의 실시예에 한정되는 것은 아니며, 본 발명이 속하는 분야에서 통상의 지식을 가진 자라면 이러한 기재로부터 다양한 수정 및 변형이 가능하다.

- [0100] 그러므로, 본 발명의 범위는 설명된 실시예에 국한되어 정해져서는 아니 되며, 후술하는 특허청구범위뿐 아니라 이 특허청구범위와 균등한 것들에 의해 정해져야 한다.

#### 부호의 설명

[0101] 110: 중앙처리장치

120: 메모리 장치

130: 입출력 장치

160: 메모리 컨트롤러